# Carry Chain Adder (1A)

- - •

Copyright (c) 2010 -- 2020 Young W. Lim.

Permission is granted to copy, distribute and/or modify this document under the terms of the GNU Free Documentation License, Version 1.2 or any later version published by the Free Software Foundation; with no Invariant Sections, no Front-Cover Texts, and no Back-Cover Texts. A copy of the license is included in the section entitled "GNU Free Documentation License".

Please send corrections (or suggestions) to youngwlim@hotmail.com.

This document was produced by using OpenOffice and Octave.

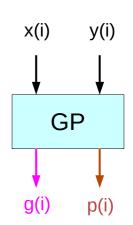

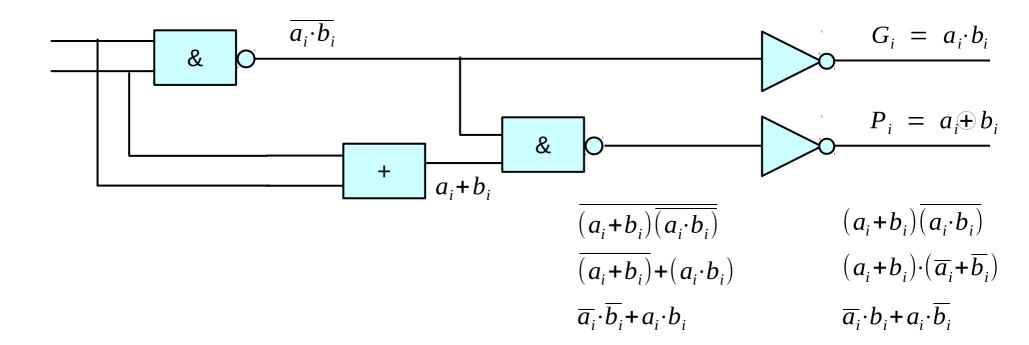

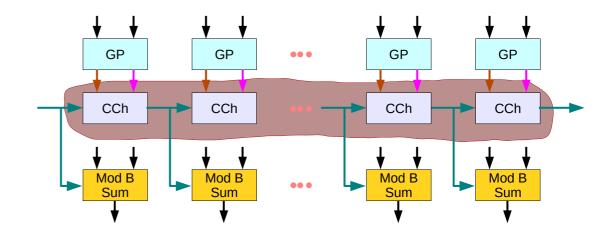

**GP** Cell

| Generate  | $G_i = a_i \cdot b_i$ |

|-----------|-----------------------|

| Propagate | $P_i = a_i + b_i$     |

| Generate | g(i) = 1 | lf x(i) + y(i) > (B − 1) |

|----------|----------|--------------------------|

|          | 0        | otherwise                |

| Propagate | p(i) = 1 | If $x(i) + y(i) = (B - 1)$ |

|-----------|----------|----------------------------|

|           | 0        | otherwise                  |

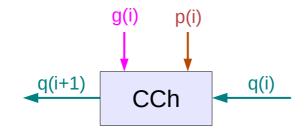

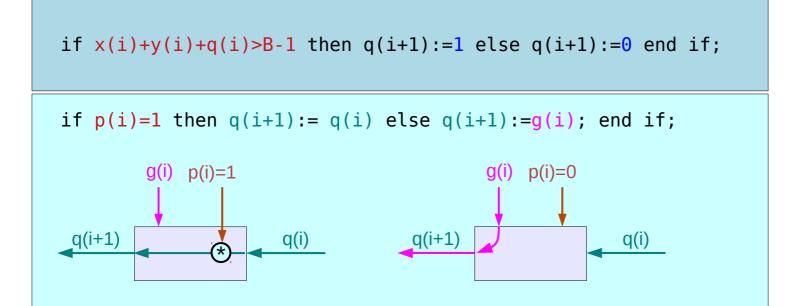

## Carry Chain Cell (1)

q(i+1), q(i) : 1-bit number

$$c_{out} = G_i + P_i c_i$$

| q(i+1) | = q(i) | when <mark>p(i)</mark> = 1 | Propagate |

|--------|--------|----------------------------|-----------|

|        | = g(i) | otherwise                  | Generate  |

Synthesis of Arithmetic Circuits: FPGA, ASIC and Ebedded Systems, J-P Deschamps et al

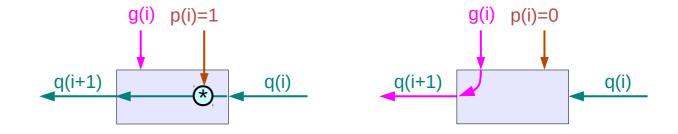

### Carry Chain Cell (2)

| q(i+1) | = q(i) | when <mark>p(i)</mark> = 1 | Propagate |

|--------|--------|----------------------------|-----------|

|        | = g(i) | otherwise                  | Generate  |

Synthesis of Arithmetic Circuits: FPGA, ASIC and Ebedded Systems, J-P Deschamps et al

$$c_{out} = G_i + P_i c_i$$

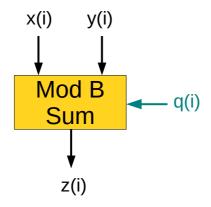

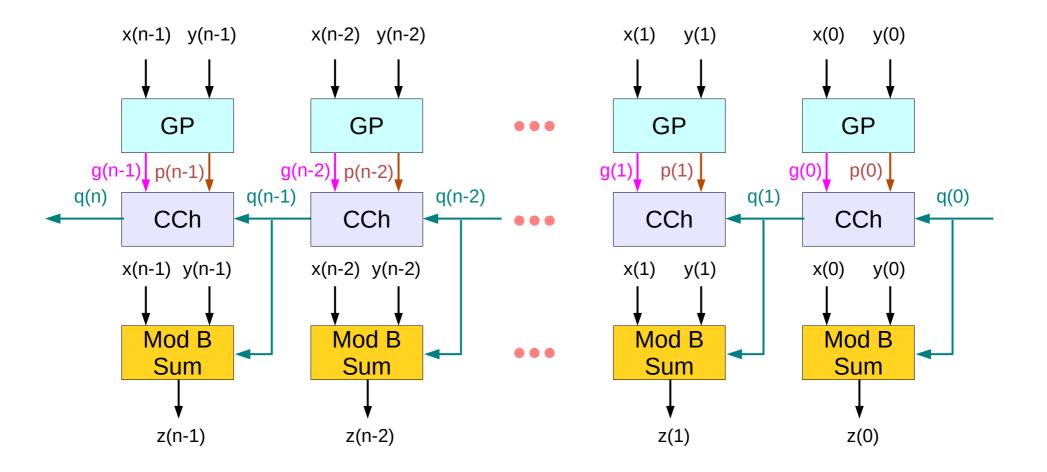

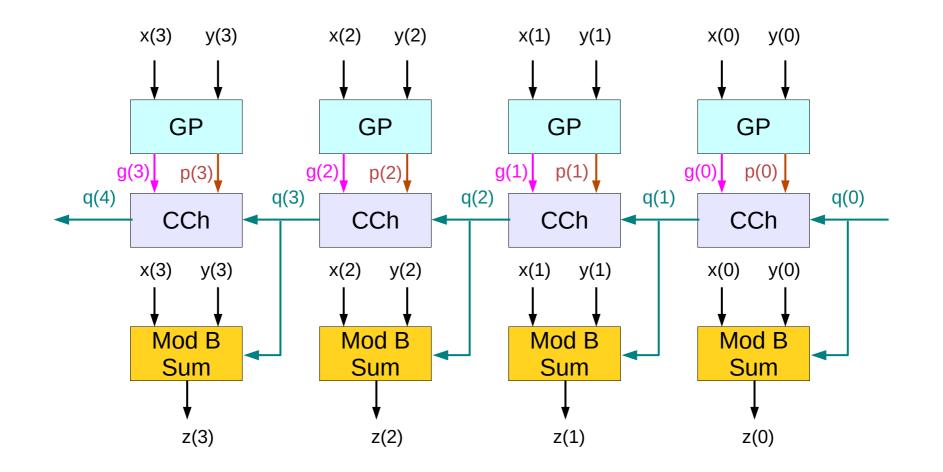

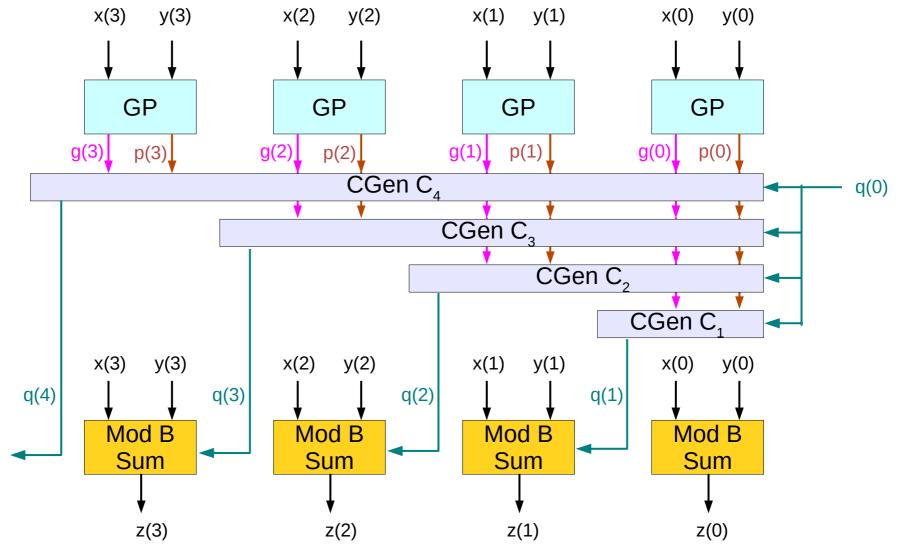

#### **Carry Chain Adder**

5

$$z(i) = (x(i) + y(i) + q(i)) \mod B$$

Synthesis of Arithmetic Circuits: FPGA, ASIC and Ebedded Systems, J-P Deschamps et al

### **Carry Chain Adder**

6

### 4-ary Carry Chain Addition Example

| Generate                             | e g(i                         | ) = 1<br>0     | lf x(i) + y<br>otherwis      |                       |  |

|--------------------------------------|-------------------------------|----------------|------------------------------|-----------------------|--|

| Propagat                             | e p(i                         | ) = 1<br>0     | lf x(i) + y<br>otherwis      |                       |  |

| q(i+1)                               | = q(i)<br>= <mark>g(i)</mark> | when<br>otherw | <mark>p(i)</mark> = 1<br>ise | Propagate<br>Generate |  |

| $z(i) = (x(i) + y(i) + q(i)) \mod 4$ |                               |                |                              |                       |  |

|                          | 0           | 1                | 2                     | 3                |  |

|--------------------------|-------------|------------------|-----------------------|------------------|--|

| 0                        | 0           |                  | 2<br>2<br>3<br>4<br>5 | 3                |  |

| 0<br>1<br>2<br>3         | 1           | 1<br>2<br>3<br>4 | 3                     | 3<br>4<br>5<br>6 |  |

| 2                        | 1<br>2<br>3 | 3                | 4                     | 5                |  |

| 3                        | 3           | 4                | 5                     | 6                |  |

|                          |             |                  |                       |                  |  |

| p(i)<br>0<br>1<br>2<br>3 | 0           | 1                | 2                     | 3                |  |

| 0                        | 0           | 0                | 0                     |                  |  |

| 1                        | 0<br>0<br>0 | 0                | 1                     | 1<br>0<br>0<br>0 |  |

| 2                        | 0           | 1<br>0           | 1<br>0<br>0           | 0                |  |

| 3                        | 1           | 0                | 0                     | 0                |  |

|                          |             |                  |                       |                  |  |

| <b>g(i)</b>              | 0           | 1                | 2                     | 3                |  |

| 0                        | 0           | 0                | 2<br>0                | 0                |  |

| 1                        | 0           | 0                | 0                     | 1                |  |

| 0<br>1<br>2<br>3         | 0<br>0<br>0 | 0                | 1<br>1                | 0<br>1<br>1<br>1 |  |

| 3                        | 0           | 1                | 1                     | 1                |  |

Synthesis of Arithmetic Circuits: FPGA, ASIC and Ebedded Systems, J-P Deschamps et al

## Carry Chain Adder

```

-- computation of the generation and propagation conditions

for i in 0...-1 loop

q(i) := q(x(i), y(i));

p(i) := p(x(i), y(i));

end loop

-- carry computation

q(0) := c in;

for i in 0..n-1 loop

if p(i)=1 then q(i+1):=q(i); else q(i+1):=g(i); end if;

end loop

-- sum computation

for i in 0..n-1 loop

z(i) := (x(i)+y(i)+q(i)) \mod B

end loop;

z(n) := q(n);

```

```

the first iteraton includes 2.n B-ary operations

computation of g(i) and p(i) that could be executed in <u>parallel</u>

g(i) := g(x(i), y(i));

p(i) := p(x(i), y(i));

```

```

The second iteration is made up of n iteration steps

that must be used executed <u>sequentially</u>

as q(i+1) is a function of q(i)

consists of binary operation only

if p(i)=1 then q(i+1):=q(i); else q(i+1):=g(i); end if;

```

```

the last iteration includes n B-ary operations

computation of z(i) that could be executed in <u>parallel</u>

z(i) := (x(i)+y(i)+q(i)) \mod B

```

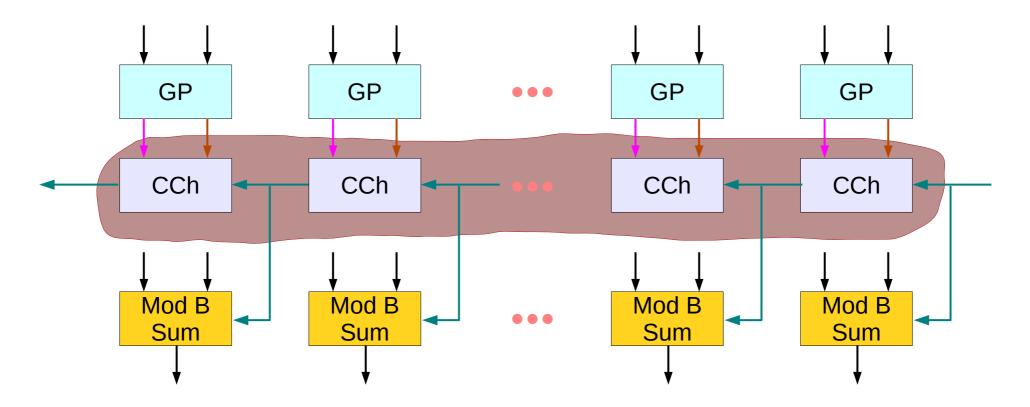

### Sequential and concurrent computations

Splits the operations into **concurrent B-ary** ones (1<sup>st</sup> and 3<sup>rd</sup> iterations) And **sequential binary** ones (2<sup>nd</sup> iterations)

```

q(0) <= c_in;

iterative_step for i in 0 to n-1 generate

p(i) <= '1' when x(i)+y(i) = B-1 else '0';

g(i) <= '1' when x(i)+y(i) > B-1 else '0';

with p(i) select q(i+1) <= q(i) when '1', g(i) when others;

z(i) <= (x(i)+y(i)+ conv_integer(q(i))) mod B;

end generate;

```

```

c_out <= q(n);</pre>

```

The sequential binary operations are the same whatever base B is

However, the expected computation time can be <u>reduced</u> by the <u>substitution</u> of the relatively complex instruction

Synthesis of Arithmetic Circuits: FPGA, ASIC and Ebedded Systems, J-P Deschamps et al

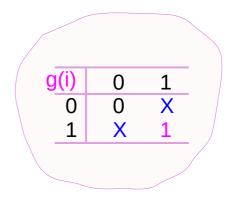

# Relaxing g(i)

if p(i)=1 then q(i+1):=q(i) else q(i+1):=g(i); end if;

the corresponding Boolean equation

$q(i+1) = p(i).q(i) \vee not(p(i)).g(i)$

the generate function g(a,b) can be relaxed as bellows

| g(a,b) = 1             | if $a + b > B-1 \dots$ when $p(i) = 0 \dots not(p(i))=1$ |

|------------------------|----------------------------------------------------------|

| g(a,b) = 0             | if $a + b < B-1 \dots$ when $p(i) = 0 \dots not(p(i))=1$ |

| g(a,b) = 1/0 dont care | if $a + b = B-1 \dots$ when $p(i) = 1 \dots not(p(i))=0$ |

the original generate and propagate function

| g(a,b) = 1 | if a + b > B-1, |

|------------|-----------------|

| g(a,b) = 0 | otherwise       |

| p(a,b) = 1 | if a + b = B-1, |

| p(a,b) = 0 | otherwise       |

Synthesis of Arithmetic Circuits: FPGA, ASIC and Ebedded Systems, J-P Deschamps et al

## Relaxed g(i) Examples

| 0<br>1<br>2 | 0<br>0<br>1<br>2 | 1<br>1<br>2<br>3 | 2<br>2<br>3<br>4 | 3<br>3<br>4<br>5 | - | 0<br>1<br>2 | 0<br>0<br>1<br>2 | 1<br>1<br>2<br>3 | 2<br>2<br>3<br>4 | 3<br>3<br>4<br>5 | $\begin{array}{c ccc} 0 & 1 \\ 0 & 0 & 1 \\ 1 & 1 & 2 \end{array}$ |

|-------------|------------------|------------------|------------------|------------------|---|-------------|------------------|------------------|------------------|------------------|--------------------------------------------------------------------|

| 3           | 3                | 4                | 5                | 6                | _ | 3           | 3                | 4                | 5                | 6                | _                                                                  |

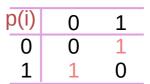

| p(i)        | 0                | 1                | 2                | 3                |   | p(i)        | 0                | 1                | 2                | 3                | p(i) 0 1                                                           |

| 0           | 0                | 0                | 0                | 1                | - | 0           | 0                | 0                | 0                | 1                | 0 0 1                                                              |

| 1           | 0                | 0                | 1                | 0                |   | 1           | 0                | 0                | 1                | 0                | 1 1 0                                                              |

| 2           | 0                | 1                | 0                | 0                |   | 2           | 0                | 1                | 0                | 0                |                                                                    |

| 3           | 1                | 0                | 0                | 0                | _ | 3           | 1                | 0                | 0                | 0                | _                                                                  |

|             |                  |                  |                  |                  |   |             |                  |                  |                  |                  |                                                                    |

| g(i)        | 0                | 1                | 2                | 3                | ( | g(i)        | 0                | 1                | 2                | 3                | g(i) 0 1                                                           |

| 0           | 0                | 0                | 0                | 0                | - | 0           | 0                | 0                | 0                | Х                | 0 0 X                                                              |

| 1           | 0                | 0                | 0                | 1                |   | 1           | 0                | 0                | Х                | 1                | 1 X 1                                                              |

| 2           | 0                | 0                | 1                | 1                |   | 2           | 0                | Х                | 1                | 1                |                                                                    |

| 3           | 0                | 1                | 1                | 1                | - | 3           | Х                | 1                | 1                | 1                | _                                                                  |

| Ori         | ginal            | g(i) :           | 4-ary            | /                |   | Rel         | axed             | g(i) :           | 4-ar             | у                | Relaxed g(i) : binary                                              |

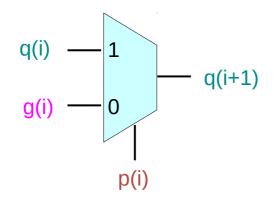

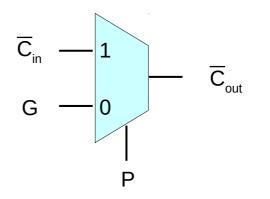

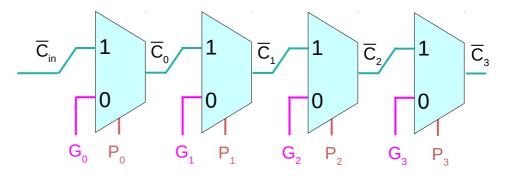

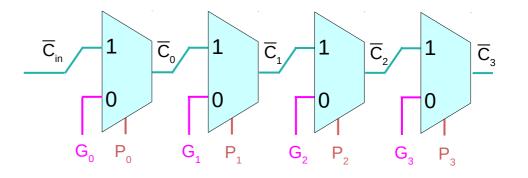

### **Multiplexer Carry Chain**

if p(i)=1 then q(i+1):=q(i) else q(i+1):=g(i); end if;

#### $q(i+1) = p(i).q(i) \vee not(p(i)).g(i)$

|   | 0 | 1 |

|---|---|---|

| 0 | 0 | 1 |

| 1 | 1 | 2 |

Synthesis of Arithmetic Circuits: FPGA, ASIC and Ebedded Systems, J-P Deschamps et al

#### **Carry Chain Adder**

16

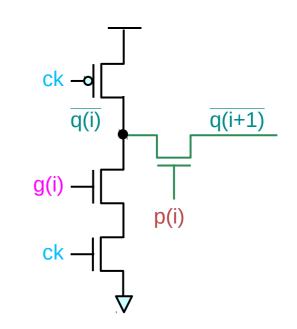

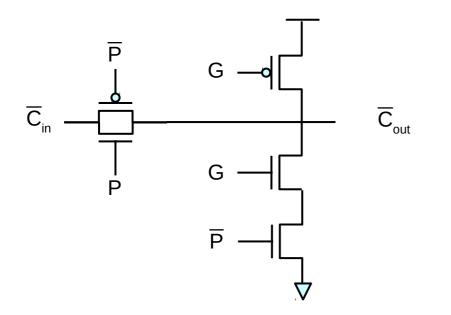

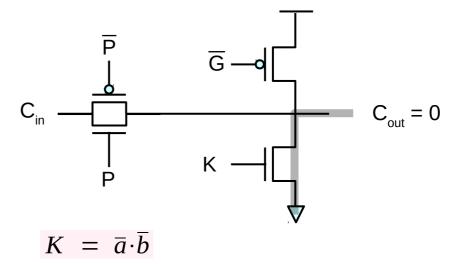

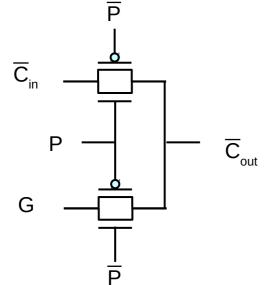

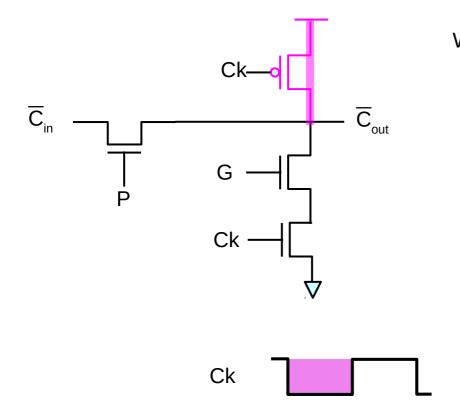

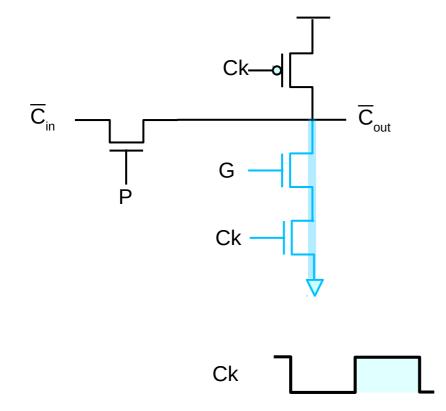

## Manchester Carry Chain

```

the output node \overline{q(i+1)} is precharged,

when the synchronization signal is equal to 0 (ck=0),

```

```

when ck=1, the output node is discharged

if either p(i) = 1 and the preceding node \overline{q(i)}

has been discharged, or

if g(i)=1.

```

In order that it works properly g(i) and p(i) should <u>not</u> be equal to 1 simultaneously so that the definition of g(i) <u>cannot</u> be <u>relaxed</u> as in the preceding case

| p(i) | 0 | 1 | <b>g(i)</b> | 0 | 1 |

|------|---|---|-------------|---|---|

| 0    | 0 | 1 | 0           | 0 | 0 |

| 1    | 1 | 0 | 1           | 0 | 1 |

#### **Manchester Carry Chain**

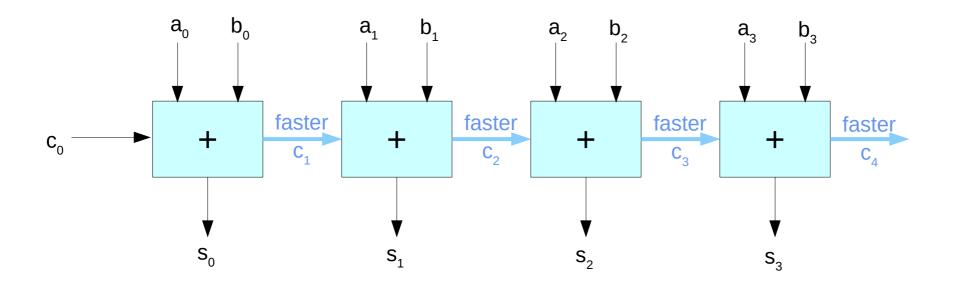

Bottle neck : any stage needs information regarding all preceding carry bits to be able to compute its own sum and carry-out bits

#### **Faster Adders**

- 1) **faster carry <u>propagation</u>** Manchester Carry Chain Adder reduction of the time required for the carry signal to propagate to the cell

- 2) **faster carry generation** Carry Lookahead Adder local computation of the carry, without having to wait for the carry-out produced by preceding stages

Principles of CMOS VLSI design – A Systems Perspective, N Weste, K Eshraghian

### **Faster Carry Propagation**

Reduces the time needed for the carry to propagate through the cells

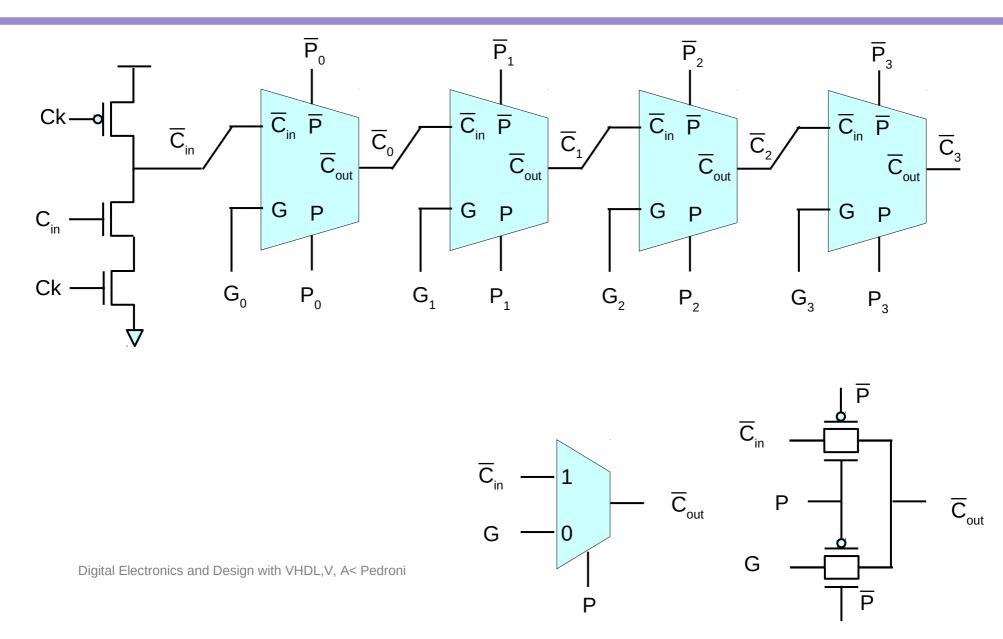

Digital Electronics and Design with VHDL,V, A< Pedroni

### **Faster Carry Generation**

20

Each stage computes its own carry-in bit

Digital Electronics and Design with VHDL, V, A< Pedroni

### Manchester Carry-Chain Adder

Manchester Carry-Chain Adder

--- faster carry propagation carry propagate adder in which the delay through the carry cells is reduced

Static or Dynamic Circuits

Thanks to the parameter G and P, The delay is just one gate-delay

Principles of CMOS VLSI design – A Systems Perspective, N Weste, K Eshraghian

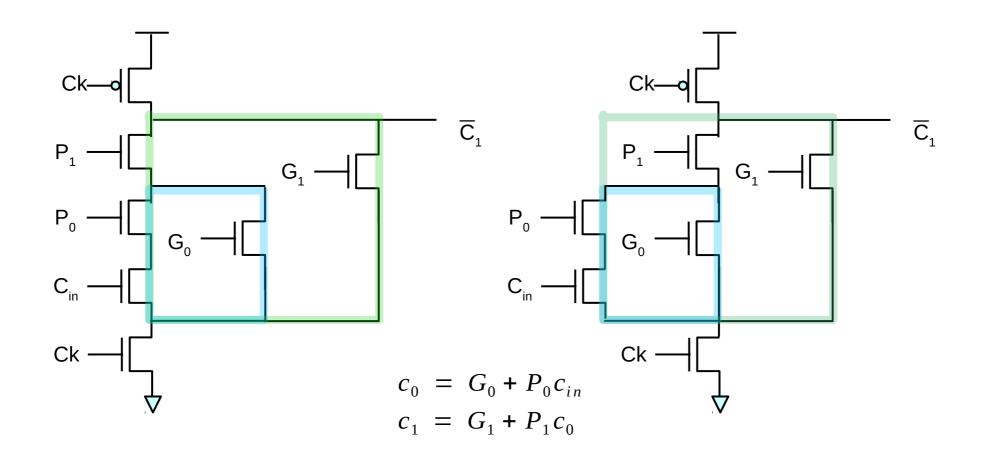

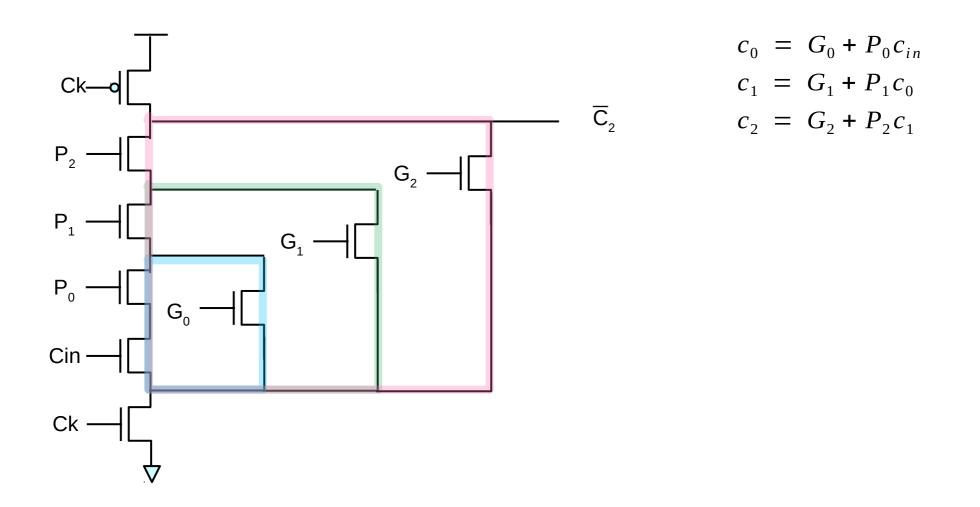

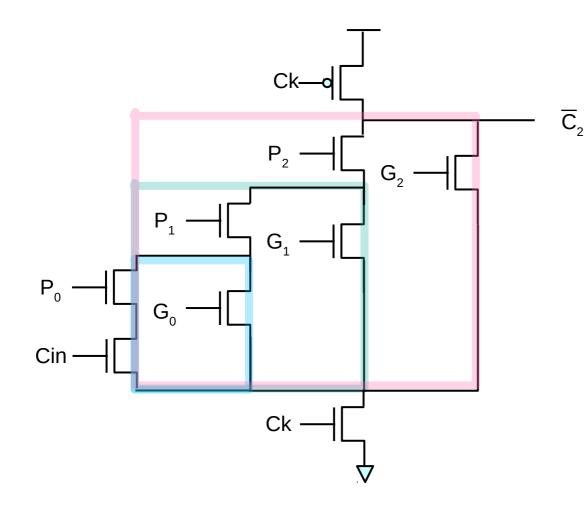

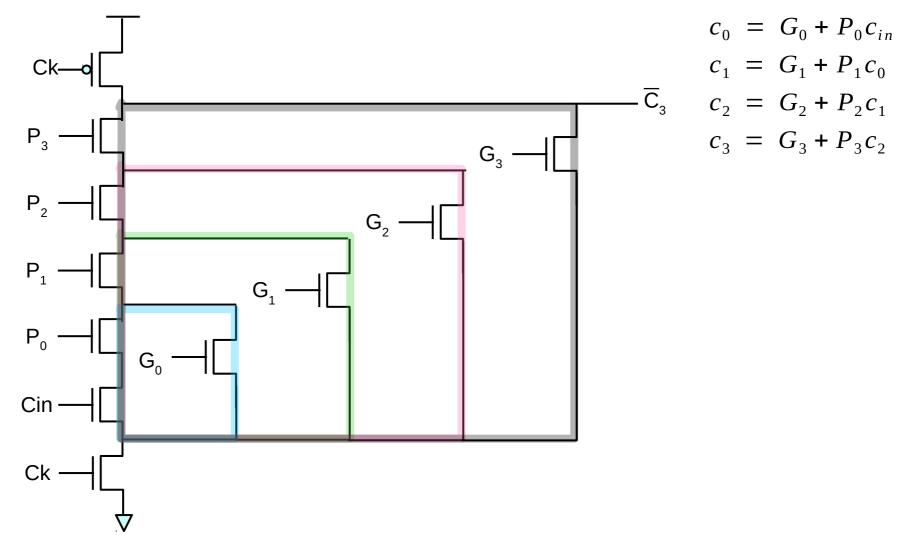

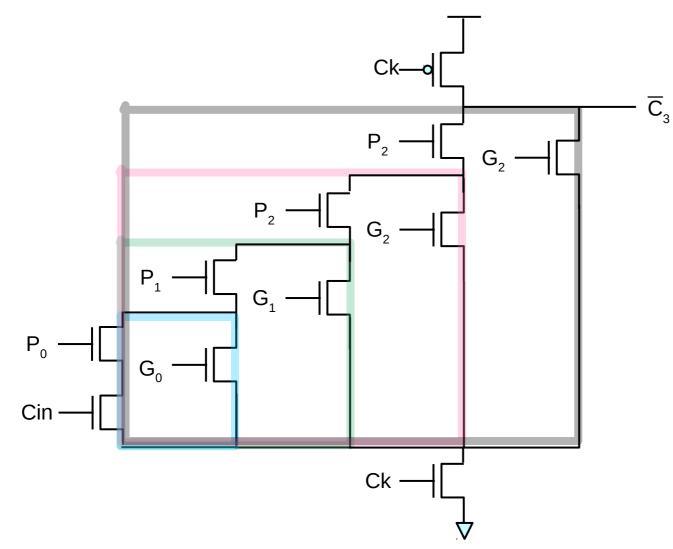

### Manchester Carry Chain – Shared Logic

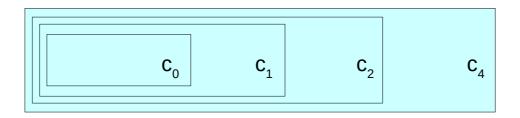

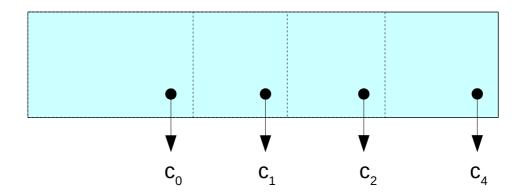

The **Manchester carry chain** is a variation of the **carry-lookahead adder** that uses **shared logic** to lower the transistor count.

the logic for **generating** each carry contains all of the logic used to **generate the previous carries**.

A Manchester carry chain generates the **intermediate carries** by tapping off nodes in the gate that calculates the **most significant carry value**.

https://en.wikipedia.org/wiki/Carry-lookahead\_adder

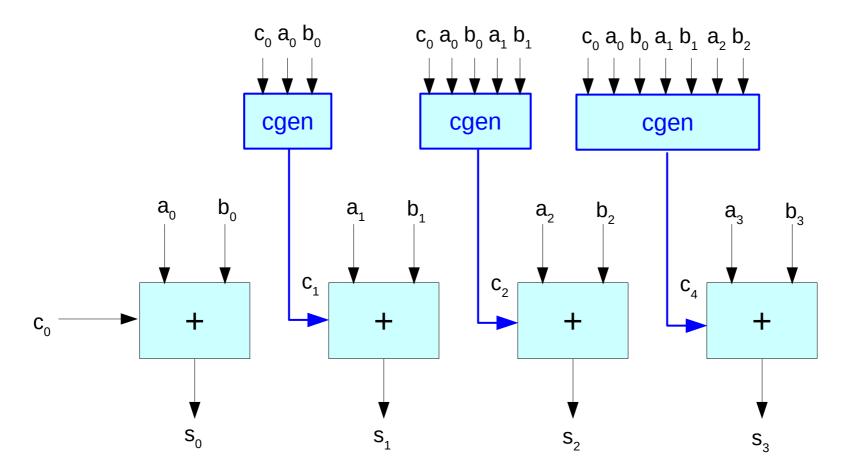

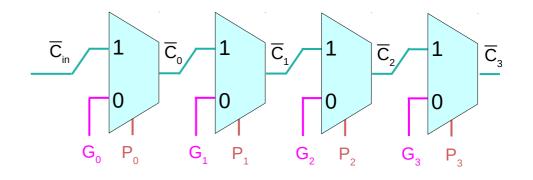

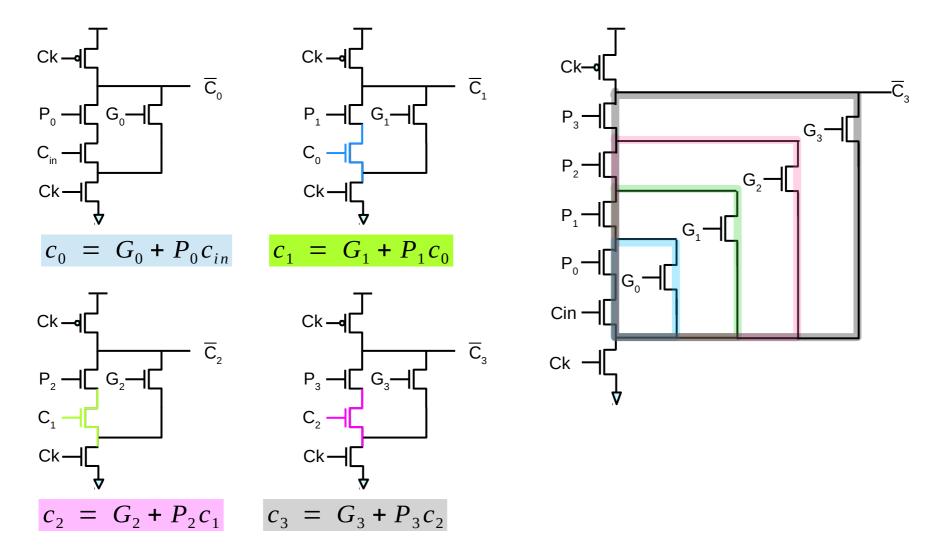

### Manchester Carry Chain – tap to internal nodes

The Manchester adder stage improves on the carry-lookahead implementation by using a single  $C_3$  circuit

$C_2$ ,  $C_1$ ,  $C_0$ , are tapped to the internal nodes of the single  $C_3$  circuit

Principles of CMOS VLSI design – A Systems Perspective, N Weste, K Eshraghian

In addition to four Manchester stages, the adder requires four PG generator blocks One representative implementation

Four SUM generate blocks an XNOR gate complete the adder This worst case propagation time can be improved by bypassing the four stages if all carry propagate signals are true

The optimum number of cascaded stages may be calculated for a given technology by simulation A final implementation of a 4-bit Manchester adder

Principles of CMOS VLSI design – A Systems Perspective, N Weste, K Eshraghian

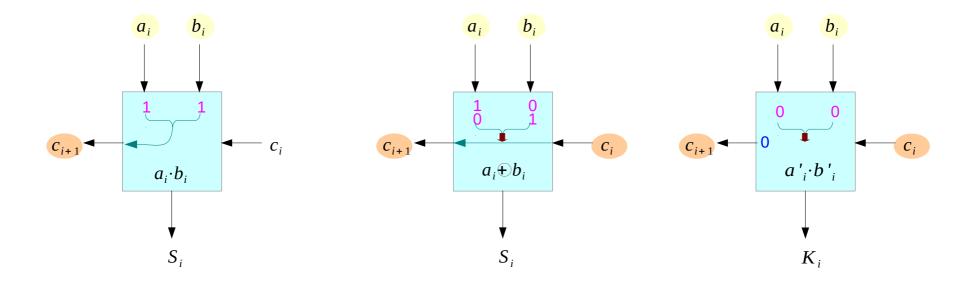

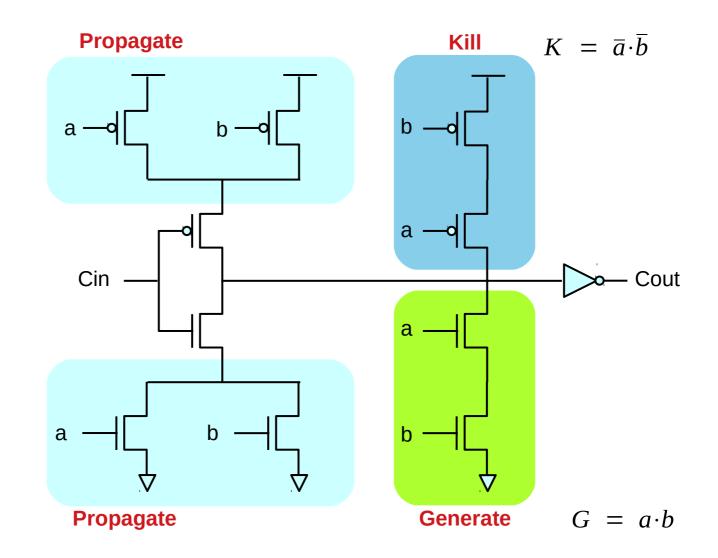

### G, P, and K

Generate

$$G_i = a_i \cdot b_i$$

Propagate $P_i = a_i + b_i$ Kill $K_i = \bar{a}_i \cdot \bar{b}_i$

$$c_{out} = G_i + P_i c_i$$

### **PG** Circuits

**Generate**  $G_i = a_i \cdot b_i$

**Propagate**  $P_i = a_i \oplus b_i$

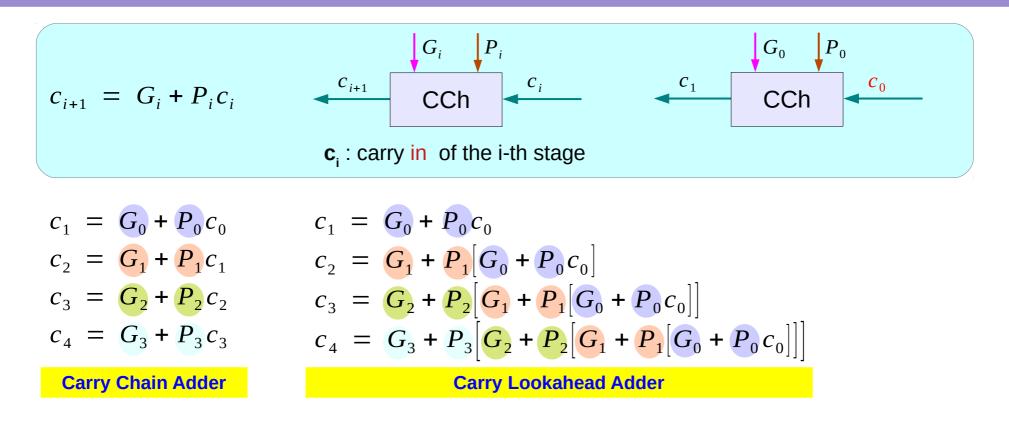

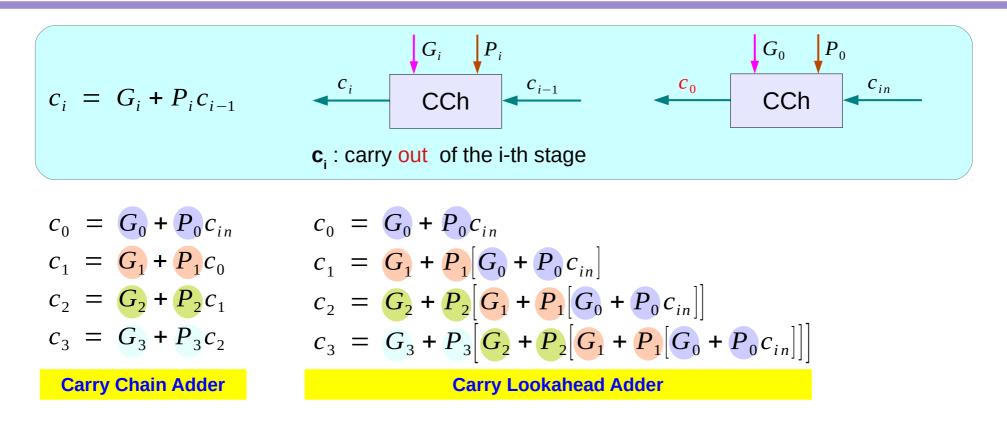

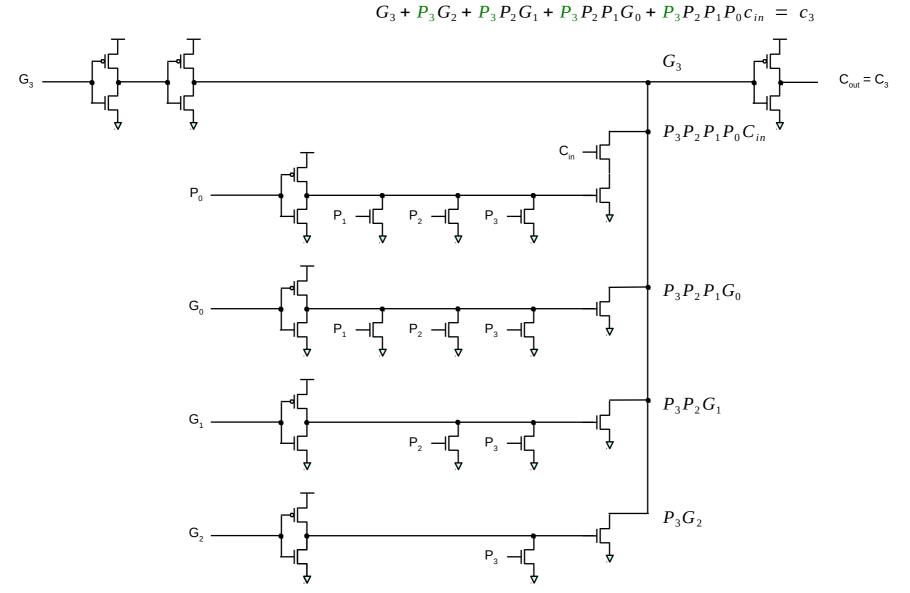

### Carry Equations (1)

$$G_{0} + P_{0}c_{0} = c_{1}$$

$$G_{1} + P_{1}G_{0} + P_{1}P_{0}c_{0} = c_{2}$$

$$G_{2} + P_{2}G_{1} + P_{2}P_{1}G_{0} + P_{2}P_{1}P_{0}c_{0} = c_{3}$$

$$G_{3} + P_{3}G_{2} + P_{3}P_{2}G_{1} + P_{3}P_{2}P_{1}G_{0} + P_{3}P_{2}P_{1}P_{0}c_{0} = c_{4}$$

## Carry Equations (2)

$G_0 + P_0 c_{in} = c_0$   $G_1 + P_1 G_0 + P_1 P_0 c_{in} = c_1$   $G_2 + P_2 G_1 + P_2 P_1 G_0 + P_2 P_1 P_0 c_{in} = c_2$   $G_3 + P_3 G_2 + P_3 P_2 G_1 + P_3 P_2 P_1 G_0 + P_3 P_2 P_1 P_0 c_{in} = c_3$

### Carry Chain Adder

Synthesis of Arithmetic Circuits: FPGA, ASIC and Ebedded Systems, J-P Deschamps et al

### Carry Lookahead Adder

Synthesis of Arithmetic Circuits: FPGA, ASIC and Ebedded Systems, J-P Deschamps et al

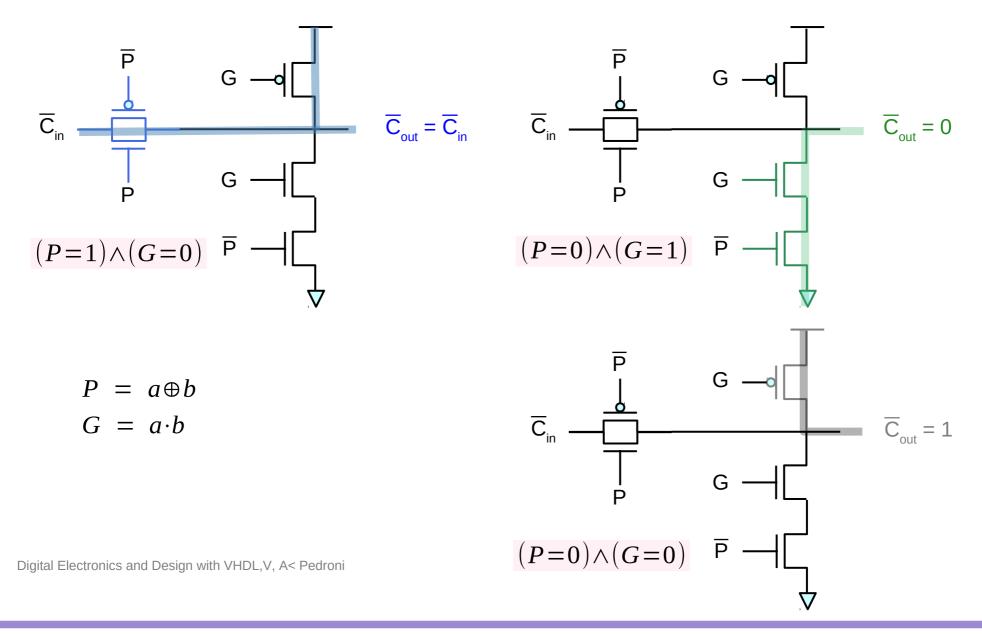

### Carry section of FA

Digital Electronics and Design with VHDL,V, A< Pedroni

### Static Carry Circuit

Principles of CMOS VLSI design – A Systems Perspective, N Weste, K Eshraghian

### Static Carry Circuit – using G, P

P cannot be relaxed

$$P = a \oplus b$$

$P = a + b$

$$G = a \cdot b$$

33

Digital Electronics and Design with VHDL,V, A< Pedroni

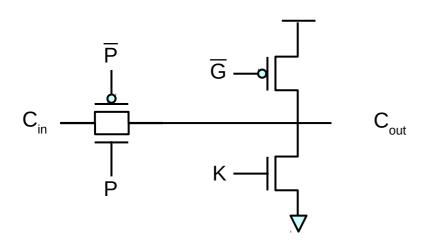

### Static Carry Circuit – using G, P

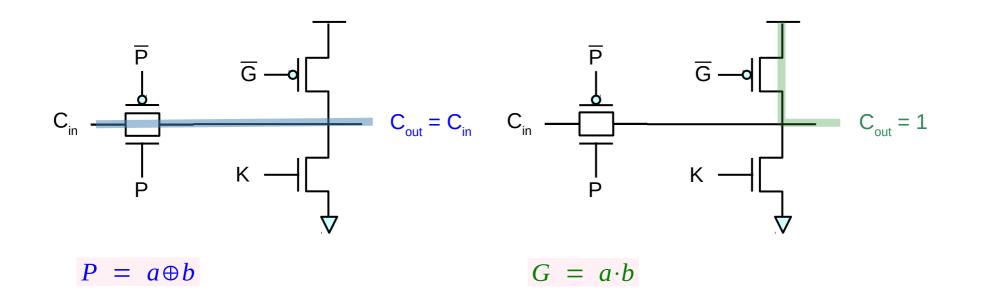

### Static Carry Circuit – using G, P, K

$$P = a \oplus b$$

$$G = a \cdot b$$

$$K = \overline{a} \cdot \overline{b}$$

Digital Electronics and Design with VHDL,V, A< Pedroni

### Static Carry Circuit – using G, P, K

Digital Electronics and Design with VHDL,V, A< Pedroni

Digital Electronics and Design with VHDL, V, A< Pedroni

**Carry Chain Adder**

Principles of CMOS VLSI design – A Systems Perspective, N Weste, K Eshraghian

**Carry Chain Adder**

A multiplexer-based 4-bit adder

cascading four such stages supplying  $P_i$ ,  $G_i$

This is commonly called a **Manchester carry adder**

not Manchester carry chain adder

There is some similarity with the domino carry circuit (nMos) Manchester carry chain adder

However, the intermediate carry gates are no longer needed,  $(G_i, P_i)$ Because the carry values are available in a distributed fashion

Principles of CMOS VLSI design – A Systems Perspective, N Weste, K Eshraghian

The 4-bit adder is chosen to reduce the number of series-propagate transistors Which improves the speed

Note that if all propagate signals are true, and CI is high , six series n-transistors Pull the output node lo in the case of the dynamic gate While five transistors re in series in the static gate

Principles of CMOS VLSI design – A Systems Perspective, N Weste, K Eshraghian

# Manchester Carry Chain – Dynamic Logic

However, <u>not</u> all logic families have these **internal nodes**, **CMOS** being a major example.

Dynamic logic can support shared logic, as can transmission gate logic.

One of the major downsides of the Manchester carry chain is that the **capacitive load** of all of these outputs, together with the resistance of the transistors causes the **propagation delay** to increase much <u>more quickly</u> than a regular carry lookahead.

A Manchester-carry-chain section generally doesn't exceed 4 bits.

https://en.wikipedia.org/wiki/Carry-lookahead\_adder

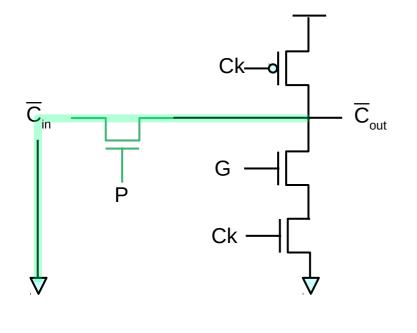

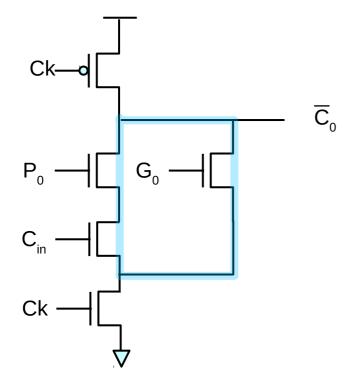

When **CLK** is **low**, the output node is precharged by the **pull-up** transistor

Principles of CMOS VLSI design – A Systems Perspective, N Weste, K Eshraghian

**Carry Chain Adder**

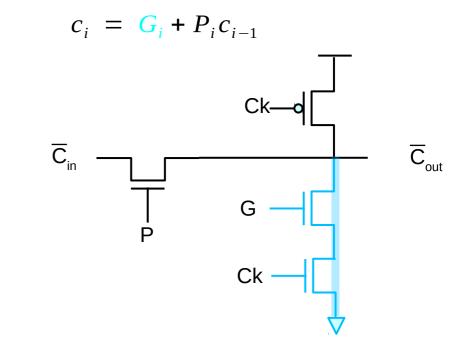

When **CLK** goes **high**, the n **pull-down** transistor turns on If carry generate **G=AB** is **true**, then the output node **discharge**

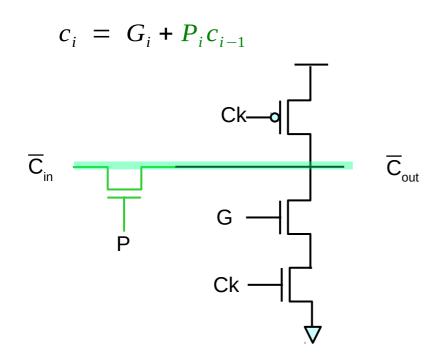

$$c_i = G_i + P_i c_{i-1}$$

Principles of CMOS VLSI design – A Systems Perspective, N Weste, K Eshraghian

When **CLK** goes **high**, the n **pull-down** transistor turns on If carry propagate **P=A+B** is **true**, then a **previous carry** may be coupled to the output node, <u>conditionally</u> **discharging** it

Note that in this circuit CARRY is actually propagated

$$c_i = G_i + P_i c_{i-1}$$

Principles of CMOS VLSI design – A Systems Perspective, N Weste, K Eshraghian

**p(i)** <u> 1 </u> **g(i)** 0 0 1 0 This requires P must not be relaxed 0 0 0 0  $P = a \oplus b$ 0 1 0 1 1 1

Digital Electronics and Design with VHDL,V, A< Pedroni

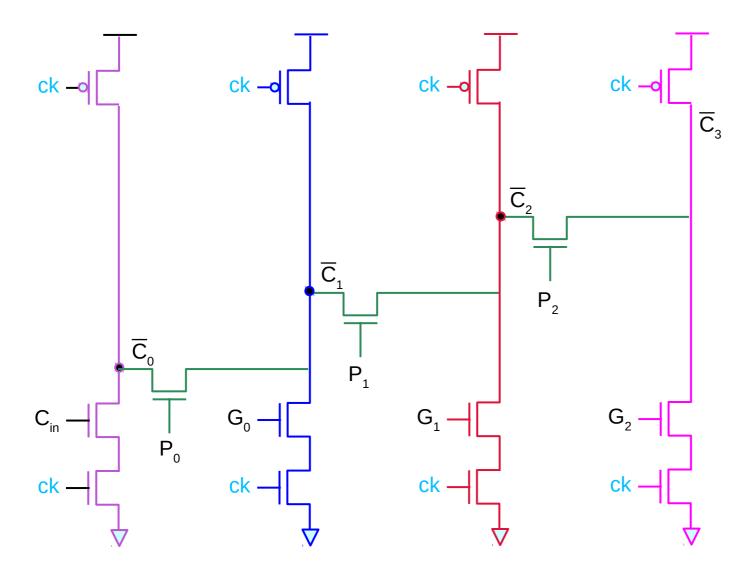

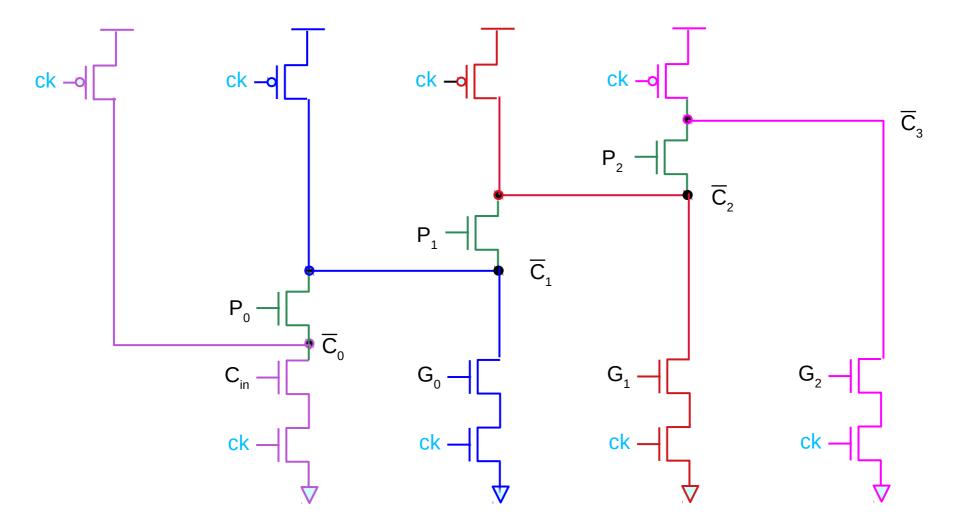

## Dynamic Manchester Carry-Chain Adder

Digital Electronics and Design with VHDL,V, A< Pedroni

## Other representation I

Digital Electronics and Design with VHDL,V, A< Pedroni

## Other representation II

Digital Electronics and Design with VHDL,V, A< Pedroni

## Dynamic Carry Circuit – C<sub>0</sub>

$$c_{out} = Pc_i + G$$

Principles of CMOS VLSI design – A Systems Perspective, N Weste, K Eshraghian

$$c_0 = G_0 + P_0 c_{in}$$

#### **Carry Chain Adder**

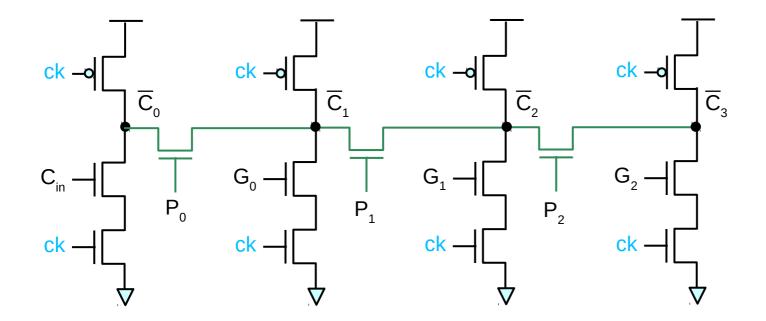

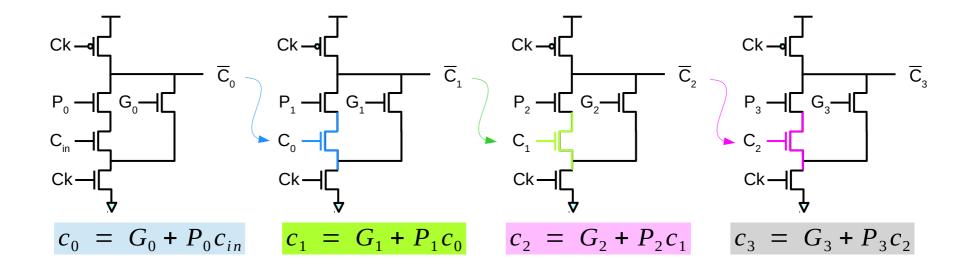

# Dynamic Carry Circuit – C<sub>0</sub>, C<sub>1</sub>, C<sub>2</sub>, C<sub>3</sub>

Principles of CMOS VLSI design – A Systems Perspective, N Weste, K Eshraghian

# Dynamic Carry Circuit – C<sub>1</sub>

Principles of CMOS VLSI design – A Systems Perspective, N Weste, K Eshraghian

#### **Carry Chain Adder**

## Dynamic Carry Circuit – C<sub>2</sub> (1)

Principles of CMOS VLSI design – A Systems Perspective, N Weste, K Eshraghian

#### **Carry Chain Adder**

## Dynamic Carry Circuit – $C_2$ (2)

$c_{0} = G_{0} + P_{0}c_{in}$   $c_{1} = G_{1} + P_{1}c_{0}$  $c_{2} = G_{2} + P_{2}c_{1}$

Principles of CMOS VLSI design – A Systems Perspective, N Weste, K Eshraghian

#### **Carry Chain Adder**

## Dynamic Carry Circuit – C<sub>3</sub> (1)

Principles of CMOS VLSI design – A Systems Perspective, N Weste, K Eshraghian

## Dynamic Carry Circuit – $C_3$ (2)

$c_{0} = G_{0} + P_{0}c_{in}$   $c_{1} = G_{1} + P_{1}c_{0}$   $c_{2} = G_{2} + P_{2}c_{1}$  $c_{3} = G_{3} + P_{3}c_{2}$

Principles of CMOS VLSI design – A Systems Perspective, N Weste, K Eshraghian

# Dynamic Carry Circuit – $C_3$ (3)

Principles of CMOS VLSI design – A Systems Perspective, N Weste, K Eshraghian

#### References

- [1] http://en.wikipedia.org/

- [2] J-P Deschamps, et. al., "Sunthesis of Arithmetic Circuits", 2006