# Contents

| 1            | Free               | eescale 68HC11 1                 |    |  |  |  |  |  |

|--------------|--------------------|----------------------------------|----|--|--|--|--|--|

|              | 1.1                | Architecture                     | 1  |  |  |  |  |  |

|              | 1.2                | Implementations                  | 1  |  |  |  |  |  |

|              | 1.3                | Other versions                   | 2  |  |  |  |  |  |

|              | 1.4                | References                       | 2  |  |  |  |  |  |

|              | 1.5                | External links                   | 2  |  |  |  |  |  |

|              |                    |                                  | 3  |  |  |  |  |  |

| 2 Intel 8085 |                    |                                  |    |  |  |  |  |  |

|              | 2.1                | Description                      | 3  |  |  |  |  |  |

|              |                    | 2.1.1 Programming model          | 4  |  |  |  |  |  |

|              |                    | 2.1.2 Commands/instructions      | 4  |  |  |  |  |  |

|              |                    | 2.1.3 Input/output scheme        | 4  |  |  |  |  |  |

|              |                    | 2.1.4 Development system         | 5  |  |  |  |  |  |

|              | 2.2                | Applications                     | 5  |  |  |  |  |  |

|              | 2.3                | MCS-85 family                    | 5  |  |  |  |  |  |

|              | 2.4                | Educational use                  | 6  |  |  |  |  |  |

|              | 2.5                | Simulators                       | 6  |  |  |  |  |  |

|              | 2.6                | See also                         | 6  |  |  |  |  |  |

|              | 2.7                | References                       | 6  |  |  |  |  |  |

|              | 2.8 External links |                                  | 7  |  |  |  |  |  |

|              |                    |                                  |    |  |  |  |  |  |

| 3            | Intel              | Intel 8086                       |    |  |  |  |  |  |

|              | 3.1                | History                          | 8  |  |  |  |  |  |

|              |                    | 3.1.1 Background                 | 8  |  |  |  |  |  |

|              |                    | 3.1.2 The first x86 design       | 8  |  |  |  |  |  |

|              | 3.2                | Details                          | 9  |  |  |  |  |  |

|              |                    | 3.2.1 Buses and operation        | 9  |  |  |  |  |  |

|              |                    | 3.2.2 Registers and instructions | 9  |  |  |  |  |  |

|              |                    | 3.2.3 Flags                      | 10 |  |  |  |  |  |

|              |                    | 3.2.4 Segmentation               | 10 |  |  |  |  |  |

|              |                    | 3.2.5 Example code               | 11 |  |  |  |  |  |

|              |                    | 3.2.6 Performance                | 12 |  |  |  |  |  |

|              |                    | 3.2.7 Floating point             | 12 |  |  |  |  |  |

|              |                    | - 1                              |    |  |  |  |  |  |

|   | 3.3        | Chip versions                                                    | 12       |

|---|------------|------------------------------------------------------------------|----------|

|   |            | 3.3.1 Derivatives and clones                                     | 12       |

|   | 3.4        | Hardware modes                                                   | 13       |

|   | 3.5        | Peripherals                                                      | 13       |

|   | 3.6        | Microcomputers using the 8086                                    | 14       |

|   | 3.7        | Notes                                                            | 14       |

|   | 3.8        | See also                                                         | 14       |

|   | 3.9        | References                                                       | 14       |

|   | 3.10       | External links                                                   | 15       |

| 4 | Intel      | MCS-51                                                           | 16       |

| - | 4.1        |                                                                  | 16       |

|   | 7.1        |                                                                  | 17       |

|   | 4.2        |                                                                  | 17       |

|   | 4.2        |                                                                  | 17       |

|   | 4.3<br>4.4 |                                                                  | 18       |

|   | 4.4        |                                                                  | 10<br>19 |

|   | 4.5<br>4.6 | Related processors                                               | 19<br>20 |

|   | 4.0        |                                                                  |          |

|   | 4 7        |                                                                  | 20       |

|   | 4.7        | Use as intellectual property                                     | 21       |

|   | 4.8        | MCU based on 8051                                                | 22       |

|   | 4.9        | Digital signal processor (DSP) variants                          | 22       |

|   |            | Enhanced 8-bit binary compatible microcontroller: MCS-151 family | 22       |

|   |            | 8/16/32-bit binary compatible microcontroller: MCS-251 family    | 22       |

|   |            |                                                                  | 22       |

|   |            | References                                                       | 22       |

|   | 4.14       | Further reading                                                  | 23       |

|   | 4.15       | External links                                                   | 23       |

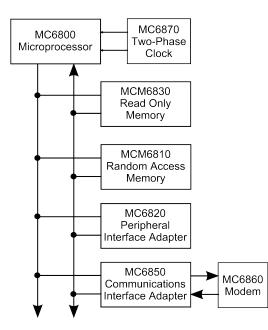

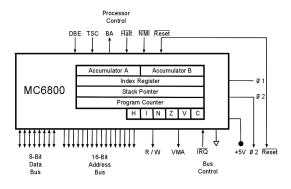

| 5 | Mote       | prola 6800                                                       | 24       |

|   | 5.1        | Motorola's history in semiconductors                             | 24       |

|   | 5.2        | Development team                                                 | 25       |

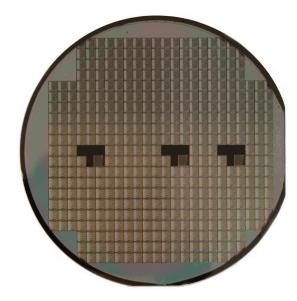

|   | 5.3        | MC6800 microprocessor design                                     | 26       |

|   | 5.4        | MOS ICs                                                          | 27       |

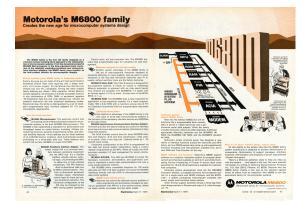

|   | 5.5        | M6800 family introduction                                        | 28       |

|   | 5.6        | Design team breakup                                              | 28       |

|   | 5.7        | Move to Austin                                                   | 29       |

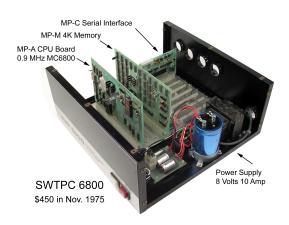

|   | 5.8        | Personal computers                                               | 30       |

|   | 5.9        | Example code                                                     | 31       |

|   |            | Peripherals                                                      | 32       |

|   |            | Second sources                                                   | 32       |

|   |            | Oral histories                                                   |          |

|   |            |                                                                  |          |

|                        | 5.13                | Referen             | nces                                     | 32 |  |  |  |

|------------------------|---------------------|---------------------|------------------------------------------|----|--|--|--|

|                        | 5.14                | Externa             | al links                                 | 35 |  |  |  |

| 6                      | PIC                 | PIC microcontroller |                                          |    |  |  |  |

|                        | 6.1                 | History             | ′                                        | 37 |  |  |  |

|                        | 6.2                 | Core an             | chitecture                               | 37 |  |  |  |

|                        |                     | 6.2.1               | Data space (RAM)                         | 37 |  |  |  |

|                        |                     | 6.2.2               | Code space                               | 38 |  |  |  |

|                        |                     | 6.2.3               | Word size                                | 38 |  |  |  |

|                        |                     | 6.2.4               | Stacks                                   | 38 |  |  |  |

|                        |                     | 6.2.5               | Instruction set                          | 38 |  |  |  |

|                        |                     | 6.2.6               | Performance                              | 38 |  |  |  |

|                        |                     | 6.2.7               | Advantages                               | 39 |  |  |  |

|                        |                     | 6.2.8               | Limitations                              | 39 |  |  |  |

|                        |                     | 6.2.9               | Compiler development                     | 39 |  |  |  |

|                        | 6.3                 | Family              | core architectural differences           | 39 |  |  |  |

|                        |                     | 6.3.1               | Baseline core devices (12 bit)           | 40 |  |  |  |

|                        |                     | 6.3.2               | ELAN Microelectronics clones (13 bit)    | 40 |  |  |  |

|                        |                     | 6.3.3               | Mid-range core devices (14 bit)          | 40 |  |  |  |

|                        |                     | 6.3.4               | Enhanced mid-range core devices (14 bit) | 40 |  |  |  |

|                        |                     | 6.3.5               | PIC17 high end core devices (16 bit)     | 41 |  |  |  |

|                        |                     | 6.3.6               | PIC18 high end core devices (8 bit)      | 41 |  |  |  |

|                        |                     | 6.3.7               | PIC24 and dsPIC 16-bit microcontrollers  | 41 |  |  |  |

|                        |                     | 6.3.8               | PIC32 32-bit microcontrollers            | 42 |  |  |  |

|                        | 6.4                 | Device              | variants and hardware features           | 42 |  |  |  |

|                        |                     | 6.4.1               | Variants                                 | 43 |  |  |  |

|                        |                     | 6.4.2               | Trends                                   | 43 |  |  |  |

|                        |                     | 6.4.3               | Part number suffixes                     | 43 |  |  |  |

|                        |                     | 6.4.4               | PIC clones                               | 43 |  |  |  |

|                        | 6.5                 | Develo              | pment tools                              | 43 |  |  |  |

| 6.6 Device programmers |                     | programmers         | 43                                       |    |  |  |  |

|                        |                     | 6.6.1               | PICKit 2 clones and open source          | 44 |  |  |  |

| 6.7 Debugging          |                     | Debugg              | ging                                     | 44 |  |  |  |

|                        |                     | 6.7.1               | Software emulation                       | 44 |  |  |  |

|                        |                     | 6.7.2               | In-circuit debugging                     | 44 |  |  |  |

|                        |                     | 6.7.3               | In-circuit emulators                     | 44 |  |  |  |

|                        | 6.8                 | 8 Operating systems |                                          |    |  |  |  |

|                        | 6.9                 | .9 See also         |                                          |    |  |  |  |

|                        | 6.10                | 5.10 References     |                                          |    |  |  |  |

|                        | 6.11 External links |                     |                                          |    |  |  |  |

|                        |                     |                     |                                          |    |  |  |  |

| 7.1 | Histor                                             | y 4                             | -6 |  |  |

|-----|----------------------------------------------------|---------------------------------|----|--|--|

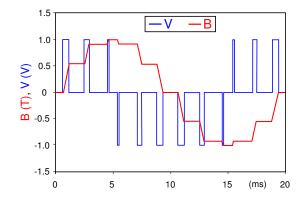

| 7.2 | Princip                                            | ple                             | .7 |  |  |

|     | 7.2.1                                              | Delta                           | .7 |  |  |

|     | 7.2.2                                              | Delta-sigma                     | .7 |  |  |

|     | 7.2.3                                              | Space vector modulation         | -8 |  |  |

|     | 7.2.4                                              | Direct torque control (DTC)     | -8 |  |  |

|     | 7.2.5                                              | Time proportioning              | -8 |  |  |

|     | 7.2.6                                              | Types                           | -8 |  |  |

|     | 7.2.7                                              | Spectrum                        | -8 |  |  |

|     | 7.2.8                                              | PWM sampling theorem            | .9 |  |  |

| 7.3 | Applic                                             | rations                         | .9 |  |  |

|     | 7.3.1                                              | Servos                          | .9 |  |  |

|     | 7.3.2                                              | Telecommunications              | .9 |  |  |

|     | 7.3.3                                              | Power delivery                  | .9 |  |  |

|     | 7.3.4                                              | Voltage regulation              | 0  |  |  |

|     | 7.3.5                                              | Audio effects and amplification | 0  |  |  |

|     | 7.3.6                                              | Electrical                      | 0  |  |  |

| 7.4 | See als                                            | 80                              | 0  |  |  |

| 7.5 | Refere                                             | nces                            | 1  |  |  |

| 7.6 | Extern                                             | al links                        | 1  |  |  |

| 7.7 | Text and image sources, contributors, and licenses |                                 |    |  |  |

|     | 7.7.1                                              | Text                            | 2  |  |  |

|     | 7.7.2                                              | Images                          | 3  |  |  |

|     | 7.7.3                                              | Content license                 | 5  |  |  |

# Chapter 1 Freescale 68HC11

Motorola MC68HC11 in a 48-pin dual in-line package (DIP)

The **68HC11** (**6811** or **HC11** for short) is an 8-bit microcontroller ( $\mu$ C) family introduced by Motorola in 1985.<sup>[1]</sup> Now produced by Freescale Semiconductor, it descended from the Motorola 6800 microprocessor. It is a CISC microcontroller. The 68HC11 devices are more powerful and more expensive than the 68HC08 microcontrollers, and are used in barcode readers, hotel card key writers, amateur robotics, and various other embedded systems. The MC68HC11A8 was the first MCU to include CMOS EEPROM.<sup>[2]</sup>

## **1.1** Architecture

Internally, the HC11 instruction set is upward compatible with the 6800, with the addition of a Y index register. (Instructions using the Y register have opcodes prefixed with the byte 0x18). It has two eight-bit accumulators, A and B, two sixteen-bit index registers, X and Y, a condition code register, a 16-bit stack pointer, and a program counter. In addition, there is an 8 x 8-bit multiply (A x B), with full 16-bit result, and Fractional/Integer 16-bit by 16-bit Divide instructions. A range of 16-bit instructions treat the A and B registers as a combined 16-bit D register for comparison (X and Y registers may also be compared to 16-bit memory operands), addition, subtraction and shift operations, or can add the B accumulator to the X or Y index registers. Bit test operations have also been added, performing a logical AND function between operands, setting the correct conditions codes, but not modifying the operands.

Different versions of the HC11 have different numbers of external ports, labeled alphabetically. The most common

version has five ports, A, B, C, D, and E, but some have as few as 3 ports (version D3). Each port is eight-bits wide except for D, which is six bits (in some variations of the chip, D also has eight bits). It can be operated with an internal program and RAM (1 to 768 bytes) or an external memory of up to 64 kilobytes. With external memory, B and C are used as address and data bus. In this mode, port C is multiplexed to carry both the lower byte of the address and data.

## **1.2 Implementations**

52-pin plastic leaded chip carrier (PLCC)

In the early 1990s Motorola produced an evaluation board kit for the 68HC11 with several UARTs, RAM, and an EPROM. The cost of the evaluation kit was \$68.11.

The standard bootloader for the HC11 family is called BUFFALO, "Bit User Fast Friendly Aid to Logical Operation" (a BUFFALO prompt seen on the serial port at bootup is a sign that a board's flash memory has been erased). Not all HC11 models come with the BUFFALO bootloader. The 68HC11A0 and A1 do not but the A8 does.

## 1.3 Other versions

The Freescale 68HC16 microcontroller family is intended as a 16-bit mostly software compatible upgrade of the 68HC11.

The Freescale 68HC12 microcontroller family is an enhanced 16-bit version of the 68HC11.

The Handy Board robotics controller by Fred Martin is based on the 68HC11.<sup>[3]</sup>

A MC68HC24 port replacement unit is available for the HC11. When placed on the external address bus, it replicates the original functions of B and C. Port A has input capture, output compare, pulse accumulator, and other timer functions; port D has serial I/O, and port E has an analog to digital converter (ADC).

## **1.4 References**

- Hambley, Allan R.(1839). *Electrical Engineering: Principles and Applications*, Pearson Higher Education. p. 417. Digitized by Google. Retrieved on May 17, 2010.

- [2] M68HC11 Reference Manual

- [3] Handy Board Hardware

## 1.5 External links

- Freescale 68HC11 (Legacy) Part Info

- Wytec 68HC11 Development Board

- A fully synthesizable VHDL implementation of the HC11 CPU

- Digital Core Design 68HC11E HDL IP Core

- Digital Core Design 68HC11F HDL IP Core

- Digital Core Design 68HC11K HDL IP Core

- Win/Linux-based freeware macro cross-assembler (ASM11)

- 4MHz-bus 68HC11F1-based board

This article is based on material taken from the Free Online Dictionary of Computing prior to 1 November 2008 and incorporated under the "relicensing" terms of the GFDL, version 1.3 or later.

## **Chapter 2**

## **Intel 8085**

The **Intel 8085** ( extquotedbl*eighty-eighty-five* extquotedbl) is an 8-bit microprocessor introduced by Intel in 1977. It was backward binary compatible with the more-famous Intel 8080 (only adding a few minor instructions) but required less supporting hardware, thus allowing simpler and less expensive microcomputer systems to be built.

The "5" in the model number came from the fact that the 8085 requires only a +5-Volt (V) power supply by using depletion mode transistors, rather than requiring the +5 V, -5 V and +12 V supplies the 8080 needed. This is similar to the competing Z80 (also 8080-derived) introduced the year before. These processors were sometimes used in computers running the CP/M operating system.

The Intel 8085 required at least an external ROM and RAM and an 8 bit address latch (both latches combined in the Intel 8755 2Kx8 EPROM / 2x8 I/O, Intel 8155 256-byte RAM and 22 I/O and 14 bit programmable Timer/Counter) so cannot technically be called a microcontroller.

Both designs (8080/8085) were eclipsed for desktop computers by the compatible Zilog Z80, which took over most of the CP/M computer market as well as taking a share of the booming home computer market in the early-to-mid-1980s.

The 8085 had a long life as a controller. Once designed into such products as the DECtape controller and the VT100 video terminal in the late 1970s, it served for new production throughout the life span of those products (generally longer than the product life of desktop computers).

## 2.1 Description

The 8085 is a conventional von Neumann design based on the Intel 8080. Unlike the 8080 it does not multiplex state signals onto the data bus, but the 8-bit data bus was instead multiplexed with the lower part of the 16-bit address bus to limit the number of pins to 40. Pin No. 40 is used for the power supply (+5 V) and pin No. 20 for ground. Pin No. 39 is used as the hold pin. Pins No. 15 to No. 8 are generally used for address buses.

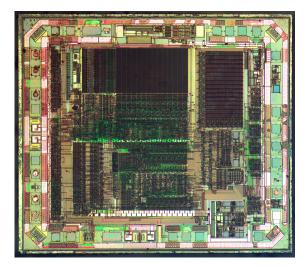

Intel 8085A CPU Die

The processor was designed using nMOS circuitry and the later "H" versions were implemented in Intel's enhanced nMOS process called HMOS, originally developed for fast static RAM products. Only a 5 volt supply is needed, like competing processors and unlike the 8080. The 8085 uses approximately 6,500 transistors.<sup>[1]</sup>

The 8085 incorporates the functions of the 8224 (clock generator) and the 8228 (system controller), increasing the level of integration. A downside compared to similar contemporary designs (such as the Z80) was the fact

that the buses required demultiplexing; however, address latches in the Intel 8155, 8355, and 8755 memory chips allowed a direct interface, so an 8085 along with these chips was almost a complete system.

The 8085 has extensions to support new interrupts, with three maskable interrupts (RST 7.5, RST 6.5 and RST 5.5), one non-maskable interrupt (TRAP), and one externally serviced interrupt (INTR). The RST n.5 interrupts refer to actual pins on the processor, a feature which permitted simple systems to avoid the cost of a separate interrupt controller.

Like the 8080, the 8085 can accommodate slower memories through externally generated wait states (pin 35, READY), and has provisions for Direct Memory Access (DMA) using HOLD and HLDA signals (pins 39 and 38). An improvement over the 8080 was that the 8085 can itself drive a piezoelectric crystal directly connected to it, and a built in clock generator generates the internal high amplitude two-phase clock signals at half the crystal frequency (a 6.14 MHz crystal would yield a 3.07 MHz clock, for instance).

The 8085 is a binary compatible follow up on the 8080, using the same basic instruction set as the 8080. Only a few minor instructions were new to the 8085 above the 8080 set.

#### 2.1.1 Programming model

The processor has seven 8-bit registers accessible to the programmer, named A, B, C, D, E, H, and L, where A is the 8-bit accumulator and the other six can be used as independent byte-registers or as three 16-bit register pairs, BC, DE, and HL, depending on the particular instruction. Some instructions use HL as a (limited) 16-bit accumulator. As in the 8080, the contents of the memory address pointed to by HL could be accessed as pseudo register M. It also has a 16-bit program counter and a 16-bit stack pointer to memory (replacing the 8008's internal stack). Instructions such as PUSH PSW, POP PSW affected the Program Status Word (Accumulator and Flags).

#### 2.1.2 Commands/instructions

As in many other 8-bit processors, all instructions are encoded in a single byte (including register-numbers, but excluding immediate data), for simplicity. Some of them are followed by one or two bytes of data, which could be an immediate operand, a memory address, or a port number. Like larger processors, it has CALL and RET instructions for multi-level procedure calls and returns (which can be conditionally executed, like jumps) and instructions to save and restore any 16-bit register-pair on the machine stack. There are also eight one-byte call instructions (RST) for subroutines located at the fixed addresses 00h, 08h, 10h,...,38h. These were intended to be supplied by external hardware in order to invoke a corresponding interrupt-service routine, but are also often employed as fast system calls. The most sophisticated command was XTHL, which is used for exchanging the register pair HL with the value stored at the address indicated by the stack pointer.

#### 8-bit instructions

Most 8-bit operations work on the 8-bit accumulator (the A register). For two operand 8-bit operations, the other operand can be either an immediate value, another 8-bit register, or a memory cell addressed by the 16-bit register pair HL. Direct copying is supported between any two 8-bit registers and between any 8-bit register and a HL-addressed memory cell. Due to the regular encoding of the MOV-instruction (using a quarter of available opcode space) there are redundant codes to copy a register into itself (MOV B,B, for instance), which are of little use, except for delays. However, what would have been a copy from the HL-addressed cell into itself (i.e., MOV M,M) instead encodes the HLT instruction, halting execution until an external reset or interrupt occurred (providing interrupts were enabled).

#### **16-bit operations**

Although the 8085 is an 8-bit processor, it has some 16bit operations. Any of the three 16-bit register pairs (BC, DE, HL or SP) could be loaded with an immediate 16bit value (using LXI), incremented or decremented (using INX and DCX), or added to HL (using DAD). LHLD loaded HL from directly-addressed memory and SHLD stored HL likewise. The XCHG operation exchanges the values of HL and DE. Adding HL to itself performs a 16bit arithmetical left shift with one instruction. The only 16 bit instruction that affects any flag was DAD (adding HL to BC, DE, HL or SP), which updates the carry flag to facilitate 24-bit or larger additions and left shifts (for a floating point mantissa for instance). Adding the stack pointer to HL is useful for indexing variables in (recursive) stack frames. A stack frame can be allocated using DAD SP and SPHL, and a branch to a computed pointer can be done with PCHL. These abilities make it feasible to compile languages such as PL/M, Pascal, or C with 16-bit variables and produce 8085 machine code.

Subtraction and bitwise logical operations on 16 bits is done in 8-bit steps. Operations that have to be implemented by program code (subroutine libraries) included comparisons of signed integers as well as multiply and divide.

#### 2.1.3 Input/output scheme

The 8085 supported up to 256 input/output (I/O) ports, accessed via dedicated Input/Output instructions—taking

port addresses as operands. This Input/Output mapping scheme was regarded as an advantage, as it freed up the processor's limited address space.

#### 2.1.4 Development system

Intel produced a series of development systems for the 8080 and 8085, known as the MDS-80 Microprocessor System. The original development system had an 8080 processor. Later 8085 and 8086 support was added including ICE (in-circuit emulators). It was a large and heavy desktop box, about a 20" cube (in the Intel corporate blue colour) which included a CPU, monitor, and a single 8 inch floppy disk drive. Later an external box was available with two more floppy drives. It ran the ISIS operating system and could also operate an emulator pod and an external EPROM programmer. This unit used the Multibus card cage which was intended just for the development system. A surprising number of spare card cages and processors were being sold, leading to the development of the Multibus as a separate product.

The later iPDS was a portable unit, about 8" x 16" x 20", with a handle. It had a small green screen, a keyboard built into the top, a 51/4 inch floppy disk drive, and ran the ISIS-II operating system. It could also accept a second 8085 processor, allowing a limited form of multiprocessor operation where both processors ran simultaneously and independently. The screen and keyboard could be switched between them, allowing programs to be assembled on one processor (large programs took awhile) while files were edited in the other. It had a bubble memory option and various programming modules, including EPROM and Intel 8048 and 8051 programming modules which were plugged into the side, replacing stand-alone device programmers. In addition to an 8080/8085 assembler, Intel produced a number of compilers including PL/M-80 and Pascal languages, and a set of tools for linking and statically locating programs to enable them to be burnt into EPROMs and used in embedded systems.

A lower cost SDK-85 System Design Kit board was provided with an 8085 CPU, 8355 ROM containing a debugging monitor program, 8155 RAM and 22 I/O, 8279 hex keypad and 8-digit 7-segment LED, TTY (Teletype) 20 mA current loop serial interface. Pads were available for one more 2Kx8 8755 EPROM and another 256 byte RAM 8155 I/O Timer/Counter could be optionally added. All data, control and address signals were available on dual pin headers and a large prototype area was provided.

## 2.2 Applications

For the extensive use of 8085 in various applications, the microprocessor is provided with an instruction set which consists of various instructions such as MOV, ADD,

The 8085 processor was used in a few early personal computers, for example, the TRS-80 Model 100 line used an OKI manufactured 80C85 (MSM80C85ARS). The CMOS version 80C85 of the NMOS/HMOS 8085 processor has several manufacturers. Some manufacturers provide variants with additional functions such as additional instructions. The rad-hard version of the 8085 has been in on-board instrument data processors for several NASA and ESA space physics missions in the 1990s and early 2000s, including CRRES, Polar, FAST, Cluster, HESSI, the Sojourner Mars Rover,<sup>[2]</sup> and THEMIS. The Swiss company SAIA used the 8085 and the 8085-2 as the CPUs of their PCA1 line of programmable logic controllers during the 1980s.

Pro-Log Corp. put the 8085 and supporting hardware on an STD Bus format card containing CPU, RAM, sockets for ROM/EPROM, I/O and external bus interfaces. The included Instruction Set Reference Card used entirely different mnemonics for the Intel 8085 CPU, as the product was a direct competitor to Intel's Multibus card offerings.

## 2.3 MCS-85 family

The 8085 CPU was one part of a family of chips developed by Intel, for building a complete system. Many of these support chips were also used with other processors. The original IBM PC based on the Intel 8088 processor used several of these chips; the equivalent functions today are provided by VLSI chips, namely the extquotedblSouthbridge extquotedbl chips.

- 8085-CPU

- 8155-RAM+ 3 I/O Ports+Timer

- 8156-RAM+ 3 I/O Ports+Timer

- 8185-SRAM

- 8355-16,384-bit (2048 x 8) ROM with I/O

- 8604-4096-bit (512 x 8) PROM

- 8755-EPROM+2 I/O Ports

- 8202-Dynamic RAM Controller

- 8203-Dynamic RAM Controller

- 8205-1 Of 8 Binary Decoder

- 8206-Error Detection & Correction Unit

- 8207-DRAM Controller

- 8210-TTL To MOS Shifter & High Voltage Clock Driver

- 8212-8 Bit I/O Port

- 8216-4 Bit Parallel Bidirectional Bus Driver

- 8218/8219-Bus Controller

- 8226-4 Bit Parallel Bidirectional Bus Driver

- 8231-Arithmetic Processing Unit

- 8232-Floating Point Processor

- 8237-DMA Controller

- 8251-Communication Controller

- 8253-Programmable Interval Timer

- 8254-Programmable Interval Timer

- 8255-Programmable Peripheral Interface

- 8256-Multifunction Support Controller

- 8257-DMA Controller

- 8259-Programmable Interrupt Controller

- 8271-Programmable Floppy Disk Controller

- 8272-Single/Double Density Floppy Disk Controller

- 8273-Programmable HDLC/SDLC Protocol Controller

- 8274-Multi-Protocol Serial Controller

- 8275-CRT Controller

- 8276-Small System CRT Controller

- 8275-Programmable Key Board Interface

- 8279-Key Board/Display Controller

- 8282–8-bit Non-Inverting Latch with Output Buffer

- 8283-8-bit Inverting Latch with Output Buffer

- 8291-GPIB Talker/Listener

- 8293-GPIB Transceiver

- 8294-Data Encryption/Decryption Unit+1 O/P Port

- 8295-Dot Matrix Printer Controller

## 2.4 Educational use

In many engineering schools<sup>[3]</sup> <sup>[4]</sup>the 8085 processor is used in introductory microprocessor courses. Trainer kits composed of a printed circuit board, 8085, and supporting hardware are offered by various companies. These kits usually include complete documentation allowing a student to go from solder to assembly language programming in a single course. Also the architecture of this and the associated instruction set is easy for a student to understand.

### 2.5 Simulators

Some of the simulators available for the 8085 microprocessor are listed below:

- GNUSim8085 It consists of a simulator, assembler and a debugger. It is available for both Windows and Linux operating systems.

- Win85 Open source (under the MIT license) simulator/debugger for Windows <sup>[5]</sup>

- 8085 simulator It includes a simulated keypad, an assembler and a simulator.

- Intel 8085 Simulator for Android. <sup>[6]</sup>

- ENVI85 It was written by professors Stefan Fedyschyn and Edwin Kay. This and the above simulator are provided on the CD that accompanies the book, *Microprocessor Architecture, Programming and Applications with the 8085* by Ramesh Gaonkar.

## 2.6 See also

- GNUSim8085 An open source multi-platform simulator software for the 8085 processor.

- IBM System/23 Datamaster gave IBM designers familiarity with the 8085 support chips used in the IBM PC

## 2.7 References

- The history of the microcomputer-invention and evolution, S Mazor - Proceedings of the IEEE, 1995

- [2] A Description of the Rover Sojourner

- [3]

- [4] Микропроцесорски системи

- [5] Win85 project homepage

[6]

- William Stallings Computer Organization and Architecture: Designing for Performance 8th Ed. Prentice Hall, 2009 ISBN 0-13-607373-5

- Abhishek Yadav Microprocessor 8085, 8086 Firewall Media, 2008 ISBN 81-318-0356-2

- Ramesh Gaonkar *Microprocessor Architecture, Programming and Applications with the 8085* Penram International Publishing ISBN 81-87972-09-2

- Bill Detwiler *Tandy TRS-80 Model 100 Teardown* Tech Republic, 2011 Web

## 2.8 External links

- Pin diagram and pin description of 8085

- Function of IC's Used in 8085 Microprocessor

## **Chapter 3**

## **Intel 8086**

The **8086**<sup>[1]</sup> ( extquotedbl*eighty-eighty-six* extquotedbl, also called **iAPX 86**)<sup>[2]</sup> is a 16-bit microprocessor chip designed by Intel between early 1976 and mid-1978, when it was released. The Intel 8088, released in 1979, was a slightly modified chip with an external 8-bit data bus (allowing the use of cheaper and fewer supporting  $ICs^{[note 1]}$ ), and is notable as the processor used in the original IBM PC design, including the widespread version called IBM PC XT.

The 8086 gave rise to the x86 architecture which eventually turned out as Intel's most successful line of processors.

## 3.1 History

### 3.1.1 Background

In 1972, Intel launched the 8008, the first 8-bit microprocessor.<sup>[note 2]</sup> It implemented an instruction set designed by Datapoint corporation with programmable CRT terminals in mind, that also proved to be fairly general purpose. The device needed several additional ICs to produce a functional computer, in part due to it being packaged in a small 18-pin "memory-package", which ruled out the use of a separate address bus (Intel was primarily a DRAM manufacturer at the time).

Two years later, Intel launched the 8080,<sup>[note 3]</sup> employing the new 40-pin DIL packages originally developed for calculator ICs to enable a separate address bus. It had an extended instruction set that was source- (not binary-) compatible with the 8008 and also included some 16-bit instructions to make programming easier. The 8080 device, often described as the first truly useful microprocessor, was eventually replaced by the depletion-load based 8085 (1977) which could cope with a single 5V power supply instead of the three different operating voltages of earlier chips.<sup>[note 4]</sup> Other well known 8-bit microprocessors that emerged during these years were Motorola 6800 (1974), General Instrument PIC16X (1975), MOS Technology 6502 (1975), Zilog Z80 (1976), and Motorola 6809 (1978).

#### 3.1.2 The first x86 design

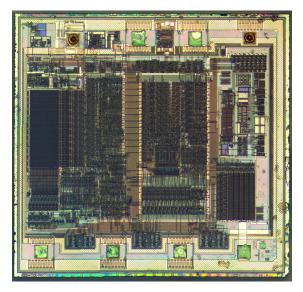

Intel 8086 CPU Die Image

The 8086 project started in May 1976 and was originally intended as a temporary substitute for the ambitious and delayed iAPX 432 project. It was an attempt to draw attention from the less-delayed 16 and 32-bit processors of other manufacturers (such as Motorola, Zilog, and National Semiconductor) and at the same time to counter the threat from the Zilog Z80 (designed by former Intel employees), which became very successful. Both the architecture and the physical chip were therefore developed rather quickly by a small group of people, and using the same basic microarchitecture elements and physical implementation techniques as employed for the slightly older 8085 (and for which the 8086 also would function as a continuation).

Marketed as source compatible, the 8086 was designed to allow assembly language for the 8008, 8080, or 8085 to be automatically converted into equivalent (sub-optimal) 8086 source code, with little or no hand-editing. The programming model and instruction set was (loosely) based on the 8080 in order to make this possible. However, the 8086 design was expanded to support full 16-bit processing, instead of the fairly basic 16-bit capabilities of the 8080/8085. New kinds of instructions were added as well; full support for signed integers, base+offset addressing, and selfrepeating operations were akin to the Z80 design<sup>[3]</sup> but were all made slightly more general in the 8086. Instructions directly supporting nested ALGOL-family languages such as Pascal and PL/M were also added. According to principal architect Stephen P. Morse, this was a result of a more software centric approach than in the design of earlier Intel processors (the designers had experience working with compiler implementations). Other enhancements included microcoded multiply and divide instructions and a bus-structure better adapted to future co-processors (such as 8087 and 8089) and multiprocessor systems.

The first revision of the instruction set and high level architecture was ready after about three months,<sup>[note 5]</sup> and as almost no CAD-tools were used, four engineers and 12 layout people were simultaneously working on the chip.<sup>[note 6]</sup> The 8086 took a little more than two years from idea to working product, which was considered rather fast for a complex design in 1976–1978.

The 8086 was sequenced<sup>[note 7]</sup> using a mixture of random logic<sup>[4]</sup> and microcode and was implemented using depletion-load nMOS circuitry with approximately 20,000 active transistors (29,000 counting all ROM and PLA sites). It was soon moved to a new refined nMOS manufacturing process called HMOS (for High performance MOS) that Intel originally developed for manufacturing of fast static RAM products.<sup>[note 8]</sup> This was followed by HMOS-II, HMOS-III versions, and, eventually, a fully static CMOS version for battery-powered devices, manufactured using Intel's CHMOS processes.<sup>[note 9]</sup> The original chip measured 33 mm<sup>2</sup> and minimum feature size was 3.2  $\mu$ m.

The architecture was defined by Stephen P. Morse with some help and assistance by Bruce Ravenel (the architect of the 8087) in refining the final revisions. Logic designer Jim McKevitt and John Bayliss were the lead engineers of the hardware-level development team<sup>[note 10]</sup> and William Pohlman the manager for the project. The legacy of the 8086 is enduring in the basic instruction set of today's personal computers and servers; the 8086 also lent its last two digits to later extended versions of the design, such as the Intel 286 and the Intel 386, all of which eventually became known as the x86 family. (Another reference is that the PCI Vendor ID for Intel devices is 8086<sub>h</sub>.)

### 3.2 Details

#### 3.2.1 Buses and operation

All internal registers, as well as internal and external data buses, were 16 bits wide, firmly establishing the "16-bit microprocessor" identity of the 8086. A 20-bit external address bus gave a 1 MB physical address space ( $2^{20}$  =

The 8086 pin-assignments in min and max mode

1,048,576). This address space was addressed by means of internal 'segmentation'. The data bus was multiplexed with the address bus in order to fit a standard 40-pin dual in-line package. 16-bit I/O addresses meant 64 KB of separate I/O space ( $2^{16} = 65,536$ ). The maximum **linear** address space was limited to 64 KB, simply because internal registers were only 16 bits wide. Programming over 64 KB boundaries involved adjusting segment registers (see below) and remained so until the 80386 introduced wider (32 bits) main registers (the memory management hardware in the 286 did not help in this regard, as registers were still 16 bits).

Some of the control pins, which carry essential signals for all external operations, had more than one function depending upon whether the device was operated in *min* or *max* mode. The former was intended for small single processor systems while the latter was for medium or large systems, using more than one processor.

#### 3.2.2 Registers and instructions

The 8086 has eight more or less general 16-bit registers (including the stack pointer but excluding the instruction pointer, flag register and segment registers). Four of them, AX, BX, CX, DX, could also be accessed as twice

as many 8-bit registers (see figure) while the other four, BP, SI, DI, SP, were 16-bit only.

Due to a compact encoding inspired by 8-bit processors, most instructions were one-address or two-address operations which means that the result was stored in one of the operands. At most one of the operands could be in memory, but this memory operand could also be the *destination*, while the other operand, the *source*, could be either *register* or *immediate*. A single memory location could also often be used as both *source* and *destination* which, among other factors, further contributed to a code density comparable to (and often better than) most eight bit machines.

Although the degree of generality of most registers were much greater than in the 8080 or 8085, it was still fairly low compared to the typical contemporary minicomputer, and registers were also sometimes used implicitly by instructions. While perfectly sensible for the assembly programmer, this made register allocation for compilers more complicated compared to more regular 16- and 32-bit processors such as the PDP-11, VAX, 68000, 32016 etc. On the other hand, it was more regular and orthogonal than ubiquitous but rather minimalistic 8-bit microprocessors such as the 6502, 6800, 6809, 8085, MCS-48, 8051 and other contemporary accumulator based machines. It was significantly easier to construct an efficient code generator for the 8086 design.

Another factor for this was that the 8086 also introduced some new instructions (not present in the 8080 and 8085) to better support stack based high level programming languages such as Pascal and PL/M; some of the more useful ones were **push** *mem-op*, and **ret** *size*, supporting the "pascal calling convention extquotedbl directly. (Several others, such as **push** *immed* and **enter**, would be added in the subsequent 80186, 80286, and 80386 processors.)

The 8086 had a 64 KB of 8-bit (or alternatively 32 Kword of 16-bit) I/O space. A 64 KB (one segment) stack growing towards lower addresses is supported in hardware; 2-byte words are pushed to the stack and the stack top is pointed to by SS:SP. There are 256 interrupts, which can be invoked by both hardware and software. The interrupts can cascade, using the stack to store the return addresses.

#### 3.2.3 Flags

8086 has a 16-bit flags register. Nine of these condition code flags are active, and indicate the current state of the processor: Carry flag (CF), Parity flag (PF), Auxiliary carry flag (AF), Zero flag (ZF), Sign flag (SF), Trap flag (TF), Interrupt flag (IF), Direction flag (DF), and Overflow flag (OF).

#### 3.2.4 Segmentation

See also: x86 memory segmentation

There are also four 16-bit segment registers (see figure) that allow the 8086 CPU to access one megabyte of memory in an unusual way. Rather than concatenating the segment register with the address register, as in most processors whose address space exceeded their register size, the 8086 shifts the 16-bit segment only four bits left before adding it to the 16-bit offset (16×segment + offset), therefore producing a 20-bit external (or effective or physical) address from the 32-bit segment:offset pair. As a result, each external address can be referred to by  $2^{12} = 4096$  different segment:offset pairs.

Although considered complicated and cumbersome by many programmers, this scheme also has advantages; a small program (less than 64 KB) can be loaded starting at a fixed offset (such as 0000) in its own segment, avoiding the need for relocation, with at most 15 bytes of alignment waste.

Compilers for the 8086-family commonly support two types of pointer, *near* and *far*. Near pointers are 16-bit offsets implicitly associated with the program's code or data segment and so can be used only within parts of a program small enough to fit in one segment. Far pointers are 32-bit segment:offset pairs resolving to 20-bit external addresses. Some compilers also support *huge* pointers, which are like far pointers except that pointer arithmetic on a huge pointer treats it as a linear 20-bit pointer, while pointer arithmetic on a far pointer wraps around within its 16-bit offset without touching the segment part of the address.

To avoid the need to specify *near* and *far* on numerous pointers, data structures, and functions, compilers also support "memory models" which specify default pointer sizes. The *tiny* (max 64K), *small* (max 128K), *compact* (data > 64K), *medium* (code > 64K), *large* (code,data > 64K), and *huge* (individual arrays > 64K) models cover practical combinations of near, far, and huge pointers for code and data. The *tiny* model means that code and data are shared in a single segment, just as in most 8-bit based processors, and can be used to build *.com*-files for instance. Precompiled libraries often came in several versions compiled for different memory models.

According to Morse et al., the designers actually contemplated using an 8-bit shift (instead of 4-bit), in order to create a 16 MB physical address space. However, as this would have forced segments to begin on 256-byte boundaries, and 1 MB was considered very large for a microprocessor around 1976, the idea was dismissed. Also, there were not enough pins available on a low-cost 40-pin package for the additional four address bus pins.<sup>[5]</sup>

In principle, the address space of the x86 series *could* have been extended in later processors by increasing the shift value, as long as applications obtained their seg-

ments from the operating system and did not make assumptions about the equivalence of different segment: offset pairs.<sup>[note 11]</sup> In practice the use of "huge" pointers and similar mechanisms was widespread and the flat 32bit addressing made possible with the 32-bit offset registers in the 80386 eventually extended the limited addressing range in a more general way (see below).

Intel could have decided to implement memory in 16 bit words (which would have eliminated the BHE signal along with much of the address bus complexities already described). This would mean that all instruction object codes and data would have to be accessed in 16-bit units. Users of the 8080 long ago realised, in hindsight, that the processor makes very efficient use of its memory. By having a large number of 8-bit object codes, the 8080 produces object code as compact as some of the most powerful minicomputers on the market at the time.<sup>[6]:5-26</sup>

If the 8086 is to retain 8-bit object codes and hence the efficient memory use of the 8080, then it cannot guarantee that (16-bit) opcodes and data will lie on an even-odd byte address boundary. The first 8-bit opcode will shift the next 8-bit instruction to an odd byte or a 16-bit instruction to an odd-even byte boundary. By implementing the BHE signal and the extra logic needed, the 8086 has allowed instructions to exist as 1-byte, 3-byte or any other odd byte object codes.<sup>[6]:5-26</sup>

Simply put: this is a trade off. If memory addressing is simplified so that memory is only accessed in 16-bit units, memory will be used less efficiently. Intel decided to make the logic more complicated, but memory use more efficient. This was at a time when memory size was considerably smaller, and at a premium, than that which users are used to today.<sup>[6]:5-26</sup>

#### Porting older software

Small programs could ignore the segmentation and just use plain 16-bit addressing. This allowed 8-bit software to be quite easily ported to the 8086. The authors of MS-DOS took advantage of this by providing an Application Programming Interface very similar to CP/M as well as including the simple *.com* executable file format, identical to CP/M. This was important when the 8086 and MS-DOS were new, because it allowed many existing CP/M (and other) applications to be quickly made available, greatly easing acceptance of the new platform.

#### 3.2.5 Example code

The following 8086/8088 assembler source code is for a subroutine named \_memcpy that copies a block of data bytes of a given size from one location to another. The data block is copied one byte at a time, and the data movement and looping logic utilizes 16-bit operations.

; \_memcpy(dst, src, len) ; Copy a block of memory from

one location to another. ; ; Entry stack parameters ; [BP+6] = len, Number of bytes to copy ; [BP+4] = src, Address of source data block ; [BP+2] = dst, Address of target data block ; ; Return registers ; AX = Zero 0000:1000 org 1000h ; Start at 0000:1000h 0000:1000 \_memcpy proc 0000:1000 55 push bp ; Set up the call frame 0000:1001 89 E5 mov bp,sp 0000:1003 06 push es ; Save ES 0000:1004 8B 4E 06 mov cx,[bp+6] ; Set CX = len 0000:1007 E3 11 jcxz done ; If len=0, return 0000:1009 8B 76 04 mov si,[bp+4] ; Set SI = src 0000:100C 8B 7E 02 mov di,[bp+2] ; Set DI = dst 0000:100F 1E push ds ; Set ES = DS 0000:1010 07 pop es 0000:1011 8A 04 loop mov al,[si] ; Load AL from [src] 0000:1013 88 05 mov [di],al ; Store AL to [dst] 0000:1015 46 inc si ; Increment src 0000:1016 47 inc di ; Increment dst 0000:1017 49 dec cx ; Decrement len 0000:1018 75 F7 jnz loop ; Repeat the loop 0000:101A 07 done pop es ; Restore ES 0000:101B 5D pop bp ; Restore previous call frame 0000:101C 29 C0 sub ax,ax ; Set AX = 0 0000:101E C3 ret ; Return 0000:101F end proc

The code above uses the BP (base pointer) register to establish a call frame, an area on the stack that contains all of the parameters and local variables for the execution of the subroutine. This kind of calling convention supports reentrant and recursive code, and has been used by most ALGOL-like languages since the late 1950s. The ES segment register is saved on the stack and replaced with the value of the DS segment register, so that the MOV AL instructions will operate within the same source and destination data segment. Before returning, the subroutine restores the previous value of the ES register.

The above routine is a rather cumbersome way to copy blocks of data. Provided the source and the destination blocks reside within single 65,536 byte segments (a requirement of the above routine), advantage can be taken of the 8086's block MOV instructions. The loop section of the above can be replaced by:

0000:1011 F2 loop rep ; Repeat until CX=0 0000:1012 A5 movsw ; Move the data block

This copies the block of data one word at a time. The REP instruction causes the following MOVSW to repeat until CX=0, automatically incrementing SI and DI as it repeats. Alternatively the MOVSB or MOVSD instructions can be used to copy single bytes or double words at a time. Most assemblers will assemble correctly if the REP instruction is used as a prefix to MOVSW as in REP MOVSW.

This routine will operate correctly if interupted, because the program counter will continue to point to the REP instruction until the block copy is completed. The copy will therefore continue from where it left off when the interupt service routine returns control.

#### 3.2.6 Performance

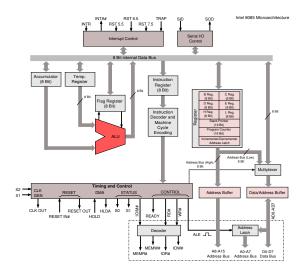

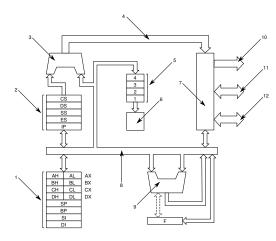

Simplified block diagram over Intel 8088 (a variant of 8086); 1=main registers; 2=segment registers and IP; 3=address adder; 4=internal address bus; 5=instruction queue; 6=control unit (very simplified!); 7=bus interface; 8=internal databus; 9=ALU; 10/11/12=external address/data/control bus.

Although partly shadowed by other design choices in this particular chip, the multiplexed address and data buses limited performance slightly; transfers of 16-bit or 8-bit quantities were done in a four-clock memory access cycle, which was faster on 16-bit, although slower on 8-bit quantities, compared to many contemporary 8-bit based CPUs. As instructions varied from one to six bytes, fetch and execution were made concurrent and decoupled into separate units (as it remains in today's x86 processors): The bus interface unit fed the instruction stream to the execution unit through a 6-byte prefetch queue (a form of loosely coupled pipelining), speeding up operations on registers and immediates, while memory operations unfortunately became slower (four years later, this performance problem was fixed with the 80186 and 80286). However, the full (instead of partial) 16-bit architecture with a full width ALU meant that 16-bit arithmetic instructions could now be performed with a single ALU cycle (instead of two, via internal carry, as in the 8080 and 8085), speeding up such instructions considerably. Combined with orthogonalizations of operations versus operand-types and addressing modes, as well as other enhancements, this made the performance gain over the 8080 or 8085 fairly significant, despite cases where the older chips may be faster (see below).

- EA = time to compute effective address, ranging from 5 to 12 cycles.

- Timings are best case, depending on prefetch status, instruction alignment, and other factors.

As can be seen from these tables, operations on registers and immediates were fast (between 2 and 4 cycles), while memory-operand instructions and jumps were quite slow; jumps took more cycles than on the simple 8080 and 8085, and the 8088 (used in the IBM PC) was additionally hampered by its narrower bus. The reasons why most memory related instructions were slow were threefold:

- Loosely coupled fetch and execution units are efficient for instruction prefetch, but not for jumps and random data access (without special measures).

- No dedicated address calculation adder was afforded; the microcode routines had to use the main ALU for this (although there was a dedicated *segment* + *offset* adder).

- The address and data buses were multiplexed, forcing a slightly longer (33~50%) bus cycle than in typical contemporary 8-bit processors.

However, memory access performance was drastically enhanced with Intel's next generation chips. The 80186 and 80286 both had dedicated address calculation hardware, saving many cycles, and the 80286 also had separate (non-multiplexed) address and data buses.

### 3.2.7 Floating point

The 8086/8088 could be connected to a mathematical coprocessor to add hardware/microcode-based floating point performance. The Intel 8087 was the standard math coprocessor for the 8086 and 8088, operating on 80-bit numbers. Manufacturers like Cyrix (8087-compatible) and Weitek (*non* 8087-compatible) eventually came up with high performance floating point co-processors that competed with the 8087 as well as with the subsequent, higher performing Intel 80387.

## **3.3** Chip versions

The clock frequency was originally limited to 5 MHz (IBM PC used 4.77 MHz, 4/3 the standard NTSC color burst frequency), but the last versions in HMOS were specified for 10 MHz. HMOS-III and CMOS versions were manufactured for a long time (at least a while into the 1990s) for embedded systems, although its successor, the 80186/80188 (which includes some on-chip peripherals), has been more popular for embedded use.

The 80C86, the CMOS version of the 8086, was used in the GRiDPad, Toshiba T1200, HP 110, and finally the 1998-1999 Lunar Prospector.

#### **3.3.1** Derivatives and clones

Compatible—and, in many cases, enhanced—versions were manufactured by Fujitsu, Harris/Intersil, OKI,

Soviet clone KP1810BM86.

OKI M80C86A QFP-56.

NEC µPD8086D-2 (8MHz) from 1984year 19week JAPAN (clone of Intel D8086-2)

Siemens AG, Texas Instruments, NEC, Mitsubishi, AMD. For example, the NEC V20 and NEC V30 pair were hardware compatible with the 8088 and 8086 even though NEC made original Intel clones  $\mu$ PD8088D and  $\mu$ PD8086D, respectively, but incorporated the instruction set of the 80186 along with some (but not all) of the 80186 speed enhancements, providing a drop-in capability to upgrade both instruction set and processing speed without manufacturers having to modify their designs. Such relatively simple and low-power 8086-compatible processors in CMOS are still used in embedded systems.

The electronics industry of the Soviet Union was able to replicate the 8086 through both industrial espionage and

reverse engineering. The resulting chip, K1810BM86, was binary and pin-compatible with the 8086.

i8088 and i8086 were respectively the cores of the Sovietmade PC-compatible EC1831 and EC1832 desktops (EC1831 is the EC identification of IZOT 1037C and EC1832 is the EC identification of IZOT 1036C, developed and manufactured in Bulgaria). However, EC1832 computer (IZOT 1036C) had significant hardware differences from its authentic prototype, and the data/address bus circuitry was designed independently of Intel products. EC1832 was the first PC compatible computer with dynamic bus sizing (US Pat. No 4,831,514). Later some of the ES1832 principles were adopted in PS/2 (US Pat. No 5,548,786) and some other machines (UK Patent Application, Publication No. GB-A-2211325, Published June. 28, 1989).

## 3.4 Hardware modes

The 8086 and 8088 support two hardware modes: maximum mode and minimum mode. Maximum mode is for large applications such as multiprocessing and is also required to support the 8087 coprocessor. The mode is usually hard-wired into the circuit and cannot be changed by software. Specifically, pin #33 (MN/MX) is either wired to voltage or to ground to determine the mode. Changing the state of pin #33 changes the function of certain other pins, most of which have to do with how the CPU handles the (local) bus. The IBM PC and PC/XT use an Intel 8088 running in maximum mode, which allows the CPU to work with an optional 8087 coprocessor installed in the math coprocessor socket on the PC or PC/XT mainboard. (The PC and PC/XT may require Max mode for other reasons, such as perhaps to support the DMA controller.)

## **3.5** Peripherals

- Intel 8237: direct memory access (DMA) controller

- Intel 8251: USART

- Intel 8253: programmable interval timer

- Intel 8255: programmable peripheral interface

- Intel 8259: programmable interrupt controller

- Intel 8279: keyboard/display controller

- Intel 8282/8283: 8-Bit latch

- Intel 8284: clock generator

- Intel 8286/8287: bidirectional 8-Bit driver

- Intel 8288: bus controller

- Intel 8289: bus arbiter

#### 3.6 **Microcomputers** using 8086

- The Xerox NoteTaker was one of the earliest portable computer designs in 1978 and used three 8086 chips (as CPU, graphics processor, and i/o processor), but never entered commercial production.

- Seattle Computer Products shipped S-100 bus based 8086 systems (SCP200B) as early as November 1979.

- The Norwegian Mycron 2000, introduced in 1980.

- One of the most influential microcomputers of all, the IBM PC, used the Intel 8088, a version of the 8086 with an eight-bit data bus (as mentioned above)

- The first Compaq Deskpro used an 8086 running at 7.14 MHz, (?) but was capable of running add-in cards designed for the 4.77 MHz IBM PC XT.

- An 8 MHz 8086 was used in the AT&T 6300 PC (built by Olivetti), an IBM PC-compatible desktop microcomputer. The M24 / PC 6300 has IBM PC/XT compatible 8-bit expansion slots, but some of them have a proprietary extension providing the full 16-bit data bus of the 8086 CPU (similar in concept to the 16-bit slots of the IBM PC AT, but different in the design details, and physically incompatible).

- The IBM PS/2 models 25 and 30 were built with an 8 MHz 8086.

- Amstrad/Schneider PC1512, PC1640, • The PC2086, PC3086 and PC5086 all used 8086 CPUs at 8 MHz.

- The NEC PC-9801.

- The Tandy 1000 SL-series and RL machines used 8086 CPUs.

- The IBM Displaywriter word processing machine<sup>[8]</sup> and the Wang Professional Computer, manufactured by Wang Laboratories, also used the 8086.

- NASA used original 8086 CPUs on equipment for ground-based maintenance of the Space Shuttle Discovery until the end of the space shuttle program in 2011. This decision was made to prevent software regression that might result from upgrading or from switching to imperfect clones.<sup>[9]</sup>

- KAMAN Process and Area Radiation Monitors<sup>[10]</sup>

#### the 3.7 Notes

- [1] Fewer TTL buffers, latches, multiplexers (although the amount of TTL logic was not drastically reduced). It also permitted the use of cheap 8080-family ICs, where the 8254 CTC, 8255 PIO, and 8259 PIC were used in the IBM PC design. In addition, it made PCB layout simpler and boards cheaper, as well as demanding fewer (1- or 4bit wide) DRAM chips.

- [2] using enhancement load PMOS logic (demanding 14V, achieving TTL-compatibility by having VCC at +5V and VDD at -9V)

- [3] using non-saturated enhancement load NMOS logic (demanding a higher gate voltage for the load transistor-gates)

- [4] made possible with depletion load nMOS logic (the 8085 was later made using HMOS processing, just like the 8086)

- [5] Rev.0 of the instruction set and architecture was ready in about three months, according to Morse.

- [6] Using rubylith, light boards, rulers, electric erasers, and a digitizer (according to Jenny Hernandez, member of the 8086 design team, in a statement made on Intel's web-page for its 25th birthday).

- [7] 8086 used less microcode than many competitors' designs, such as the MC68000 and others

- [8] Fast static RAMs in MOS technology (as fast as bipolar RAMs) was an important product for Intel during this period.

- [9] CHMOS is Intel's name for CMOS circuits manufactured using processing steps very similar to HMOS.

- [10] Other members of the design team were Peter A.Stoll and Jenny Hernandez.

- [11] Some 80186 clones did change the shift value, but were never commonly used in desktop computers.

#### 3.8 See also

- Transistor count

- iAPX, for the iAPX name

#### 3.9 References

- [1] "Microprocessor Hall of Fame". Intel. Archived from the original on 2007-07-06. Retrieved 2007-08-11.

- [2] Official Intel iAPX 286 programmers' manual (page 1-1)

- [3] Birth of a Standard: The Intel 8086 Microprocessor. Thirty years ago, Intel released the 8086 processor, introducing the x86 architecture that underlies every PC-Windows, Mac, or Linux-produced today, PC World, June 17, 2008

- [4] Randall L. Geiger, Phillip E. Allen, Noel R. Strader VLSI design techniques for analog and digital circuits, McGraw-Hill Book Co., 1990, ISBN 0-07-023253-9, page 779 "Random Logic vs. Structured Logic Forms", illustration of use of "random" describing CPU control logic

- [5] Intel 8008 to 8086 by Stephen P. Morse et al.

- [6] Osborne 16 bit Processor Handbook (Adam Osborne & Gerry Kane) ISBN 0-931988-43-8

- [7] Microsoft Macro Assembler 5.0 Reference Manual. Microsoft Corporation. 1987. "Timings and encodings in this manual are used with permission of Intel and come from the following publications: Intel Corporation. iAPX 86, 88, 186 and 188 User's Manual, Programmer's Reference, Santa Clara, Calif. 1986." (Similarly for iAPX 286, 80386, 80387.)

- [8] Zachmann, Mark (August 23, 1982). "Flaws in IBM Personal Computer frustrate critic". *InfoWorld* (Palo Alto, CA: Popular Computing) 4 (33): 57–58. ISSN 0199-6649. "the IBM Displaywriter is noticeably more expensive than other industrial micros that use the 8086."

- [9] For Old Parts, NASA Boldly Goes ... on eBay, May 12, 2002.

- [10] Kaman Tech. Manual

## **3.10** External links

- Architecture-Of-8086 and pin at scanftree.com

- Intel datasheets

- List of 8086 CPUs and their clones at CPUworld.com

- 8086 Pinouts

- Maximum Mode Interface

- The 8086 User's manual October 1979 INTEL Corporation (PDF document)

- 8086 program codes using emu8086 (Version 4.08) Emulator

- Intel 8086/80186 emulator written in C, this file is part of a larger PC emulator

## **Chapter 4**

## Intel MCS-51

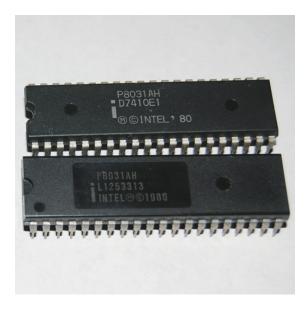

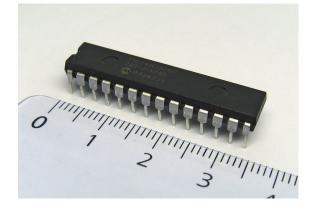

Intel P8051 microcontroller.

SAB-C515-LN by Infineon is based on the 8051

The **Intel MCS-51** (commonly referred to as **8051**) is a Harvard architecture, CISC instruction set, single chip microcontroller ( $\mu$ C) series which was developed by Intel in 1980 for use in embedded systems.<sup>[11]</sup> Intel's original versions were popular in the 1980s and early 1990s and enhanced binary compatible derivatives remain popular today.

Intel's original MCS-51 family was developed using NMOS technology, but later versions, identified by a letter C in their name (e.g., 80C51) used CMOS technology and consume less power than their NMOS predecessors. This made them more suitable for battery-powered devices.

The family was continued in 1996 with the enhanced 8-bit MCS-151 and the 8/16/32-bit MCS-251 family of binary compatible microcontrollers.<sup>[2]</sup> While Intel no longer manufactures the MCS-51, MCS-151 and MCS-251 family, enhanced binary compatible derivatives made by numerous vendors remain popular today. Some derivatives integrate a digital signal processor (DSP). In addition to these physical devices, several companies also offer MCS-51 derivatives as IP cores for use in FPGAs or ASICs designs.

## 4.1 Important features and applications

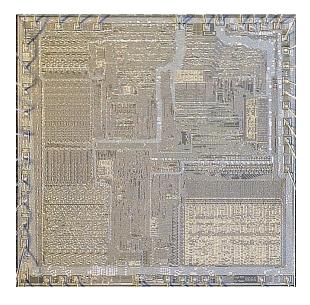

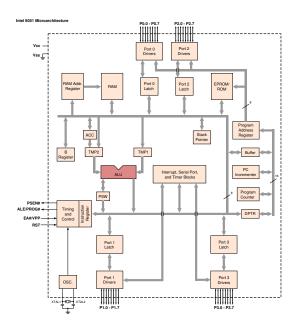

i8051 microarchitecture.

The 8051 architecture provides many functions (CPU, RAM, ROM, I/O, interrupt logic, timer, etc.) in a single package

• 8-bit ALU and Accumulator, 8-bit Registers (one 16-bit register with special move instructions), 8-bit data bus and 2×16-bit address bus/program

counter/data pointer and related 8/11/16-bit operations; hence it is mainly an 8-bit microcontroller

- Boolean processor with 17 instructions, 1-bit accumulator, 32 registers (4 bit-addressable 8-bit) and up to 144 special 1 bit-addressable RAM variables (18 bit-addressable 8-bit)<sup>[3]</sup>

- Multiply, divide and compare instructions

- 4 fast switchable register banks with 8 registers each (memory mapped)

- Fast interrupt with optional register bank switching

- Interrupts and threads with selectable priority<sup>[4]</sup>

- Dual 16-bit address bus It can access 2 x 2<sup>16</sup> memory locations – 64 KB (65,536 locations) each of RAM and ROM

- 128 bytes of on-chip RAM (IRAM)

- 4 KiB of on-chip ROM, with a 16-bit (64 KiB) address space (PMEM). Not included on 803X variants

- Four 8-bit bi-directional input/output port

- UART (serial port)

- Two 16-bit Counter/timers

- Power saving mode (on some derivatives)

One feature of the 8051 core is the inclusion of a boolean processing engine which allows bit-level boolean logic operations to be carried out directly and efficiently on select internal registers and select RAM locations. This feature helped cement the 8051's popularity in industrial control applications because it reduced code size by as much as 30%. Another feature is the inclusion of four bank selectable working register sets which greatly reduce the amount of time required to complete an interrupt service routine. With a single instruction the 8051 can switch register banks as opposed to the time consuming task of transferring the critical registers also allowed the 8051 to quickly perform a context switch.

Once a UART, and a timer if necessary, has been configured, the programmer needs only write a simple interrupt routine to refill the *send* shift register whenever the last bit is shifted out by the UART and/or empty the full *receive* shift register (copy the data somewhere else). The main program then performs serial reads and writes simply by reading and writing 8-bit data to stacks.

#### 4.1.1 Derivate features

As of 2013, new derivates are still developed by many major chipmakers, and major compiler suppliers such as IAR Systems, Keil and Altium Tasking continuously release updates.

MCS-51 based microcontrollers typically include one or two UARTs, two or three timers, 128 or 256 bytes of internal data RAM (16 bytes of which are bit-addressable), up to 128 bytes of I/O, 512 bytes to 64 KB of internal program memory, and sometimes a quantity of extended data RAM (ERAM) located in the external data space. The original 8051 core ran at 12 clock cycles per machine cycle, with most instructions executing in one or two machine cycles. With a 12 MHz clock frequency, the 8051 could thus execute 1 million one-cycle instructions per second or 500,000 two-cycle instructions per second. Enhanced 8051 cores are now commonly used which run at six, four, two, or even one clock per machine cycle, and have clock frequencies of up to 100 MHz, and are thus capable of an even greater number of instructions per second. All Silicon Labs, some Dallas and a few Atmel devices have single cycle cores.

8051 variants may include built-in reset timers with brown-out detection, on-chip oscillators, selfprogrammable Flash ROM program memory, built-in external RAM, extra internal program storage, bootloader code in ROM, EEPROM non-volatile data storage, 1<sup>2</sup>C, SPI, and USB host interfaces, CAN or LIN bus, ZigBee or Bluetooth radio modules, PWM generators, analog comparators, A/D and D/A converters, RTCs, extra counters and timers, in-circuit debugging facilities, more interrupt sources, extra power saving modes, etc.

In many engineering schools the 8051 microcontroller is used in introductory microcontroller courses.

## 4.2 Memory architecture

The MCS-51 has four distinct types of memory – internal RAM, special function registers, program memory, and external data memory.

Internal RAM (IRAM) is located from address 0 to address 0xFF. IRAM from 0x00 to 0x7F can be accessed directly. IRAM from 0x80 to 0xFF must be accessed indirectly, using the @R0 or @R1 syntax, with the address to access loaded in R0 or R1. The 128 bits at IRAM locations 0x20–0x2F are bit-addressable.

Special function registers (SFR) are located in the same address space as IRAM, at addresses 0x80 to 0xFF, and are accessed directly using the same instructions as for the lower half of IRAM. They can *not* be accessed indirectly via @R0 or @R1. 16 of the SFRs are also bitaddressable.

Program memory (PMEM, though less common in usage than IRAM and XRAM) is up to 64 KiB of readonly memory, starting at address 0 in a separate address space. It may be on- or off-chip, depending on the particular model of chip being used. Program memory is readonly, though some variants of the 8051 use on-chip flash memory and provide a method of re-programming the memory in-system or in-application. In addition to code, it is possible to store read-only data in program memory, accessed by the MOVC A, @DPTR instruction. Data is fetched from the address specified in the 16-bit special function register DPTR.

External data memory (XRAM) is a third address space, also starting at address 0. It can also be on- or off-chip; what makes it "external" is that it must be accessed using the MOVX (Move eXternal) instruction. Many variants of the 8051 include the standard 256 bytes of IRAM plus a few KB of XRAM on the chip.

The 8051 is designed as a strict Harvard architecture. The 8051 can only execute code fetched from program memory. The 8051 does not have any instruction to write to program memory. Most 8051 systems respect this distinction, and so are unable to download and directly execute new programs. The strict Harvard architecture has the advantage of making such systems immune to most forms of malware. Some 8051 systems have (or can be modified to have) some "dual-mapped" RAM, making them act somewhat more like Princeton architecture. This (partial) Princeton architecture has the advantage of making it possible for a Forth boot loader running on the 8051 to write new native code to RAM and then execute it, leading to faster incremental and interactive programming cycles than strict Harvard systems.<sup>[5][6]</sup>

## 4.3 Registers

The only register on an 8051 that is not memory-mapped is the 16-bit program counter PC. This specifies the address of the next instruction to execute. Relative branch instructions supply an 8-bit signed offset which is added to the PC.

The following registers are memory-mapped into the special function register space:

- (0x81) Stack pointer SP. This is an 8-bit register used by subroutine call and return instructions. The stack grows upward; the SP is incremented before pushing, and decremented after popping a value.

- (0x82–83) Data pointer DP. This is a 16-bit register that is used for accessing PMEM and XRAM.

- (0xD0) Program status word PSW. This contains important status flags:

- --- PSW.0: P Parity. Gives the parity (modulo-2 sum of the bits of) the most recent ALU result.

- --- PSW.1: UD User Defined. For general software use, not otherwise used by hardware.

- --- PSW.2: OV Overflow flag. Set when addition produces a signed overflow.

- --- PSW.3: RS0 Register select 0. The low-order bit of the register bank. Set when banks at 0x08 or 0x18 are in use.

- --- PSW.4: RS1 Register select 1. The high-order bit of the register bank. Set when banks at 0x10 or 0x18 are in use.

- --- PSW.5: F0 Flag 0. For general software use, not otherwise used by hardware.

- --- PSW.6: AC auxiliary carry. Set when addition produces a carry from bit 3 to bit 4.

- --- PSW.7: C Carry bit.

- (0xE0) Accumulator A. This register is used by most instructions.

- (0xF0) B register. This is used as an extension to the accumulator for multiply and divide instructions.

In addition, there are 8 general purpose registers R0–R7, mapped to IRAM between 0x00 and 0x1F. Only 8 bytes of that range are used at any given time, determined by the bank select bits in the PSW.

256 single bits are directly addressable. These are the 16 IRAM locations from 0x20–0x2F, and the 16 special function registers 0x80, 0x88, 0x90, ..., 0xF8.

Note that the PSW does not contain the common N (negative) and Z (zero) flags. Instead, because the accumulator is a bit-addressible SFR, it is possible to branch on individual bits of it, including the msbit. There is also an instruction to jump if the accumulator is zero or non-zero.

## 4.4 Instruction set

Instructions are all 1 to 3 bytes long, consisting of an initial opcode byte, followed by up to 2 bytes of operands.

There are 16 basic ALU instructions that operate between the accumulator and a second operand, specified using one of the following addressing modes:

- Register direct, R0–R7 (opcodes x8–xF)

- Register indirect, @R0 or @R1 (opcodes x6 and x7)

- Memory direct, specifying an IRAM or SFR location (opcodes *x*5, followed by 1 byte of address)

- Immediate, specifying an 8-bit constant (opcodes *x*4, followed by 1 byte of data)

The instructions are as follows. Not all support all addressing modes; the immediate mode in particular is sometimes nonsensical:

- 0y INC *operand*: Increment the specified operand. Opcode 04 specifies "INC A"

- 1*y* DEC *operand*: Decrement the specified operand. Opcode 14 specifies "DEC A"

- 2y ADD A, *operand*: Add the operand to the accumulator A.

- 3y ADDC A,*operand*: Add the operand, plus the C bit, to the accumulator.

- 4y ORL A, *operand*: Logical OR the operand into the A register.

- 5*y* ANL A,*operand*: Logical AND the operand into the A register.

- 6y XRL A, operand: Logical exclusive-OR the operand into the A register.

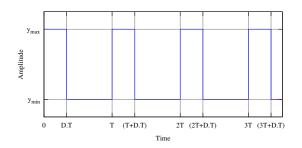

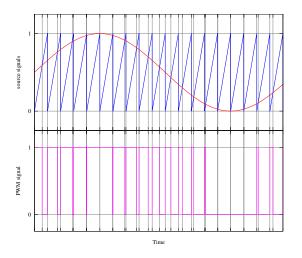

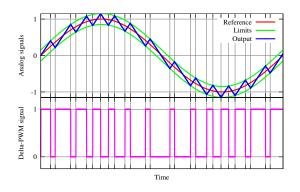

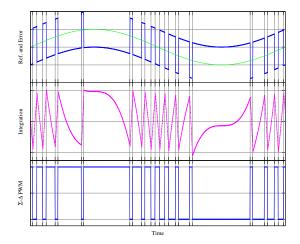

- 7y MOV operand,#data: Move immediate data to the operand. Opcode 74 specifies "MOV A,#data.