# Logic Families

# Contents

# Articles

|    | Logic family                             | 1  |

|----|------------------------------------------|----|

|    | Resistor–transistor logic                | 7  |

|    | Diode-transistor logic                   | 10 |

|    | Emitter-coupled logic                    | 11 |

|    | Gunning transceiver logic                | 16 |

|    | Transistor-transistor logic              | 16 |

|    | PMOS logic                               | 23 |

|    | NMOS logic                               | 24 |

|    | CMOS                                     | 25 |

|    | BiCMOS                                   | 33 |

|    | Integrated injection logic               | 34 |

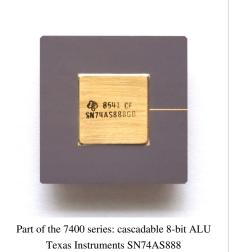

|    | 7400 series                              | 35 |

|    | List of 7400 series integrated circuits  | 41 |

|    | 4000 series                              | 62 |

|    | List of 4000 series integrated circuits  | 69 |

| Re | eferences                                |    |

|    | Article Sources and Contributors         | 75 |

|    | Image Sources, Licenses and Contributors | 76 |

| Aı | rticle Licenses                          |    |

|    | License                                  | 77 |

# Logic family

In computer engineering, a **logic family** may refer to one of two related concepts. A logic family of monolithic digital integrated circuit devices is a group of electronic logic gates constructed using one of several different designs, usually with compatible logic levels and power supply characteristics within a family. Many logic families were produced as individual components, each containing one or a few related basic logical functions, which could be used as "building-blocks" to create systems or as so-called "glue" to interconnect more complex integrated circuits. A "logic family" may also refer to a set of techniques used to implement logic within VLSI integrated circuits such as central processors, memories, or other complex functions. Some such logic families use static techniques to minimize design complexity. Other such logic families, such as domino logic, use clocked dynamic techniques to minimize size, power consumption, and delay.

Before the widespread use of integrated circuits, various solid-state and vacuum-tube logic systems were used but these were never as standardized and interoperable as the integrated-circuit devices.

#### **Technologies**

The list of packaged building-block logic families can be divided into categories, listed here in roughly chronological order of introduction, along with their usual abbreviations:

- Resistor-transistor logic (RTL)

- Direct-coupled transistor logic (DCTL)

- Resistor-capacitor-transistor logic (RCTL)

- Diode-transistor logic (DTL)

- Complemented transistor diode logic (CTDL)

- High-threshold logic (HTL)

- Emitter-coupled logic (ECL)

- Positive emitter-coupled logic (PECL)

- Low-voltage positive emitter-coupled logic (LVPECL)

- Gunning transceiver logic (GTL)

- Transistor-transistor logic (TTL)

- P-type metal—oxide—semiconductor logic (PMOS)

- N-type metal-oxide-semiconductor logic (NMOS)

- Depletion-load NMOS logic

- High-density nMOS (HMOS)

- Complementary metal—oxide—semiconductor logic (CMOS)

- Bipolar complementary metal—oxide—semiconductor logic (BiCMOS)

- Integrated injection logic (I<sup>2</sup>L)

The families (RTL, DTL, and ECL) were derived from the logic circuits used in early computers, originally implemented using discrete components. One example is the Philips NORbits family of logic building blocks.

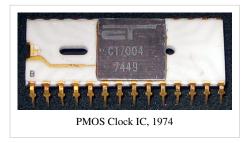

The PMOS and I<sup>2</sup>L logic families were used for relatively short periods, mostly in special purpose custom large-scale integration circuits devices and are generally considered obsolete. For example, early digital clocks or electronic calculators may have used one or more PMOS devices to provide most of the logic for the finished product. The F14 CADC, Intel 4004, Intel 4040, and Intel 8008 microprocessors and their support chips were PMOS.

Of these families, only ECL, TTL, NMOS, CMOS, and BiCMOS are currently still in widespread use. ECL is used for very high-speed applications because of its price and power demands, while NMOS logic is mainly used in VLSI

circuits applications such as CPUs and memory chips which fall outside of the scope of this article. Present-day "building block" logic gate ICs are based on the ECL, TTL, CMOS, and BiCMOS families.

#### **RTL**

Main article: Resistor-transistor logic

The Atanasoff–Berry Computer used resistor-coupled vacuum tube logic circuits similar to RTL. Several early transistorized computers (e.g., IBM 1620, 1959) used RTL, where it was implemented using discrete components.

A family of simple resistor–transistor logic integrated circuits was developed at Fairchild Semiconductor for the Apollo Guidance Computer in 1962. Texas Instruments soon introduced its own family of RTL. A variant with integrated capacitors, RCTL, had increased speed, but lower immunity to noise than RTL. This was made by Texas Instruments as their "51XX" series.

#### DTL

Main article: Diode-transistor logic

Diode logic goes back as far as ENIAC and was used in many early vacuum tube computers. Several early transistorized computers (e.g., IBM 1401) used DTL, where it was implemented using discrete components.

The first diode–transistor logic family of integrated circuits was introduced by Signetics in 1962. DTL was also made by Fairchild and Westinghouse. A family of diode logic and diode-transistor logic integrated circuits was developed by Texas Instruments for the D-37C Minuteman II Guidance Computer in 1962, but these devices were not available to the public.

A variant of DTL called "high-threshold logic" incorporated Zener diodes to create a large offset between logic 1 and logic 0 voltage levels. These devices usually ran off a 15 volt power supply and were found in industrial control, where the high differential was intended to minimize the effect of noise.<sup>[1]</sup>

#### **ECL**

Main article: Emitter-coupled logic

The ECL family, ECL is also known as current-mode logic (CML), was invented by IBM as current steering logic for use in the transistorized IBM 7030 Stretch computer, where it was implemented using discrete components.

The first ECL logic family to be available in integrated circuits was introduced by Motorola as MECL in 1962. [2]

#### TTL

Main article: Transistor-transistor logic

The first transistor-transistor logic family of integrated circuits was introduced by Sylvania as *Sylvania Universal High–Level Logic* (SUHL) in 1963. Texas Instruments introduced 5400 Series TTL family in 1964. Transistor–transistor logic uses bipolar transistors to form its integrated circuits.<sup>[3]</sup> TTL has changed significantly over the years, with newer versions replacing the older types.

Since the transistors of a standard TTL gate are saturated switches, minority carrier storage time in each junction limits the switching speed of the device. Variations on the basic TTL design are intended to reduce these effects and improve speed, power consumption, or both.

The German physicist Walter H. Schottky formulated a theory predicting the **Schottky effect**, which led to the Schottky diode and later Schottky transistors. Schottky transistors have a much higher switching speed than conventional transistors because the Schottky junction does not promote charge storage, leading to faster switching gates. Gates built with Schottky transistors use more power than normal TTL and switch faster. With **Low-power**

**Schottky** (LS), internal resistance values were increased to reduce power consumption and increase switching speed over the original version. The introduction of **Advanced Low-power Schottky** (ALS) further increased speed and reduced power consumption. A faster logic family called **Fast** (Schottky) (F) was also introduced that was faster than normal Schottky TTL.

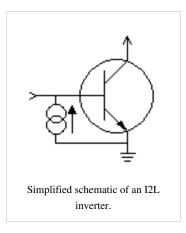

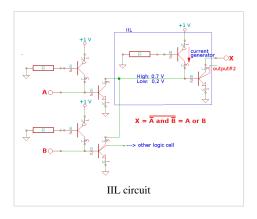

#### IIL

Main article: integrated injection logic

The integrated injection logic (IIL or  $I^2L$ ) uses bipolar transistors in a kind of current-steering arrangement to form its integrated circuits. IIL is slightly easier to construct on an integrated circuit, and so was popular for early VLSI circuits.

#### **CMOS**

Main article: CMOS

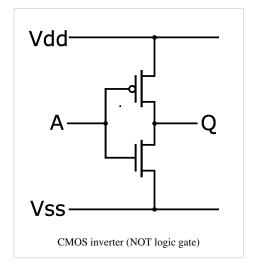

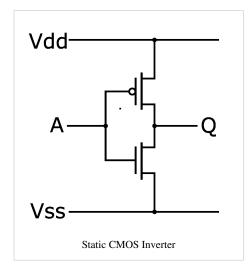

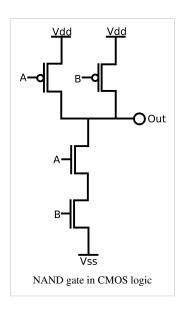

CMOS logic gates use complementary arrangements of N-channel and P-channel Field effect transistor. Since the initial devices used oxide-isolated metal gates, they were called **CMOS** (complementary metal—oxide—semiconductor logic). In contrast to TTL, CMOS uses almost no power in the static state (that is, when inputs are not changing). A CMOS gate draws no current other than leakage when in a steady 1 or 0 state. When the gate switches states, current is drawn from the power supply to charge the capacitance at the output of the gate. This means that the current draw of CMOS devices increases with switching rate (controlled by clock speed, typically).

The first CMOS family of logic integrated circuits was introduced by RCA as *CD4000 COS/MOS*, the 4000 series, in 1968. Initially CMOS logic was slower than LS-TTL. However, because the logic thresholds of CMOS were proportional to the power supply voltage, CMOS devices were well-adapted to battery-operated systems with simple power supplies. CMOS gates can also tolerate much wider voltage ranges than TTL gates because the logic thresholds are (approximately) proportional to power supply voltage, and not the fixed levels required by bipolar circuits.

The required silicon area for implementing such digital CMOS functions has rapidly shrunk. VLSI technology incorporating millions of basic logic operations onto one chip, almost exclusively uses CMOS. The extremely small capacitance of the on-chip wiring, caused an increase in performance by several orders of magnitude. On-chip clock rates as high as 4 GHz have become common, approximately 1000 times faster than the technology by 1970.

#### Lowering the power supply voltage

CMOS chips often work with a broader range of power supply voltages than other logic families. Early TTL ICs required a power supply voltage of 5V, but early CMOS could use 3 to 15V. [4] Lowering the supply voltage reduces the charge stored on any capacitances and consequently reduces the energy required for a logic transition. Reduced energy implies less heat dissipation. The energy stored in a capacitance C and changing V volts is  $\frac{1}{2}CV^2$ . By lowering the power supply from 5V to 3.3V, switching power was reduced by almost 60 percent (power dissipation is proportional to the square of the supply voltage). Newer CPUs have lowered their power supply voltages further.

#### **HC** logic

Because of the incompatibility of the CD4000 series of chips with the previous TTL family, a new standard emerged which combined the best of the TTL family with the advantages of the CD4000 family. It was known as the 74HC (High-performance silicon gate) family of devices and used the pinout of the 74LS family with an improved version of CMOS technology inside the chip. It could be used both with logic devices which used 3.3V power supplies (and thus 3.3V logic levels), and with devices that used 5V power supplies and TTL logic levels.

#### The CMOS-TTL logic level problem

Interconnecting any two logic families often required special techniques such as additional pull-up resistors, or purpose-built interface circuits, since the logic families may use different voltage levels to represent 1 and 0 states, and may have other interface requirements only met within the logic family.

TTL logic levels are different from those of CMOS – generally a TTL output does not rise high enough to be reliably recognized as a logic 1 by a CMOS input. This problem was solved by the invention of the 74HCT family of devices that uses CMOS technology but TTL input logic levels. These devices only work with a 5V power supply. They form a replacement for TTL, although HCT is slower than original TTL (HC logic has about the same speed as original TTL).

#### Other CMOS families

Other CMOS circuit families within integrated circuits include cascode voltage switch logic (CVSL) and pass transistor logic (PTL) of various sorts. These are generally used "on-chip" and are not delivered as building-block medium-scale or small-scale integrated circuits.

#### **BiCMOS**

Main article: BiCMOS

One major improvement was to combine CMOS inputs and TTL drivers to form of a new type of logic devices called BiCMOS logic, of which the LVT and ALVT logic families are the most important. The BiCMOS family has many members, including ABT logic, ALB logic, ALVT logic, BCT logic and LVT logic.

#### **Improved versions**

With HC and HCT logic and LS-TTL logic competing in the market it became clear that further improvements were needed to create the *ideal* logic device that combined high speed, with low power dissipation and compatibility with older logic families. A whole range of newer families has emerged that use CMOS technology. A short list of the most important family designators of these newer devices includes:

- LV logic (lower supply voltage)

- LVT logic (lower supply voltage while retaining TTL logic levels)

- ALVT logic (an 'advanced' version of LVT logic)

There are many others including AC/ACT logic, AHC/AHCT logic, ALVC logic, AUC logic, AVC logic, CBT logic, CBTLV logic, FCT logic and LVC logic (LVCMOS).

#### Monolithic integrated circuit logic families compared

The following logic families would either have been used to build up systems from functional blocks such as flip-flops, counters, and gates, or else would be used as "glue" logic to interconnect very-large scale integration devices such as memory and processors. Not shown are some early obscure logic families from the early 1960s such as DCTL (direct-coupled transistor logic), which did not become widely available.

*Propagation delay* is the time taken for a two-input NAND gate to produce a result after a change of state at its inputs. *Toggle speed* represents the fastest speed at which a J-K flip flop could operate. *Power per gate* is for an individual 2-input NAND gate; usually there would be more than one gate per IC package. Values are very typical and would vary slightly depending on application conditions, manufacturer, temperature, and particular type of logic circuit. *Introduction year* is when at least some of the devices of the family were available in volume for civilian uses. Some military applications pre-dated civilian use. <sup>[5][6]</sup>

| Family | Description               | Propagation<br>delay (ns) | Toggle speed<br>(MHz) | Power per<br>gate @1 MHz<br>(mW) | Typical supply<br>voltage V<br>(range) | Introduction year | Remarks                                                                                        |

|--------|---------------------------|---------------------------|-----------------------|----------------------------------|----------------------------------------|-------------------|------------------------------------------------------------------------------------------------|

| RTL    | Resistor-transistor logic | 500                       | 4                     | 10                               | 3.3                                    | 1963              | the first CPU built from<br>integrated circuits (the Apollo<br>Guidance Computer) used<br>RTL. |

| DTL    | Diode-transistor logic    | 25                        |                       | 10                               | 5                                      | 1962              | Introduced by Signetics,<br>Fairchild 930 line became<br>industry standard in 1964             |

| CMOS   | AC/ACT                    | 3                         | 125                   | 0.5                              | 3.3 or 5 (2-6 or<br>4.5-5.5)           | 1985              | ACT has TTL Compatible levels                                                                  |

| CMOS   | НС/НСТ                    | 9                         | 50                    | 0.5                              | 5 (2-6 or<br>4.5-5.5)                  | 1982              | HCT has TTL compatible levels                                                                  |

| CMOS   | 4000B/74C                 | 30                        | 5                     | 1.2                              | 10V (3-18)                             | 1970              | Approximately half speed and power at 5 volts                                                  |

| TTL    | Original series           | 10                        | 25                    | 10                               | 5 (4.75-5.25)                          | 1964              | Several manufacturers                                                                          |

| TTL    | L                         | 33                        | 3                     | 1                                | 5 (4.75-5.25)                          | 1964              | Low power                                                                                      |

| TTL    | Н                         | 6                         | 43                    | 22                               | 5 (4.75-5.25)                          | 1964              | High speed                                                                                     |

| TTL    | S                         | 3                         | 100                   | 19                               | 5 (4.75-5.25)                          | 1969              | Schottky high speed                                                                            |

| TTL    | LS                        | 10                        | 40                    | 2                                | 5 (4.75-5.25)                          | 1976              | Low power Schottky high speed                                                                  |

| TTL    | ALS                       | 4                         | 50                    | 1.3                              | 5 (4.5-5.5)                            | 1976              | Advanced Low power<br>Schottky                                                                 |

| TTL    | F                         | 3.5                       | 100                   | 5.4                              | 5 (4.75-5.25)                          | 1979              | Fast                                                                                           |

| TTL    | AS                        | 2                         | 105                   | 8                                | 5 (4.5-5.5)                            | 1980              | Advanced Schottky                                                                              |

| TTL    | G                         | 1.5                       | 1125<br>(1.125 GHz)   |                                  | 1.65 - 3.6                             | 2004              | First GHz 7400 series logic                                                                    |

| ECL    | ECL III                   | 1                         | 500                   | 60                               | -5.2(-5.19 -<br>-5.21)                 | 1968              | Improved ECL                                                                                   |

| ECL    | MECL I                    | 8                         |                       | 31                               | -5.2                                   | 1962              | first integrated logic circuit commercially produced                                           |

| ECL    | ECL 10K                   | 2                         | 125                   | 25                               | -5.2(-5.19 -<br>-5.21)                 | 1971              | Motorola                                                                                       |

| ECL    | ECL 100K                  | 0.75                      | 350                   | 40                               | -4.5(-4.25.2)                          | 1981              |                                                                                                |

| ECL    | ECL 100KH                 | 1                         | 250                   | 25                               | -5.2(-4.95.5)                          | 1981              |                                                                                                |

#### On-chip design styles

Several techniques and design styles are primarily used in designing large single-chip application-specific integrated circuits (ASIC) and CPUs, rather than generic logic families intended for use in multi-chip applications.

These design styles can typically be divided into two main categories, static techniques and clocked dynamic techniques. (See static versus dynamic logic for some discussion on the advantages and disadvantages of each category).

#### **Static logic**

- Pulsed Static CMOS

- Differential Cascode Voltage Switch (DCVS)

- Cascode Non-Threshold Logic (CNTL)

- Pass Gate/Transmission Gate Logic: pass transistor logic (PTL)

- Complementary Pass Gate Logic (CPL)

- · Push-Pull Logic

- Output Prediction Logic (OPL)

- cascode voltage switch logic (CVSL)

#### **Dynamic logic**

- · four-phase logic

- domino logic

- · Footless Domino

- NORA/Zipper Logic

- Multiple-Output Domino

- · Compound Domino

- · Dual-Rail Domino

- Self-Resetting Domino

- Sample-Set Differential Logic

- Limited Switch Dynamic Logic

#### References

- Jacob Millman, Microelectronics Digital and Analog Circuits and Systems, McGraw-Hill Book Company, New York, 1979, ISBN 0-07-042327-X

- [2] William R. Blood Jr. (1972). MECL System Design Handbook 2nd ed. n.p.: Motorola Semiconductor Products Inc. vi.

- [3] Don Lancaster, TTL Cookbook, Howard W. Sams and Co., Indianapolis, 1975, ISBN 0-672-21035-5

- [4] RCA COSMOS

- [5] The Engineering Staff, The TTL Data Book for Design Engineers, 1st Ed., Texas Instruments, Dallas Texas, 1973, no ISBN, pages 59, 87

- [6] Paul Horowitz and Winfield Hill, *The Art of Electronics 2nd Ed.* Cambridge University Press, Cambridge, 1989 ISBN 0-521-37095-7 table 9.1 page 570

#### **Further reading**

H. P. Westman (ed), Reference Data for Radio Engineers 5th Edition, Howard W. Sams & Co., Indianapolis, 1968, no ISBN, Library of Congress Card 43-14665

#### **External links**

• What Computers are Made From (http://www.quadibloc.com/comp/cp01.htm)

# Resistor-transistor logic

**Resistor–transistor logic (RTL)** is a class of digital circuits built using resistors as the input network and bipolar junction transistors (BJTs) as switching devices. RTL is the earliest class of transistorized digital logic circuit used; other classes include diode–transistor logic (DTL) and transistor–transistor logic (TTL). The concept had been used in early computers with electron tubes, and in RTL circuits constructed with discrete components, but in 1961 it became the first digital logic family to be produced as a monolithic integrated circuit. Such were used in the US space program in 1962.

#### **Implementation**

#### **RTL** inverter

A bipolar transistor switch is the simplest RTL gate (inverter or NOT gate) implementing logical negation. <sup>[1]</sup> It consists of a common-emitter stage with a base resistor connected between the base and the input voltage source. The role of the base resistor is to expand the negligible transistor input voltage range (about 0.7 V) to the logical "1" level (about 3.5 V) by converting the input voltage into current. Its resistance is settled by a compromise: it is chosen low enough to saturate the transistor and high enough to obtain high input resistance. The role of the collector resistor is to convert the collector current into voltage; its resistance is chosen high enough to saturate the transistor and low enough to obtain low output resistance (high fan-out).

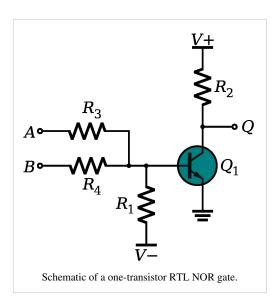

#### One-transistor RTL NOR gate

By connecting additional base resistors (R<sub>3</sub> and R<sub>4</sub>) to the inverter it is expanded to the simplest RTL NOR gate (see the figure on the right). It is an interesting fact that the basic input logical operation OR is performed by applying consecutively the two arithmetic operations addition and comparison (the input resistor network acts as a parallel *voltage summer* with equally weighted inputs and the next common-emitter transistor stage - as a *voltage comparator* with a threshold about 0.7 V). The equivalent resistance of all the resistors connected to logical "1" and the equivalent resistance of all the resistors connected to logical "0" form the two legs of a composed voltage divider driving the transistor. The base resistances and the number of the inputs are chosen (limited) so that only one logical "1" is sufficient to create

base-emitter voltage exceeding the threshold and, as a result, saturating the transistor. If all the input voltages are low (logical "0"), the transistor is cut-off. The pull-down resistor  $R_1$  provides reliable cut-off of the transistor (it is not absolutely necessary in the case of a silicon transistor). The output is inverted since the voltage drop across the collector-emitter junction of the transistor  $Q_1$  is taken as a grounded output instead the voltage drop across the floating collector resistor  $R_2$ . Thus, the analog resistive network and the analog transistor stage perform the logic function NOR.

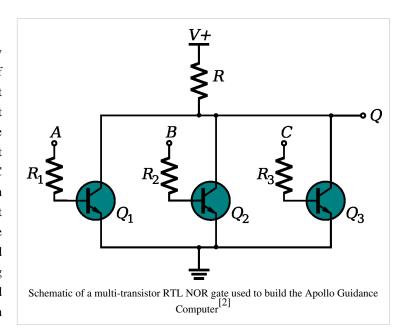

#### Multi-transistor RTL NOR gate

The limitations of the one-transistor RTL NOR gate are overcome by multi-transistor RTL implementation. It consists of a set of parallel-connected transistor switches driven by the logic inputs (see the figure on the right). In this configuration, the inputs are completely separated and the number of inputs is limited only by the small reverse saturation current of the cut-off transistors at output logical "1". The same idea is used later for building DCTL, ECL, some TTL (7450, 7460), NMOS and CMOS gates.

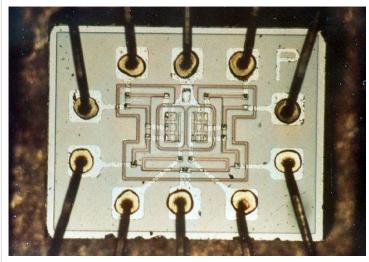

photograph of the dual NOR gate chip used to build the Apollo Guidance

Computer

#### **Advantages**

The primary advantage of RTL technology was that it involved a minimum number of which was an consideration before integrated circuit technology (that is, in circuits using discrete components), as transistors were the most expensive component to produce. Early IC logic production (such as Fairchild's in 1961) used the same approach briefly, but quickly transitioned to higher-performance circuits such as diode-transistor logic and then transistor-transistor logic (starting 1963 at Sylvania), since diodes and transistors were no more expensive than resistors in the IC.

#### Limitations

The obvious disadvantage of RTL is its high power dissipation when the transistor is switched on (the power is dissipated mainly by the base resistors connected to logical "1" and by the collector resistor). This requires that more current be supplied to and heat be removed from RTL circuits. In contrast, TTL circuits with "totem-pole" output stage

minimize

both

of

these

requirements. Another limitation of RTL was its limited fan-in: 3 inputs being the limit for many circuit designs, before it completely lost usable noise immunity. Wikipedia: Citation needed It has a low noise margin.

Lancaster says that integrated circuit RTL NOR gates (which have one transistor per input) may be constructed with "any reasonable number" of logic inputs, and gives an example of an 8-input NOR gate.

A standard integrated circuit RTL NOR gate can drive up to 3 other similar gates. Alternatively, it has enough output to drive up to 2 standard integrated circuit RTL "buffers", each of which can drive up to 25 other standard RTL NOR gates.

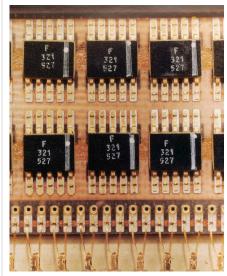

Flatpack RTL NOR gate integrated circuits in the Apollo guidance computer

#### Speeding up RTL

Various companies applied the following speed-up methods to discrete RTL.

Transistor switching speed has increased steadily from the first transistorized computers through the present. The *GE Transistor Manual* (7th ed., p. 181, or 3rd ed., p. 97 or intermediate editions) recommends gaining speed by using higher-frequency transistors, or capacitors, or a diode from base to collector (parallel negative feedback) to prevent saturation.

Placing a capacitor in parallel with each input resistor decreases the time needed for a driving stage to forward-bias a driven stage's base-emitter junction. Engineers and technicians use "RCTL" (resistor capacitor transistor logic) to designate gates equipped with "speed-up capacitors." The Lincoln Laboratory TX-0 computer's circuits included some RCTL. However, methods involving capacitors were unsuitable for integrated circuits. Wikipedia: Citation needed

Using a high collector supply voltage and diode clamping decreased collector-base and wiring capacitance charging time. This arrangement required diode clamping the collector to the design logic level. This method was also applied to discrete DTL (diode—transistor logic).

Another method that was familiar in discrete-device logic circuits used a diode and a resistor, a germanium and a silicon diode, or three diodes in a negative feedback arrangement. These diode networks known as various Baker clamps reduced the voltage applied to the base as the collector approached saturation. Because the transistor went less deeply into saturation, the transistor accumulated fewer stored charge carriers. Therefore, less time was required to clear stored charge during transistor turn off. A low-voltage diode arranged to prevent saturation of the transistor was applied to integrated logic families by using Schottky diodes, as in Schottky TTL.

#### References

[1] Resistor-Transistor Logic (http://www.play-hookey.com/digital\_electronics/rtl\_gates.html) explains the basic RTL gates and gives some useful calculations

[2] Apollo Guidance Computer schematics, Dwg. No. 2005011 (http://klabs.org/history/ech/agc\_schematics/logic/5011-1.jpg).

# **Diode-transistor logic**

"DTL" redirects here. For other uses, see DTL (disambiguation).

**Diode–transistor logic (DTL)** is a class of digital circuits that is the direct ancestor of transistor–transistor logic. It is called so because the logic gating function (e.g., AND) is performed by a diode network and the amplifying function is performed by a transistor (in contrast with RTL and TTL).

#### **Implementations**

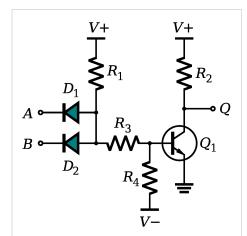

The DTL circuit shown in the picture consists of three stages: an input diode logic stage (D1, D2 and R1), an intermediate level shifting stage (R3, R4 and V-) and an output common-emitter switching-transistor stage (Q1 and R2). The two resistors R3 and R4 form a resistive summing circuit with weighted inputs that adds the negative bias voltage V- to the positive diode logic output voltage. As a result, the unipolar (positive) diode output voltage (about V+ for *logical one* and 1.0 V for *logical zero*) is converted into a bipolar voltage (a few volts above and below ground) to drive the output transistor.

The IBM 1401 (announced in 1959<sup>[1]</sup>) used DTL circuits similar to the simplified circuit. <sup>[2]</sup> IBM called the logic "complemented transistor diode logic" (CTDL). CTDL avoided the level shifting stage (R3, R4, and V–) by alternating NPN- and PNP-based gates operating on different power supply voltages. The 1401 used germanium transistors and diodes in its basic gates. The 1401 also added an inductor in series with R2. <sup>[1]</sup> The physical packaging used the IBM Standard Modular System.

Schematic of basic two-input DTL NAND gate.

R3, R4 and V- shift the positive output voltage of the input DL stage below the ground (to cut off the transistor at low input voltage).

In an integrated circuit version of the DTL gate, R3 is replaced by two level-shifting diodes connected in series. Also the bottom of R4 is connected to ground to provide bias current for the diodes and a discharge path for the transistor base. The resulting integrated circuit runs off a single power supply voltage. [3][4]

#### **Speed acceleration**

The DTL propagation delay is relatively large. When the transistor goes into saturation from all inputs being high, charge is stored in the base region. When it comes out of saturation (one input goes low) this charge has to be removed and will dominate the propagation time. A Baker clamp can be used to keep the transistor from saturating.

Another way to speed up DTL is to add a small capacitor across R3. The capacitor helps to turn off the transistor by removing the stored base charge; the capacitor also helps to turn on the transistor by increasing the initial base drive.<sup>[5]</sup>

Diodetransistor logic 11

#### **Interfacing considerations**

A major advantage over the earlier resistor-transistor logic is the increased fan-in. Alternatively, to increase fan-out of the gate, an additional transistor and diode may be used.

#### References

- [1] computermuseum.li (http://www.computermuseum.li/Testpage/IBM-1401.htm)

- [2] The IBM 1401 may have also used a current mode logic.

- [3] , page 188 states resistor is replaced with one or more diodes; figure 10-43 shows 2 diodes; cites to Schulz 1962.

- [4] ASIC world: "Diode Transistor Logic" (http://www.asic-world.com/digital/logic2.html)

- [5] . Page 32 states: "As the input signal changes, the charge on the capacitor is forced into the base of the transistor. This charge can effectively cancel the transistor stored charge, resulting in a reduction of storage time. This method is very effective if the output impedance of the preceding stage is low so that the peak reverse current into the transistor is high."

# **Emitter-coupled logic**

In electronics, emitter-coupled logic (ECL) is a high-speed integrated circuit bipolar transistor logic family. uses an overdriven differential amplifier with single-ended input and limited emitter current to avoid the saturated (fully on) region of operation and its slow turn-off behavior. As the current is steered between two legs of an emitter-coupled pair, ECL is sometimes called current-steering logic (CSL). current-mode (CML) logic current-switch emitter-follower (CSEF) logic.

In ECL, the transistors are never in saturation, the input/output voltages

have a small swing (0.8 V), the input impedance is high and the output resistance is low; as a result, the transistors change states quickly, gate delays are low, and the fanout capability is high. In addition, the essentially-constant current draw of the differential amplifiers minimises delays and glitches due to supply-line inductance and capacitance, and the complementary outputs decrease the propagation time of the whole circuit by saving additional inverters.

ECL's major disadvantage is that each gate continuously draws current, which means it requires (and dissipates) significantly more power than those of other logic families, especially when quiescent.

The equivalent of emitter-coupled logic made out of FETs is called source-coupled logic (SCFL).

A variation of ECL in which all signal paths and gate inputs are differential is known as differential current switch (DCS) logic.

#### **History**

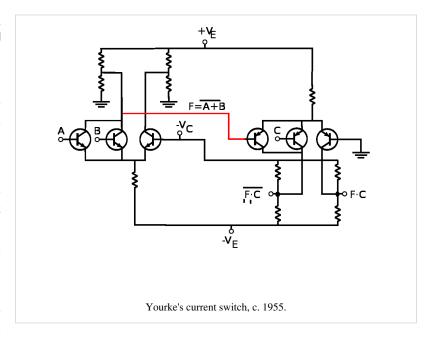

ECL was invented in August 1956 at IBM by Hannon S. Yourke. [2][3] Originally called *current-steering logic*, it was used in the Stretch, IBM 7090, and IBM 7094 computers. The logic was also called a current mode circuit. [4]

Yourke's current switch, also known as ECL, was a differential amplifier, and the input logic levels were different from the output logic levels. "In current mode operation, however, the output signal consists of voltage levels which vary about a reference level different from the input reference level." In Yourke's design, the two

logic reference levels differed by 3 volts. Consequently, two complementary versions were used: an NPN version and a PNP version. The NPN output could drive PNP inputs, and vice-versa. "The disadvantages are that more different power supply voltages are needed, and both pnp and npn transistors are required."

Instead of alternating NPN and PNP stages, another coupling method employed zener diodes and resistors to shift the output logic levels to be the same as the input logic levels.

ECL circuits in the mid-1960s through the 1990s consisted of a differential amplifier input stage to perform logic, followed by an emitter follower to drive outputs and shift the output voltages so they will be compatible with the inputs. Wikipedia: Disputed statement

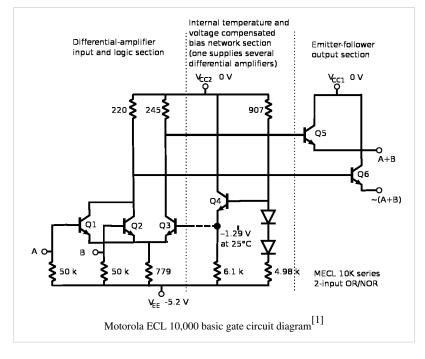

Motorola introduced their first digital monolithic integrated circuit line, MECL I, in 1962. Motorola developed several improved series, with MECL II in 1966, MECL III in 1968 with 1 nanosecond gate propagation time and 300 MHz flip-flop toggle rates, and the 10,000 series (with lower power consumption and controlled edge speeds) in 1971. [5]

The high power consumption associated with ECL has meant that it has been used mainly when high speed is a vital requirement. Older high-end mainframe computers, such as the Enterprise System/9000 members of IBM's ESA/390 computer family, used ECL as did the Cray-1; and first generation Amdahl mainframes. Current IBM mainframes use CMOS.

#### **Implementation**

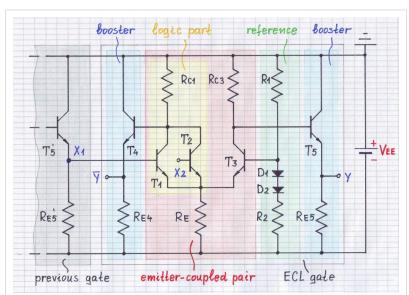

ECL is based on an emitter-coupled (long-tailed) pair, shaded red in the figure on the right. The left half of the pair (shaded yellow) consists of two parallel-connected input transistors T1 and T2 (an exemplary two-input gate is considered) implementing NOR logic. The base voltage of the right transistor T3 is held fixed by a reference voltage source, shaded light green: the voltage divider with a diode thermal compensation (R1, R2, D1 and D2) and sometimes a buffering emitter follower (not shown on the picture); thus the emitter voltages are kept relatively steady. As a result, the common emitter resistor R<sub>E</sub> acts nearly as a current source. The output voltages at the collector load resistors  $R_{C1}$  and  $R_{C3}$  are shifted and buffered to the inverting and non-inverting

The picture represents a typical ECL circuit diagram based on Motorola's MECL. In this schematic, transistor T5' represents the output transistor of a previous ECL gate that provides a logic signal to input transistor T1 of an OR/NOR gate whose other input is at T2 and has outputs Y and Y. Additional pictures illustrate the circuit operation by visualizing the voltage relief and current topology at low input voltage (logical "0"), during the transition and at high input voltage (logical "1").

outputs by the emitter followers T4 and T5 (shaded blue). The output emitter resistors  $R_{E4}$  and  $R_{E5}$  do not exist in all versions of ECL. In some cases 50  $\Omega$  line termination resistors connected between the bases of the input transistors and -2 V act as emitter resistors.<sup>[6]</sup>

#### **Operation**

The ECL circuit operation is considered below with assumption that the input voltage is applied to T1 base, while T2 input is unused or a logical "0" is applied.

During the transition, the core of the circuit – the emitter-coupled pair (T1 and T3) – acts as a differential amplifier with single-ended input. The "long-tail" current source ( $R_E$ ) sets the total current flowing through the two legs of the pair. The input voltage controls the current flowing through the transistors by sharing it between the two legs, steering it all to one side when not near the switching point. The gain is higher than at the end states (see below) and the circuit switches quickly.

At low input voltage (logical "0") or at high input voltage (logical "1") the differential amplifier is overdriven. The one transistor (T1 or T3) is cut-off and the other (T3 or T1) is in active linear region acting as a common-emitter stage with emitter degeneration that takes all the current, starving the other cut-off transistor.

The active transistor is loaded with the relatively high emitter resistance  $R_{\rm E}$  that introduces a significant negative feedback (emitter degeneration). To prevent saturation of the active transistor so that the diffusion time that slows the recovery from saturation will not be involved in the logic delay, the emitter and collector resistances are chosen such that at maximum input voltage some voltage is left across the transistor. The residual gain is low  $(K = R_{\rm C}/R_{\rm E} < 1)$ . The circuit is insensitive to the input voltage variations and the transistor stays firmly in active linear region. The input resistance is high because of the series negative feedback.

The cut-off transistor breaks the connection between its input and output. As a result, its input voltage does not affect the output voltage. The input resistance is high again since the base-emitter junction is cut-off.

#### **Characteristics**

Other noteworthy characteristics of the ECL family include the fact that the large current requirement is approximately constant, and does not depend significantly on the state of the circuit. This means that ECL circuits generate relatively little power noise, unlike many other logic types which typically draw far more current when switching than quiescent, for which power noise can become problematic. In cryptographic applications, ECL circuits are also less susceptible to side channel attacks such as differential power analysis.

The propagation time for this arrangement can be less than a nanosecond, making it for many years the fastest logic family.

#### Power supplies and logic levels

The ECL circuits usually operate with negative power supplies (positive end of the supply is connected to ground) in contrast to other logic families in which negative end of the supply is grounded. This is done mainly to minimize the influence of the power supply variations on the logic levels as ECL is more sensitive to noise on the  $V_{CC}$  and relatively immune to noise on  $V_{EE}$ . Because ground should be the most stable voltage in a system, ECL is specified with a positive ground. In this connection, when the supply voltage varies, the voltage drops across the collector resistors change slightly (in the case of emitter constant current source, they do not change at all). As the collector resistors are firmly "tied up" to ground, the output voltages "move" slightly (or not at all). If the negative end of the power supply was grounded, the collector resistors would be attached to the positive rail. As the constant voltage drops across the collector resistors change slightly (or not at all), the output voltages follow the supply voltage variations and the two circuit parts act as constant current level shifters. In this case, the voltage divider R1-R2 compensates the voltage variations to some extent. The positive power supply has another disadvantage - the output voltages will vary slightly ( $\pm 0.4 \text{ V}$ ) against the background of high constant voltage ( $\pm 3.9 \text{ V}$ ). Another reason for using a negative power supply is protection of the output transistors from an accidental short circuit developing between output and ground ground [8] (but the outputs are not protected from a short circuit with the negative rail).

The value of the supply voltage is chosen so that a sufficient current to flow through the compensating diodes D1 and D2 and the voltage drop across the common emitter resistor  $R_{\rm F}$  to be adequate.

ECL circuits available on the open market usually operated with logic levels incompatible with other families. This meant that interoperation between ECL and other logic families, such as the popular TTL family, required additional interface circuits. The fact that the high and low logic levels are relatively close meant that ECL suffers from small noise margins, which can be troublesome.

At least one manufacturer, IBM, made ECL circuits for use in the manufacturer's own products. The power supplies were substantially different from those used in the open market.

Positive emitter-coupled logic (PECL) is a further development of ECL using a positive 5V supply instead of a negative 5.2V supply. Low-voltage positive emitter-coupled logic (LVPECL) is a power optimized version of PECL, using a positive 3.3V instead of 5V supply. PECL and LVPECL are differential signaling systems, and are mainly used in high speed and clock distribution circuits.

Logic levels:<sup>[9]</sup>

| Type   | V <sub>ee</sub> | V <sub>low</sub> | V <sub>high</sub> | V <sub>cc</sub> | V <sub>cm</sub> |

|--------|-----------------|------------------|-------------------|-----------------|-----------------|

| PECL   | GND             | 3.4 V            | 4.2 V             | 5.0 V           |                 |

| LVPECL | GND             | 1.6 V            | 2.4 V             | 3.3 V           | 2.0 V           |

#### References

- [1] Original drawing based on William R. Blood Jr. (1972). MECL System Design Handbook 2nd ed. n.p.: Motorola Semiconductor Products. 1.

- [2] Early Transistor History at IBM (http://semiconductormuseum.com/Transistors/IBM/OralHistories/Yourke/Yourke\_Index.htm)

- [3] . Yourke's circuits used commercial transistors and had an average gate delay of 12 ns.

- [4] , p. 37.

- [5], pp vi-vii

- [6] Blood, W.R. (1972). MECL System Design Handbook 2nd ed. n.p.: Motorola Semiconductor Products Inc. p. 3.

- [7] Electronic Materials Handbook: Packaging (page 163) (http://books.google.bg/books?id=c2YxCCaM9RIC&pg=PA163&lpg=PA163&dpg=PA163&dpg=5.2+V+power+supply+voltage+why&source=bl&ots=0eJCoqu1gf&sig=Wb9Cfd8EGOfqIOl\_oNjdhVKUYdQ&hl=en&ei=ek\_ESub7LYuz4QbApdw\_&sa=X&oi=book\_result&ct=result&resnum=6#v=onepage&q=5.2 V power supply voltage why&f=false) by Merrill L. Minges, ASM International. Handbook Committee

- [8] Modern digital electronics By R P Jain (http://books.google.com/books?id=dnq3HmDN1ZAC&pg=RA1-PA110&lpg=RA1-PA110&dq=emitter-coupled+logic&source=bl&ots=hcQdJqyQXW&sig=THPHTWMe1Fr-XgMmWN-J1S8Gi\_Y&hl=en&ei=QvzCSq24KJS24QadxdzTDQ&sa=X&oi=book\_result&ct=result&resnum=4#v=onepage&q=emitter-coupled logic&f=false) (page 111)

- [9] Interfacing Between LVPECL, VML, CML and LVDS Levels (http://focus.ti.com/lit/an/slla120/slla120.pdf)

- US 2964652 (http://worldwide.espacenet.com/textdoc?DB=EPODOC&IDX=US2964652), Yourke, Hannon S., "Transistor Switching Circuits", published November 15, 1956, issued December 13,1960

- Yourke, Hannon S. (September 1957). "Millimicrosecond Transistor Current Switching Circuits". *IRE Transactions on Circuit Theory* 4 (3): 236–240. doi: 10.1109/TCT.1957.1086377 (http://dx.doi.org/10.1109/TCT.1957.1086377). ISSN 0096-2007 (http://www.worldcat.org/issn/0096-2007).

#### **External links**

Motorola MECL logic family datasheets, 1963 (http://www.wps.com/archives/solid-state-datasheets/ Motorola/MECL/index.html)

# **Gunning transceiver logic**

Gunning transceiver logic or GTL is a type of logic signaling used to drive electronic backplane buses. It has a voltage swing between 0.4 volts and 1.2 volts—much lower than that used in TTL and CMOS logic—and symmetrical parallel resistive termination. The maximum signaling frequency is specified to be 100 MHz, although some applications use higher frequencies. GTL is defined by JEDEC standard JESD 8-3 (1993) and was invented by William Gunning while working for Xerox at the Palo Alto Research Center.

All Intel front-side buses use GTL. As of 2008, GTL in these FSBs has a maximum frequency of 1.6 GHz. The front-side bus of the Intel Pentium Pro, Pentium II and Pentium III microprocessors uses GTL+ (or GTLP) developed by Fairchild Semiconductor, an upgraded version of GTL which has defined slew rates and higher voltage levels. AGTL+ stands for either assisted Gunning transceiver logic or advanced Gunning transceiver logic. These are GTL signaling derivatives used by Intel microprocessors.

#### References

- "GTLP vs. GTL: A Performance Comparison from a System Perspective" (http://www.fairchildsemi.com/an/AN/AN-1070.pdf), AN-1070 (Fairchild Semiconductor), December 2000

- "GTL/BTL: A Low-Swing Solution for High-Speed Digital Logic" (http://focus.ti.com/lit/an/scea003a/scea003a.pdf), Application Note (Texas Instruments), 1997

- JEDEC Standard JESD8-3A, Gunning Transceiver Logic (GTL) Low-Level, High Speed Interface Standard for Digital Integrated Circuits (http://www.jedec.org/sites/default/files/docs/JESD8-3A.pdf), JEDEC, May 2007

# Transistor-transistor logic

**Transistor–transistor logic** (**TTL**) is a class of digital circuits built from bipolar junction transistors (BJT) and resistors. It is called *transistor–transistor logic* because both the logic gating function (e.g., AND) and the amplifying function are performed by transistors (contrast with RTL and DTL).

TTL is notable for being a widespread integrated circuit (IC) family used in many applications such as computers, industrial controls, test equipment and instrumentation, consumer electronics, synthesizers, etc. The designation *TTL* is sometimes used to mean TTL-compatible logic levels, even when not associated directly with TTL integrated circuits, for example as a label on the inputs and outputs of electronic instruments.<sup>[1]</sup>

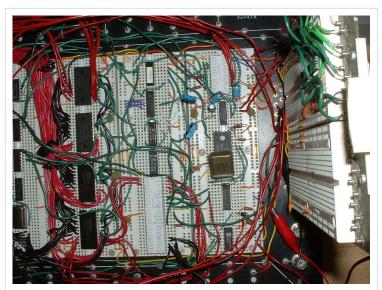

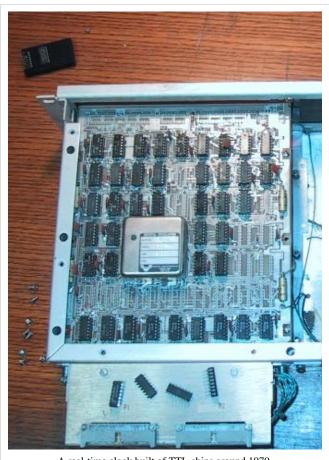

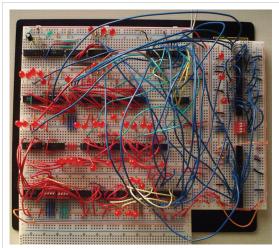

A Motorola 68000-based computer with various TTL chips mounted on breadboards.

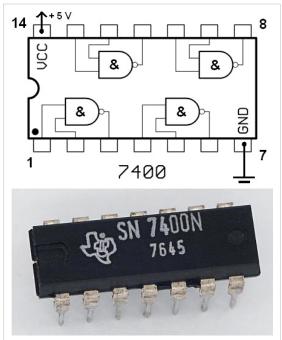

After their introduction in integrated circuit form in 1963 by Sylvania, TTL integrated circuits were manufactured by several semiconductor companies, with the 7400 series by Texas Instruments becoming particularly popular. TTL

manufacturers offered a wide range of logic gate, flip-flops, counters, and other circuits. Several variations from the original bipolar TTL concept were developed, giving circuits with higher speed or lower power dissipation to allow optimization of a design. TTL circuits simplified design of systems compared to earlier logic families, offering superior speed to resistor-transistor logic (RTL) and easier design layout than emitter-coupled logic (ECL). The design of the input and outputs of TTL gates allowed many elements to be interconnected.

TTL became the foundation of computers and other digital electronics. Even after much larger scale integrated circuits made multiple-circuit-board processors obsolete, TTL devices still found extensive use as the "glue" logic interfacing more densely integrated components. TTL devices were originally made in ceramic and plastic dual-in-line (DIP) packages, and flat-pack form. TTL chips are now also made in surface-mount packages. Successors to the original bipolar TTL logic often are interchangeable in function with the original circuits, but with improved speed or lower power dissipation.

#### History

TTL was invented in 1961 by James L. Buie of TRW, "particularly suited to the newly developing integrated circuit design technology", and it was originally named transistor-coupled transistor logic (TCTL). [2] The first commercial integrated-circuit TTL devices were manufactured by Sylvania in 1963, called the Sylvania Universal High-Level Logic family (SUHL).<sup>[3]</sup> The Sylvania parts were used in the controls of the Phoenix missile. TTL became popular with electronic systems designers after Texas Instruments introduced the 5400 series of ICs, with military temperature range, in 1964 and the later 7400 series, specified over a narrower range, and with inexpensive plastic packages in 1966.<sup>[4]</sup>

The Texas Instruments 7400 family became an industry standard. Compatible parts were made by Motorola, AMD, Fairchild, Intel, Intersil, Signetics, Mullard, Siemens, SGS-Thomson and National Semiconductor, [5][6] and many other companies, even in the Eastern Bloc (Soviet Union, GDR, Poland, Bulgaria). Wikipedia: Citation needed Not only did others make compatible TTL parts, but compatible parts were made using many other

A real-time clock built of TTL chips around 1979.

circuit technologies as well. At least one manufacturer, IBM, produced non-compatible TTL circuits for its own use; IBM used the technology in the IBM System/38, IBM 4300, and IBM 3081. [7]

The term "TTL" is applied to many successive generations of bipolar logic, with gradual improvements in speed and power consumption over about two decades. The most recently introduced familyWikipedia:Citation needed, 74AS/ALS Advanced Schottky, was introduced in 1985. [8] As of 2008, Texas Instruments continues to supply the more general-purpose chips in numerous obsolete technology families, albeit at increased prices. Typically, TTL chips integrate no more than a few hundred transistors each. Functions within a single package generally range from a few logic gates to a microprocessor bit-slice. TTL also became important because its low cost made digital

techniques economically practical for tasks previously done by analog methods. [9]

The Kenbak-1, ancestor to the first personal computers, used TTL for its CPU instead of a microprocessor chip, which was not available in 1971. The 1973 Xerox Alto and 1981 Star workstations, which introduced the graphical user interface, used TTL circuits integrated at the level of ALUs and bitslices, respectively. Most computers used TTL-compatible "glue logic" between larger chips well into the 1990s. Until the advent of programmable logic, discrete bipolar logic was used to prototype and emulate microarchitectures under development.

#### **Implementation**

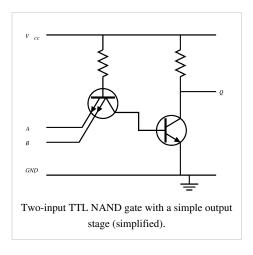

#### **Fundamental TTL gate**

TTL inputs are the emitters of a multiple-emitter transistor. This IC structure is functionally equivalent to multiple transistors where the bases and collectors are tied together.<sup>[11]</sup> The output is buffered by a common emitter amplifier.

Inputs both logical ones. When all the inputs are held at high voltage, the base—emitter junctions of the multiple-emitter transistor are reverse-biased. Unlike DTL, a small "collector" current (approximately  $10\mu A$ ) is drawn by each of the inputs. This is because the transistor is in reverse-active mode. An approximately constant current flows from the positive rail, through the resistor and into the base of the multiple emitter transistor. [12] This current passes through the base-emitter junction of the output transistor, allowing it to conduct and pulling the output voltage low (logical zero).

An input logical zero. Note that the base-collector junction of the multiple-emitter transistor and the base-emitter junction of the output transistor are in series between the bottom of the resistor and ground. If one input voltage becomes zero, the corresponding base-emitter junction of the multiple-emitter transistor is in parallel with these two junctions. A phenomenon called current steering means that when two voltage-stable elements with different threshold voltages are connected in parallel, the current flows through the path with the smaller threshold voltage. As a result, no current flows through the base of the output transistor, causing it to stop conducting and the output voltage becomes high (logical one). During the transition the input transistor is briefly in its active region; so it draws a large current away from the base of the output transistor and thus quickly discharges its base. This is a critical advantage of TTL over DTL that speeds up the transition over a diode input structure. [13]

The main disadvantage of TTL with a simple output stage is the relatively high output resistance at output logical "1" that is completely determined by the output collector resistor. It limits the number of inputs that can be connected (the fanout). Some advantage of the simple output stage is the high voltage level (up to  $V_{CC}$ ) of the output logical "1" when the output is not loaded.

A common variation omits the collector resistor of the output transistor, making an open collector output. This allows the designer to fabricate logic by connecting the open collector outputs of several logic gates together and providing a single external pull-up resistor. If any of the logic gates becomes logic low (transistor conducting), the combined output will be low. Examples of this type of gate are the 7401<sup>[14]</sup> and 7403 series.

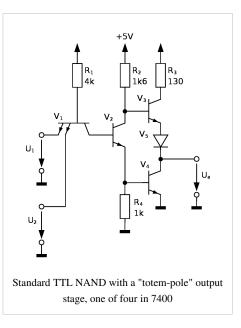

#### TTL with a "totem-pole" output stage

To solve the problem with the high output resistance of the simple output stage the second schematic adds to this a "totem-pole" ("push-pull") output. It consists of the two n-p-n transistors  $V_3$  and  $V_4$ , the "lifting" diode  $V_5$  and the current-limiting resistor  $R_3$  (see the figure on the right). It is driven by applying the same *current steering* idea as above.

When  $V_2$  is "off",  $V_4$  is "off" as well and  $V_3$  operates in active region as a voltage follower producing high output voltage (logical "1"). When  $V_2$  is "on", it activates  $V_4$ , driving low voltage (logical "0") to the output.  $V_2$  and  $V_4$  collector—emitter junctions connect  $V_4$  base—emitter junction in parallel to the series-connected  $V_3$  base—emitter and  $V_5$  anode—cathode junctions.  $V_3$  base current is deprived; the transistor turns "off" and it does not impact on the output. In the middle of the transition, the resistor  $V_3$  limits the current flowing directly through the series connected transistor  $V_3$ , diode  $V_5$  and transistor  $V_4$  that are all conducting. It also limits the output current in

the case of output logical "1" and short connection to the ground. The strength of the gate may be increased without proportionally affecting the power consumption by removing the pull-up and pull-down resistors from the output stage. [15][16]

The main advantage of TTL with a "totem-pole" output stage is the low output resistance at output logical "1". It is determined by the upper output transistor  $V_3$  operating in active region as a voltage follower. The resistor  $R_3$  does not increase the output resistance since it is connected in the  $V_3$  collector and its influence is compensated by the negative feedback. A disadvantage of the "totem-pole" output stage is the decreased voltage level (no more than 3.5 V) of the output logical "1" (even, if the output is unloaded). The reason of this reduction are the voltage drops across the  $V_3$  base-emitter and  $V_5$  anode-cathode junctions.

#### **Interfacing considerations**

Like DTL, TTL is a *current-sinking logic* since a current must be drawn from inputs to bring them to a logic 0 level. At low input voltage, the TTL input sources current which must be absorbed by the previous stage. The maximum value of this current is about 1.6 mA for a standard TTL gate. The input source has to be low-resistive enough (< 500  $\Omega$ ) so that the flowing current creates only a negligible voltage drop (< 0.8 V) across it, for the input to be considered as a logical "0". TTL inputs are sometimes simply left floating to provide a logical "1", though this usage is not recommended.

Standard TTL circuits operate with a 5-volt power supply. A TTL input signal is defined as "low" when between 0 V and 0.8 V with respect to the ground terminal, and "high" when between 2.2 V and 5 V<sup>[18]</sup> and if a voltage signal ranges between 0.8 volts and 2 volts were to be sent into the input of a TTL gate, there would be no certain response from the gate and therefore it is considered "uncertain" (precise logic levels vary slightly between sub-types and by temperature). TTL outputs are typically restricted to narrower limits of between 0 V and 0.4 V for a "low" and between 2.6 V and 5 V for a "high", providing 0.4V of noise immunity. Standardization of the TTL levels was so ubiquitous that complex circuit boards often contained TTL chips made by many different manufacturers selected for availability and cost, compatibility being assured; two circuit board units off the same assembly line on different successive days or weeks might have a different mix of brands of chips in the same positions on the board; repair was possible with chips manufactured years (sometimes over a decade) later than original components. Within usefully broad limits, logic gates could be treated as ideal Boolean devices without concern for electrical limitations.

In some cases (e.g., when the output of a TTL logic gate needs to be used for driving the input of a CMOS gate), the voltage level of the "totem-pole" output stage at output logical "1" can be increased up to  $V_{CC}$  by connecting an external resistor between the  $V_3$  collector and the positive rail. It pulls up the  $V_5$  cathode and cuts-off the diode. [19] However, this technique actually converts the sophisticated "totem-pole" output into a simple output stage having significant output resistance when driving a high level (determined by the external resistor).

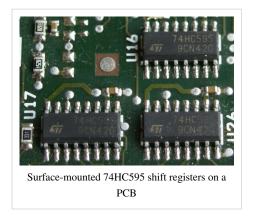

#### **Packaging**

Like most integrated circuits of the period 1965–1990, TTL devices are usually packaged in through-hole, dual in-line packages with between 14 and 24 lead wires, usually made of epoxy plastic (PDIP) or sometimes of ceramic (CDIP). Beam-lead chip dice without packages were made for assembly into larger arrays as hybrid integrated circuits. Parts for military and aerospace applications were packaged in flat packs, a form of surface-mount package, with leads suitable for welding or soldering to printed circuit boards. Today, many TTL-compatible devices are available in surface-mount packages, which are available in a wider array of types than through-hole packages.

TTL is particularly well suited to bipolar integrated circuits because additional inputs to a gate merely required additional emitters on a shared base region of the input transistor. If individually packaged transistors were used, the cost of all the transistors would discourage one from using such an input structure. But in an integrated circuit, the additional emitters for extra gate inputs add only a small area.

#### Comparison with other logic families

Main article: Logic family

TTL devices consume substantially more power than equivalent CMOS devices at rest, but power consumption does not increase with clock speed as rapidly as for CMOS devices. [20] Compared to contemporary ECL circuits, TTL uses less power and has easier design rules but is substantially slower. Designers can combine ECL and TTL devices in the same system to achieve best overall performance and economy, but level-shifting devices are required between the two logic families. TTL is less sensitive to damage from electrostatic discharge than early CMOS devices.

Due to the output structure of TTL devices, the output impedance is asymmetrical between the high and low state, making them unsuitable for driving transmission lines. This drawback is usually overcome by buffering the outputs with special line-driver devices where signals need to be sent through cables. ECL, by virtue of its symmetric low-impedance output structure, does not have this drawback.

The TTL "totem-pole" output structure often has a momentary overlap when both the upper and lower transistors are conducting, resulting in a substantial pulse of current drawn from the power supply. These pulses can couple in unexpected ways between multiple integrated circuit packages, resulting in reduced noise margin and lower performance. TTL systems usually have a decoupling capacitor for every one or two IC packages, so that a current pulse from one TTL chip does not momentarily reduce the supply voltage to another.

Several manufacturers now supply CMOS logic equivalents with TTL-compatible input and output levels, usually bearing part numbers similar to the equivalent TTL component and with the same pinouts. For example, the 74HCT00 series provides many drop-in replacements for bipolar 7400 series parts, but uses CMOS technology.

#### **Sub-types**

Successive generations of technology produced compatible parts with improved power consumption or switching speed, or both. Although vendors uniformly marketed these various product lines as TTL with Schottky diodes, some of the underlying circuits, such as used in the LS family, could rather be considered DTL.<sup>[21]</sup>

Variations of and successors to the basic TTL family, which has a typical gate propagation delay of 10ns and a power dissipation of 10 mW per gate, for a power-delay product (PDP) or switching energy of about 100 pJ, include:

- Low-power TTL (L), which traded switching speed (33ns) for a reduction in power consumption (1 mW) (now essentially replaced by CMOS logic)

- High-speed TTL (H), with faster switching than standard TTL (6ns) but significantly higher power dissipation (22 mW)

- Schottky TTL (S), introduced in 1969, which used Schottky diode clamps at gate inputs to prevent charge storage and improve switching time. These gates operated more quickly (3ns) but had higher power dissipation (19 mW)

- Low-power Schottky TTL (LS) used the higher resistance values of low-power TTL and the Schottky diodes to provide a good combination of speed (9.5ns) and reduced power consumption (2 mW), and PDP of about 20 pJ. Probably the most common type of TTL, these were used as glue logic in microcomputers, essentially replacing the former H, L, and S sub-families.

- Fast (F) and Advanced-Schottky (AS) variants of LS from Fairchild and TI, respectively, circa 1985, with "Miller-killer" circuits to speed up the low-to-high transition. These families achieved PDPs of 10 pJ and 4 pJ, respectively, the lowest of all the TTL families.

- Low-voltage TTL (LVTTL) for 3.3-volt power supplies and memory interfacing.

Most manufacturers offer commercial and extended temperature ranges: for example Texas Instruments 7400 series parts are rated from 0 to 70 °C, and 5400 series devices over the military-specification temperature range of –55 to +125 °C.

Special quality levels and high-reliability parts are available for military and aerospace applications.

Radiation-hardened devices are offered for space applications.

#### **Applications**

Before the advent of VLSI devices, TTL integrated circuits were a standard method of construction for the processors of mini-computer and mainframe processors; such as the DEC VAX and Data General Eclipse, and for equipment such as machine tool numerical controls, printers and video display terminals. As microprocessors became more functional, TTL devices became important for "glue logic" applications, such as fast bus drivers on a motherboard, which tie together the function blocks realized in VLSI elements.

#### **Analog applications**

While originally designed to handle logic-level digital signals, a TTL inverter can be biased as an analog amplifier. Connecting a resistor between the output and the input biases the TTL element as a negative feedback amplifier. Such amplifiers may be useful to convert analog signals to the digital domain but would not ordinarily be used where analog amplification is the primary purpose. [22] TTL inverters can also be used in crystal oscillators where their analog amplification ability is significant.

#### **Notes**

- [1] Eren, H., 2003.

- [2] Buie, J., 1966.

- [3] The Computer History Museum, 2007.

- [4] Bo Lojek, History of semiconductor engineering Springer, 2006 ISBN 3-540-34257-5, pages 212-215

- [5] Engineering Staff, 1973.

- [6] L.W. Turner, (ed), Electronics Engineer's Reference Book, 4th ed. Newnes-Butterworth, London 1976 ISBN 0408001682

- [7] Pittler, Powers, and Schnabel 1982, 5

- [8] Texas Instruments, 1985

- [9] Lancaster, 1975, preface.

- [10] Klein, 2008.

- [11] Electronic Principles Physics, Models, and Circuits, first edition 1969, Gray and Searle, page 870

- [12] Buie, J., 1966, column 4.

- [13] Millman 1979 pg. 147.

- [14] SN7401 datasheet (http://www.ti.com/lit/gpn/sn7401) Texas Instruments

- [15] Transistor-Transistor Logic (TTL), 2005, p. 1.

- [16] Tala, 2006.

- [17] SN7400 datasheet (http://focus.ti.com/general/docs/lit/getliterature.tsp?genericPartNumber=sn74ls00&fileType=pdf&track=no) -Texas Instruments

- [18] TTL logic levels

- [19] TTL-to-CMOS Interfacing Techniques (http://ecelab.com/interfacing-ttl-cmos.htm)

- [20] Paul Horowitz and Winfield Hill, *The Art of Electronics 2nd Ed.* Cambridge University Press, Cambridge, 1989 ISBN 0-521-37095-7 page 970 ... CMOS devices consume power proportional to ther switching frequency... At their maximum operating frequency they may use more power than equivalent bipolar TTL devices.

- [21] Ayers, n.d.

- [22] Wobschall, 1987, pp. 209-211.

#### References

- Ayers, J. UConn EE 215 notes for lecture 4. (http://people.seas.harvard.edu/~jones/es154/lectures/lecture\_7/pdfs/215ln04.pdf) Harvard University faculty web page. Archive of web page from University of Connecticut. n.d. Retrieved 17 September 2008.

- US 3283170 (http://worldwide.espacenet.com/textdoc?DB=EPODOC&IDX=US3283170), James L. Buie,

"Coupling transistor logic and other circuits", issued 1966-11-01, assigned to TRW Semiconductors, Inc.

- The Computer History Museum. 1963 Standard Logic Families Introduced. (http://www.computerhistory.org/semiconductor/timeline/1963-TTL.html) 2007. Retrieved 16 April 2008.

- Engineering Staff. The TTL Data Book for Design Engineers. 1st Ed. Dallas: Texas Instruments. 1973.

- Eren, H. Electronic Portable Instruments: Design and Applications. CRC Press. 2003. ISBN 0-8493-1998-6.

Google preview (http://books.google.com/books?id=xwfpvzvNTr4C&pg=PA353&dq=intitle:instruments+intitle:electronic+ttl-outputs&lr=&as\_brr=3&ei=Hz6wSKHHDJzOswO6uI3ABA&sig=ACfU3U2jAUGIInuz8NEKLkToZYAqYJTirA#PPT1,M1) available.

- Fairchild Semiconductor. An Introduction to and Comparison of 74HCT TTL Compatible CMOS Logic (Application Note 368). (http://www.fairchildsemi.com/an/AN/AN-368.pdf) 1984. (for relative ESD sensitivity of TTL and CMOS.)

- Horowitz, P. and Winfield Hill, W. The Art of Electronics. 2nd Ed. Cambridge University Press. 1989. ISBN 0-521-37095-7

- Klein, E. Kenbak-1. (http://www.vintage-computer.com/kenbak-1.shtml) Vintage-Computer.com. 2008.

- Lancaster, D. TTL Cookbook. Indianapolis: Howard W. Sams and Co. 1975. ISBN 0-672-21035-5.

- Millman, J. Microelectronics Digital and Analog Circuits and Systems. New York:McGraw-Hill Book Company. 1979. ISBN 0-07-042327-X

- Pittler, M.S., Powers, D.M., and Schnabel, D.L. System development and technology aspects of the IBM 3081

Processor Complex. (http://www.research.ibm.com/journal/rd/261/ibmrd2601B.pdf) IBM Journal of

- Research and Development. 26 (1982), no. 1:2-11.

- Standard TTL logic levels. (http://www.twysted-pair.com/74xx.htm) n.d. Twisted Pair Software.

- Tala, D. K. *Digital Logic Gates Part-V*. (http://www.asic-world.com/digital/gates5.html) asic-world.com. 2006.

- Texas Instruments. *Advanced Schottky Family*. (http://focus.ti.com/lit/an/sdaa010/sdaa010.pdf) 1985. Retrieved 17 September 2008.

- *Transistor—Transistor Logic (TTL)*. (http://www.siliconfareast.com/ttl.htm) siliconfareast.com. 2005. Retrieved 17 September 2008.

- Wobschall, D. Circuit Design for Electronic Instrumentation: Analog and Digital Devices from Sensor to Display. 2d edition. New York: McGraw Hill 1987. ISBN 0-07-071232-8

#### **External links**

- Texas Instruments logic family application notes (http://focus.ti.com/logic/docs/techdocs. tsp?sectionId=452&tabId=1989&techDoc=1&familyId=1&documentCategoryId=1&viewType=1&techFamId=0)

- TTL NAND and AND gates (http://ibiblio.org/kuphaldt/electricCircuits/Digital/DIGI\_3.html#xtocid653312) from *Lessons In Electric Circuits* by Tony Kuphaldt

# **PMOS logic**

P-type metal-oxide-semiconductor logic uses p-channel metal-oxide-semiconductor field effect transistors (MOSFETs) to implement logic gates and other digital circuits. PMOS transistors operate by creating an inversion layer in an n-type transistor body. This inversion layer, called p-channel, can conduct holes between p-type "source" and "drain" terminals.

The p-channel is created by applying voltage to the third terminal

called gate. Like other MOSFETs, PMOS transistors have four modes of operation: cut-off (or subthreshold), triode, saturation (sometimes called active), and velocity saturation.

The p-type MOSFETs are arranged in a so-called "pull-up network" (PUN) between the logic gate output and positive supply voltage, while a resistor is placed between the logic gate output and the negative supply voltage. The circuit is designed such that if the desired output is high, then the PUN will be active, creating a current path between the positive supply and the output.

While PMOS logic is easy to design and manufacture (a MOSFET can be made to operate as a resistor, so the whole circuit can be made with PMOS FETs), it has several shortcomings as well. The worst problem is that a DC current flows through a PMOS logic gate when the PUN is active, that is whenever the output is high. This leads to static power dissipation even when the circuit sits idle.

Also, PMOS circuits are slow to transition from high to low. When transitioning from low to high, the transistors provide low resistance, and the capacitative charge at the output accumulates very quickly (similar to charging a capacitor through a very low resistor). But the resistance between the output and the negative supply rail is much greater, so the high to low transition takes longer (similar to discharge a capacitor through a high resistor value). Using a resistor of lower value will speed up the process but also increases static power dissipation.

Additionally, the asymmetric input logic levels make PMOS circuits susceptible to noise.

PMOS logic 24

Though initially easier to manufacture, PMOS logic was later supplanted by NMOS logic because NMOS is faster than PMOS. Modern fabs use CMOS, which uses both PMOS and NMOS transistors together. Static CMOS logic leverages the advantages of both by using NMOS and PMOS together in the wafer.

# **NMOS** logic

**N-type metal-oxide-semiconductor logic** uses n-type metal-oxide-semiconductor field effect transistors (MOSFETs) to implement logic gates and other digital circuits. NMOS transistors have four modes of operation: cut-off (or sub-threshold), triode, saturation (sometimes called active), and velocity saturation.

The n-type MOSFETs are arranged in a so-called "pull-down network" (PDN) between the logic gate output and negative supply voltage, while a resistor is placed between the logic gate output and the positive supply voltage. The circuit is designed such that if the desired output is low, then the PDN will be active, creating a current path between the negative supply and the output.

As an example, here is a NOR gate in NMOS logic. If either input A or input B is high (logic 1, = True), the respective MOS transistor acts as a very low resistance between the output and the negative supply, forcing the output to be low (logic 0, = False). When both A and B are high, both transistors are conductive, creating an even lower resistance path to ground. The only case where the output is high is when both transistors are off, which occurs only when both A and B are low, thus satisfying the truth table of a NOR gate:

| A | В | A NOR B |

|---|---|---------|

| 0 | 0 | 1       |

| 0 | 1 | 0       |

| 1 | 0 | 0       |

| 1 | 1 | 0       |

A MOSFET can be made to operate as a resistor, so the whole circuit can be made with n-channel MOSFETs only. For many years, this made NMOS circuits much faster than comparable PMOS and CMOS circuits, which had to use much slower p-channel transistors. It was also easier to manufacture NMOS than CMOS, as the latter has to implement p-channel transistors in special n-wells on the p-substrate. The major problem with NMOS (and most other logic families) is that a DC current must flow through a logic gate even when the output is in a steady state (low in the case of NMOS). This means static power dissipation, i.e. power drain even when the circuit is not switching. This is a similar situation to the modern high speed, high density CMOS circuits (microprocessors etc.) which also has significant static current draw, although this is due to leakage, not bias. However, older and/or slower static CMOS circuits used for ASICs, SRAM etc., typically have very low static power consumption.

NMOS logic 25

Also, NMOS circuits are slow to transition from low to high. When transitioning from high to low, the transistors provide low resistance, and the capacitative charge at the output drains away very quickly (similar to discharging a capacitor through a very low resistor). But the resistance between the output and the positive supply rail is much greater, so the low to high transition takes longer (similar to charging a capacitor through a high value resistor). Using a resistor of lower value will speed up the process but also increases static power dissipation. However, a better (and the most common) way to make the gates faster is to use depletion-mode transistors instead of enhancement-mode transistors as loads. This is called depletion-load NMOS logic.

Additionally, just like in DTL, TTL and ECL etc., the asymmetric input logic levels make NMOS circuits somewhat susceptible to noise. These disadvantages are why the CMOS logic now has supplanted most of these types in most high-speed digital circuits such as microprocessors (despite the fact that CMOS was originally very slow).

### **CMOS**

For other uses, see CMOS (disambiguation).

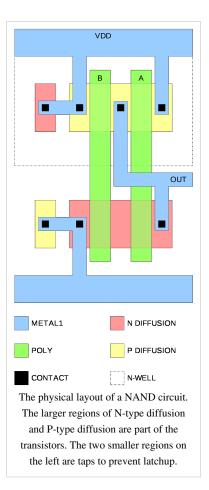

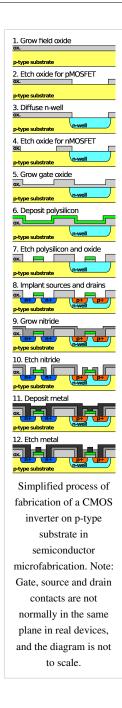

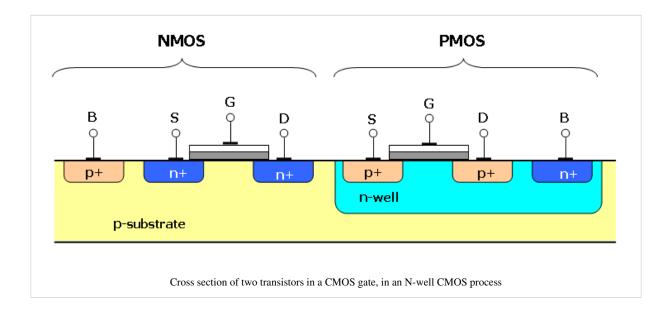

Complementary metal—oxide—semiconductor (CMOS) /'si:mps/ is a technology for constructing integrated circuits. CMOS technology is used in microprocessors, microcontrollers, static RAM, and other digital logic circuits. CMOS technology is also used for several analog circuits such as image sensors (CMOS sensor), data converters, and highly integrated transceivers for many types of communication. Frank Wanlass patented CMOS in 1963 (US patent 3,356,858).