# **RTL** Timing

Young Won Lim 10/20/15 Copyright (c) 2011 – 2015 Young W. Lim.

Permission is granted to copy, distribute and/or modify this document under the terms of the GNU Free Documentation License, Version 1.2 or any later version published by the Free Software Foundation; with no Invariant Sections, no Front-Cover Texts, and no Back-Cover Texts. A copy of the license is included in the section entitled "GNU Free Documentation License".

Please send corrections (or suggestions) to youngwlim@hotmail.com.

This document was produced by using OpenOffice and Octave.

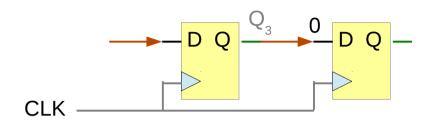

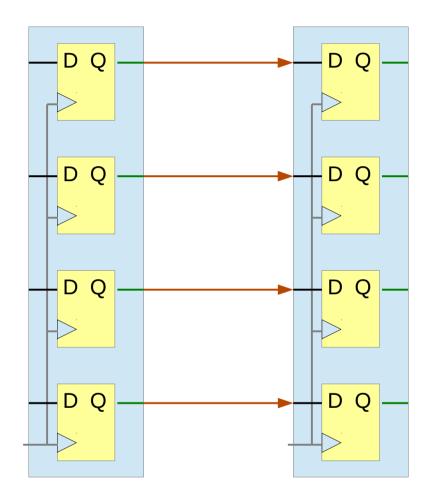

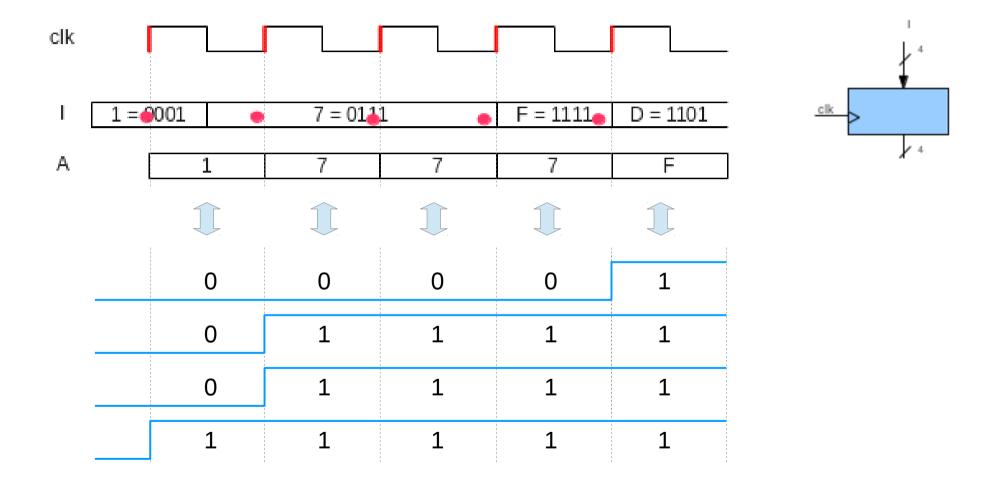

### Shift Register v.s. Pipeline Stage Register

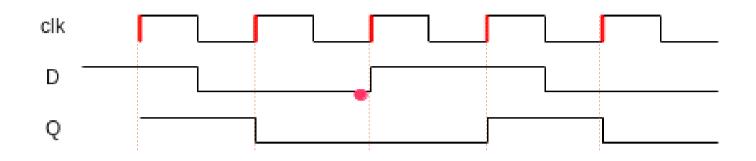

### FF and Register Timing

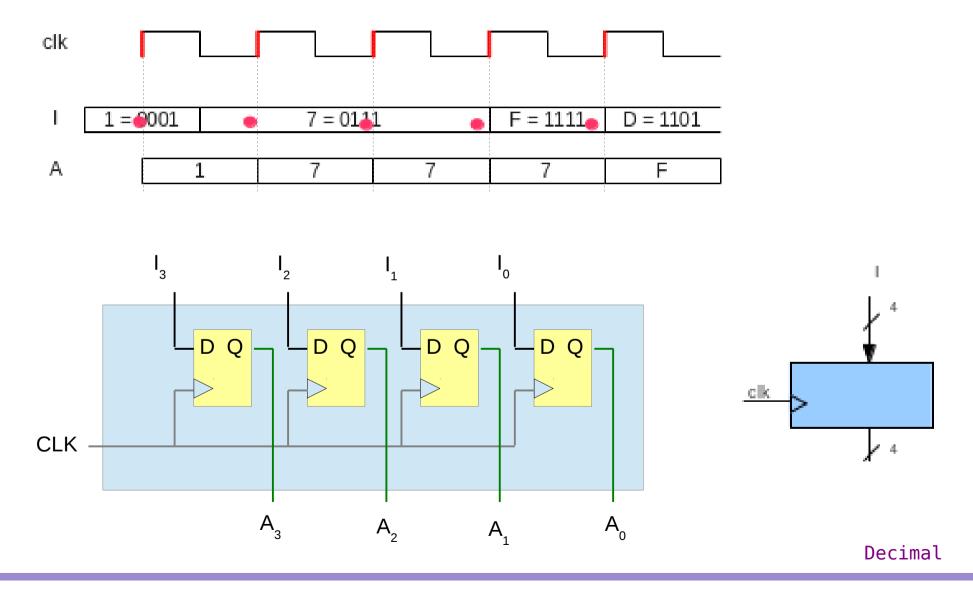

Decimal

Young Won Lim

10/20/15

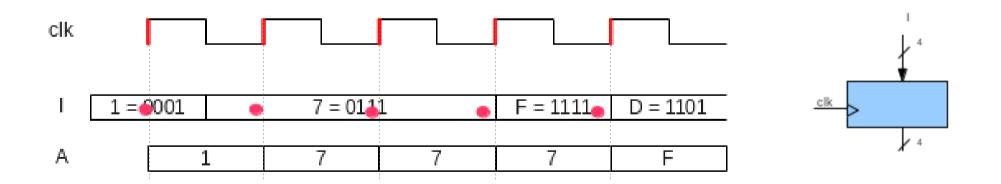

### **Bus Notation**

Decimal

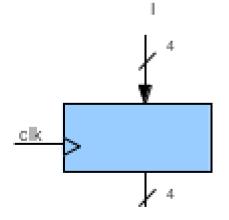

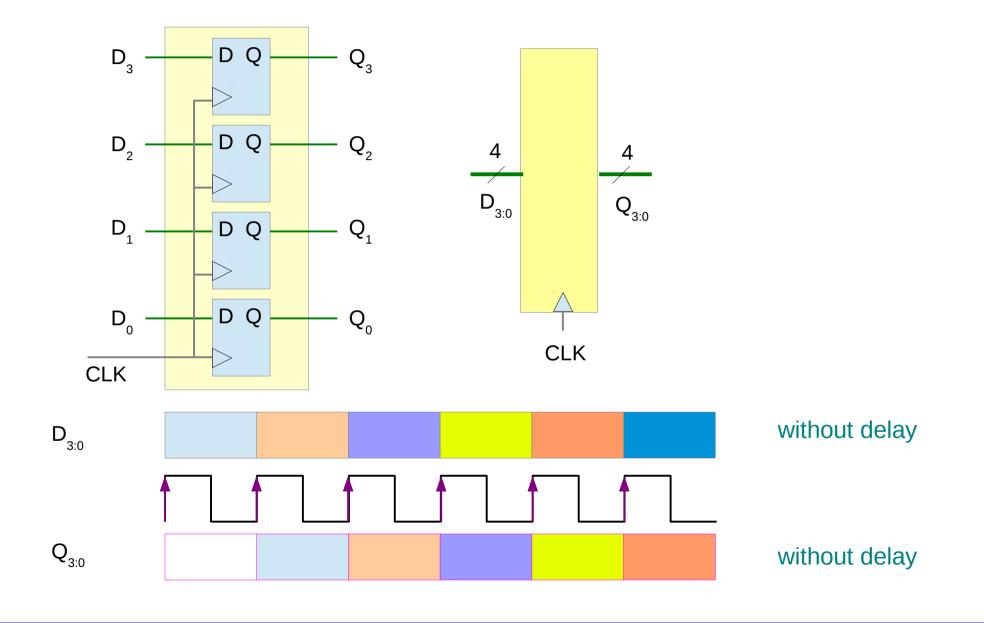

### Register

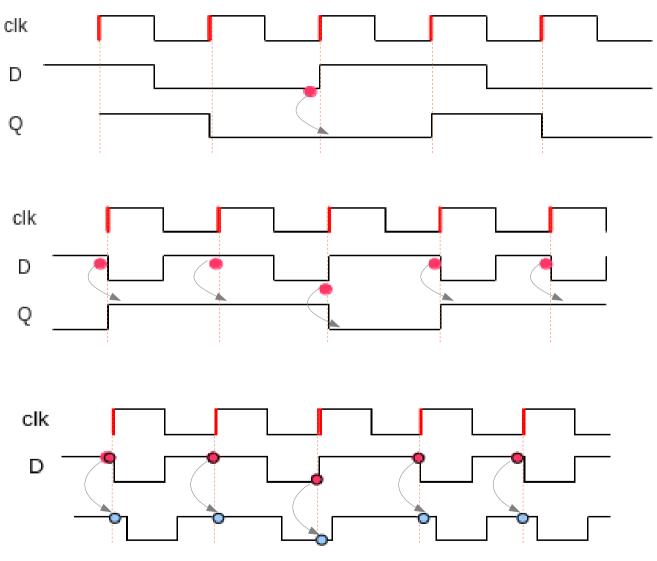

# FF Timing

input signal with a delay ignored (ideal case)

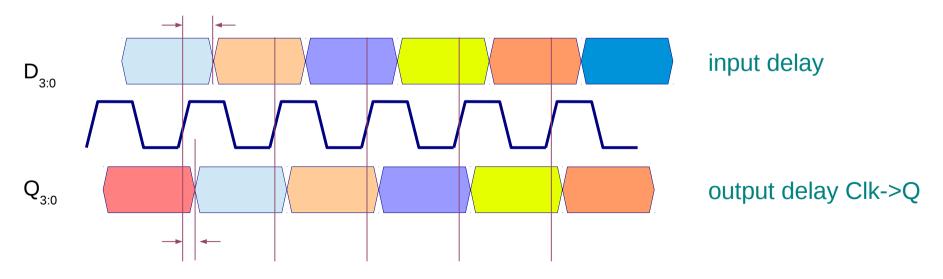

input signal with a delay explicitly shown

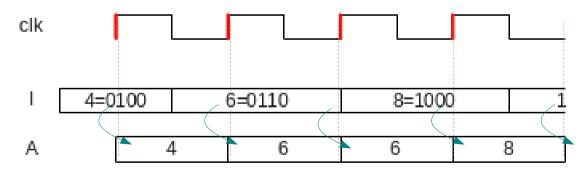

# **Register Timing**

input signal with a delay explicitly shown

input signal with a delay explicitly shown

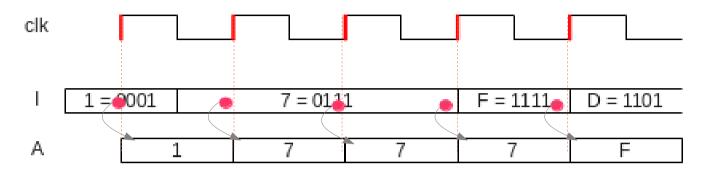

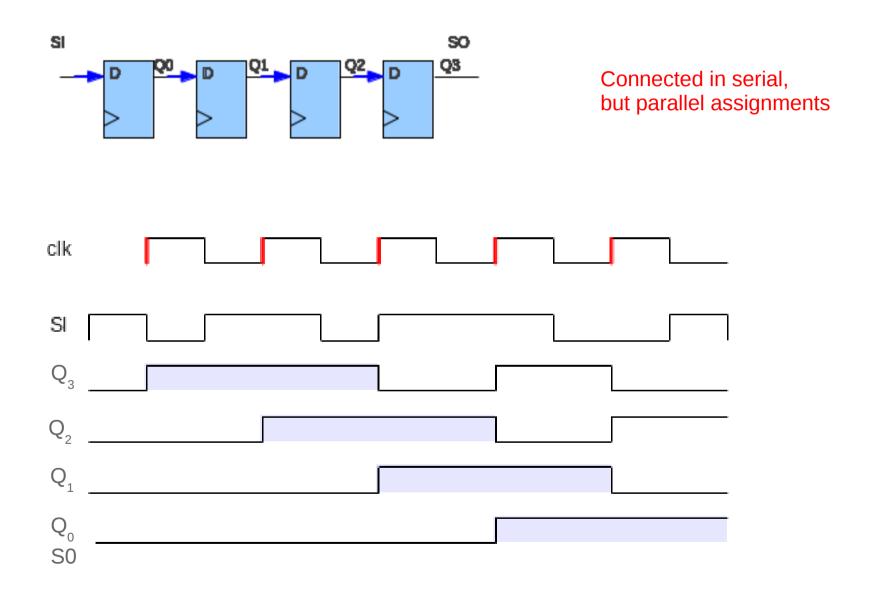

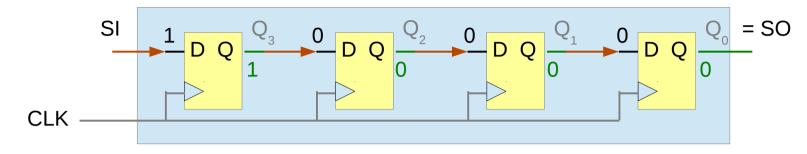

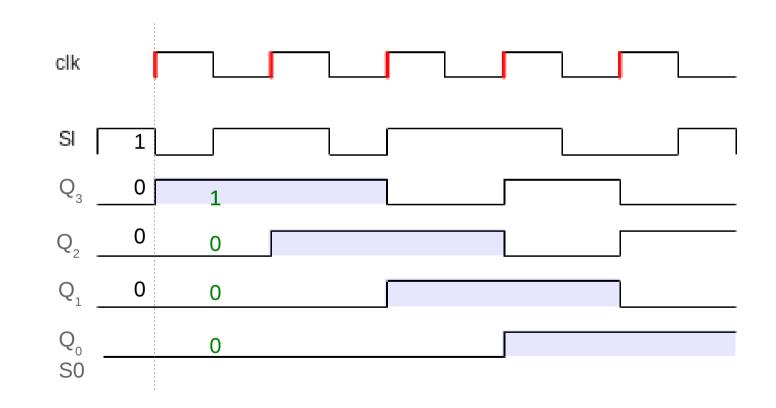

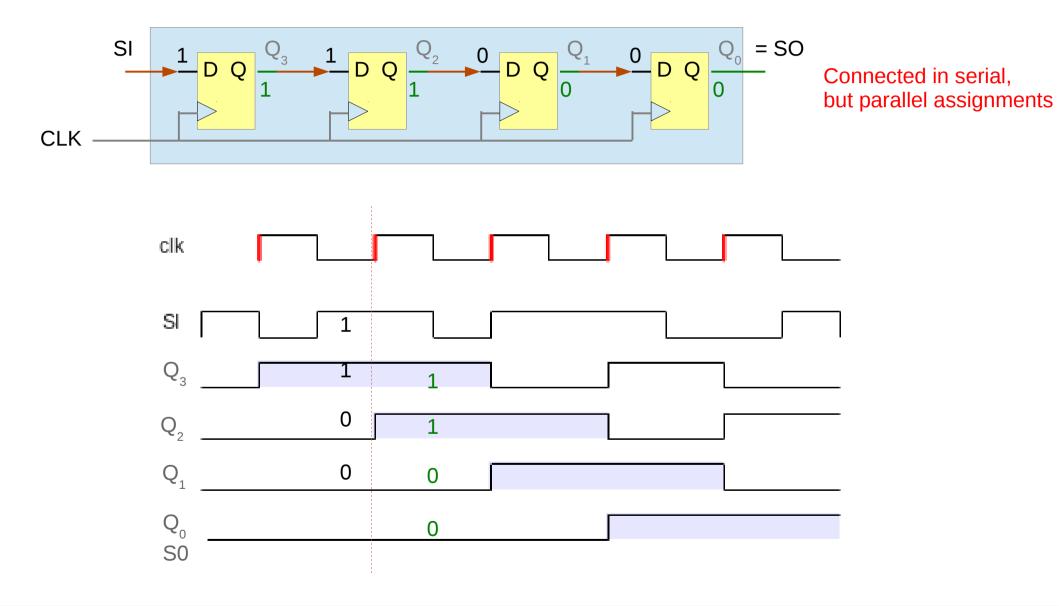

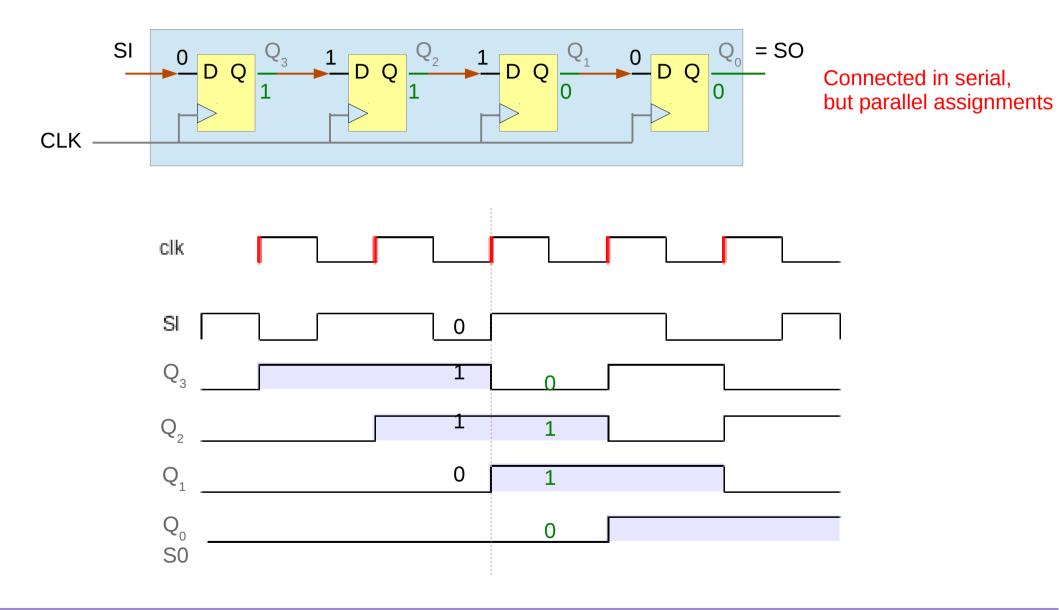

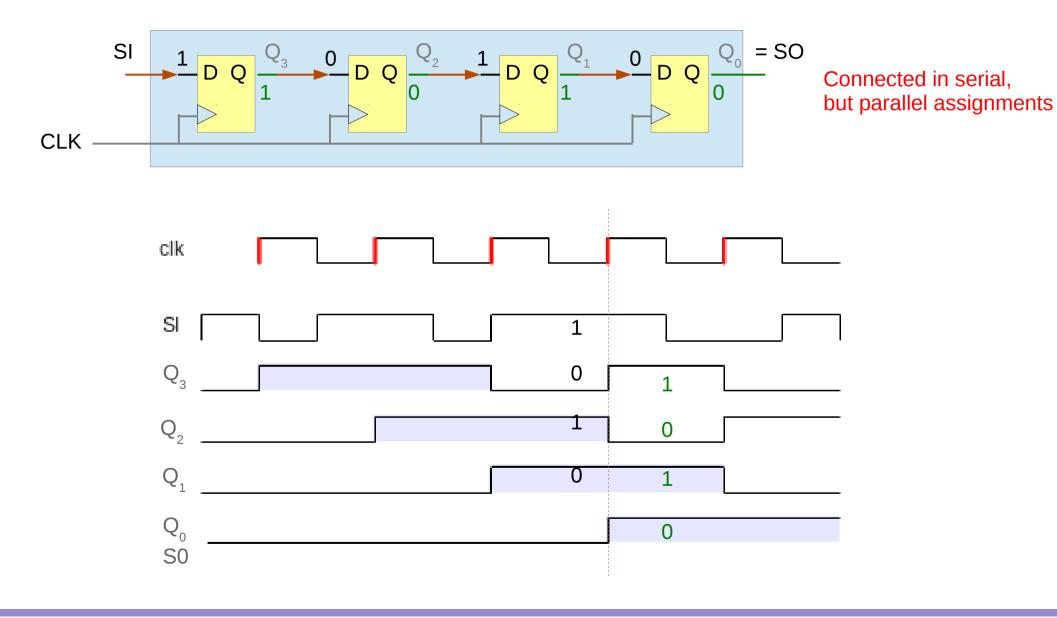

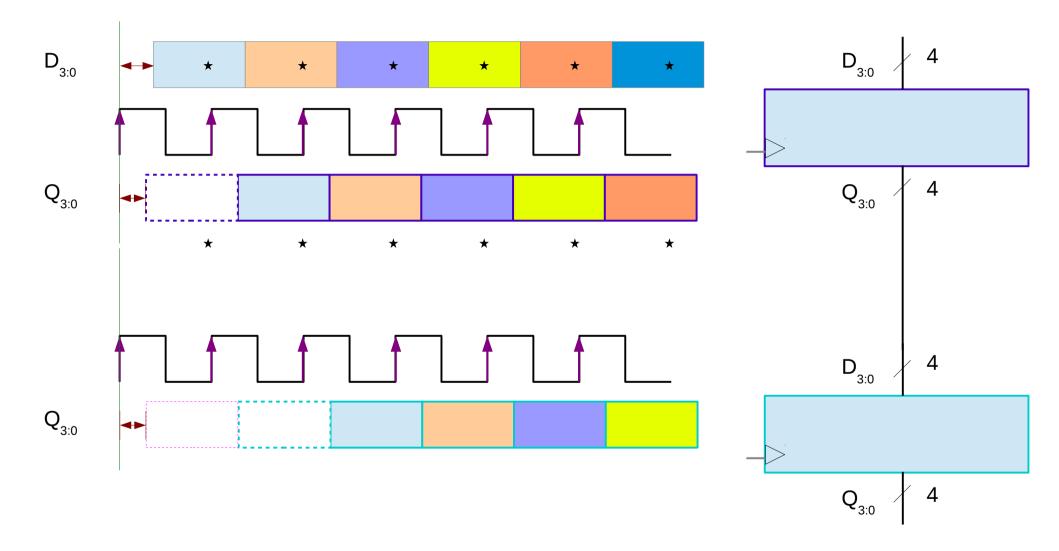

### Shift Register Timing

Connected in serial, but parallel assignments

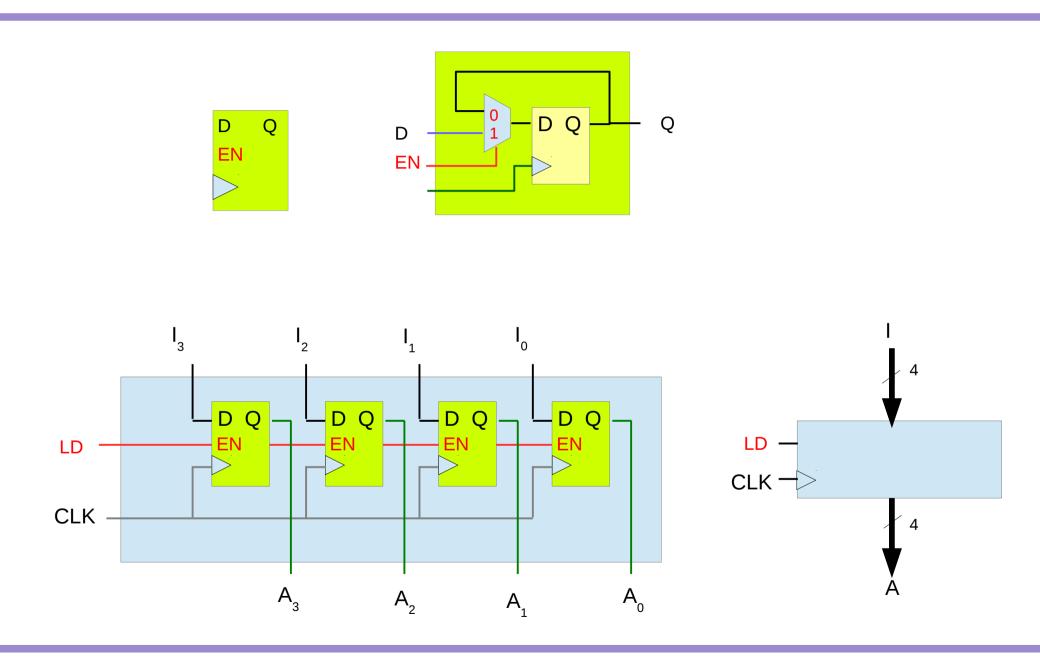

### **Register with Parallel Load**

### Register

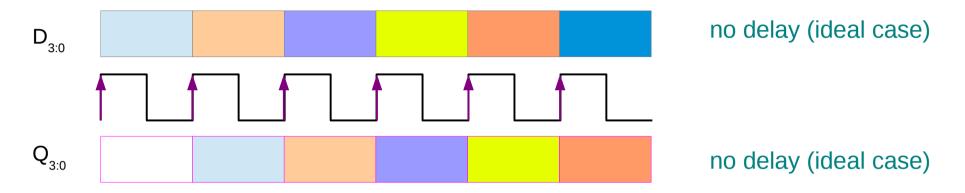

# Types of Timing Diagrams

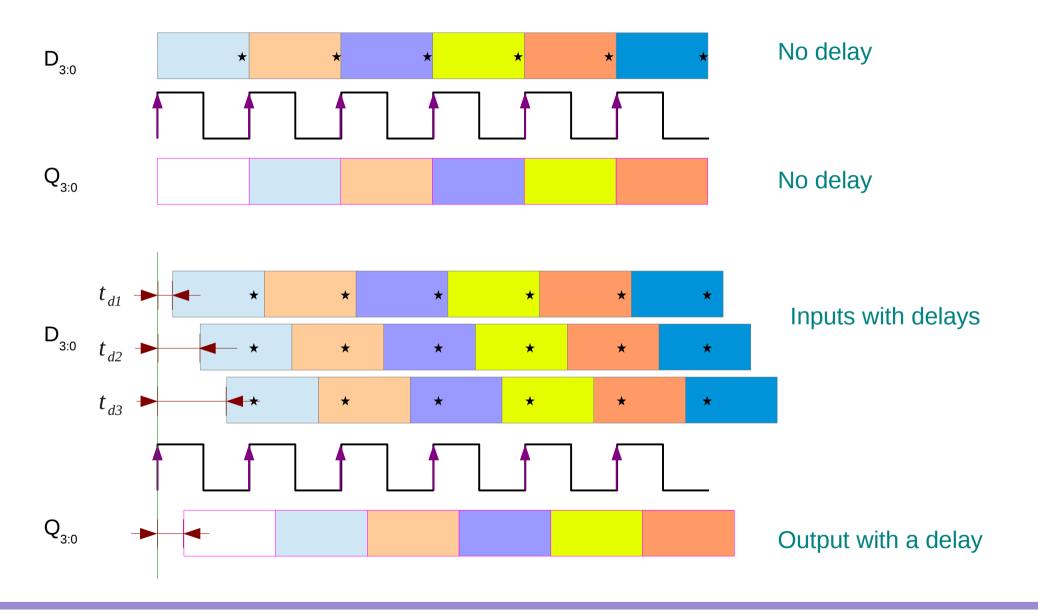

#### a timing diagram without delays

#### a timing diagram with delays

### **DFF** Testbench

module dff(d, clk, rst, q, qb); input d, clk, rst; output q, qb; reg q;

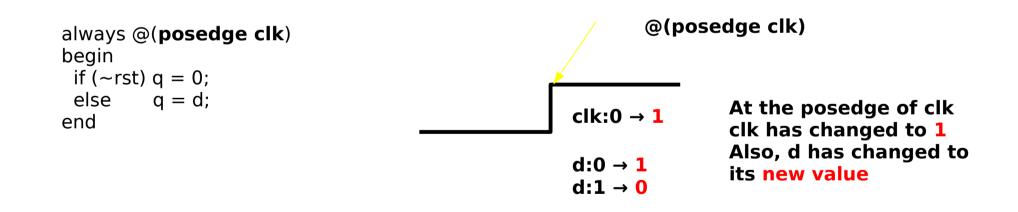

always @(posedge clk) begin if (~rst) q = 0; else q = d; end

assign qb =  $\sim$ q; endmodule

| Nonblocking<br>Assignments | <= |

|----------------------------|----|

| Blocking<br>Assignments    | =  |

| - | nitial<br>egin<br>#20 | clk =0;<br>d =0;<br>rst =1;<br>rst =0;<br>rst = 1;  |

|---|-----------------------|-----------------------------------------------------|

|   | #10<br>#10<br>#10     | d <= 0;<br>d <= 1;<br>d <= 0;<br>d <= 1;<br>d <= 1; |

|   | nd                    | ,                                                   |

|   |                       | d = 0;<br>d = 1;<br>d = 0;<br>d = 1;                |

`timescale 1ns/100ps module dff\_tb; reg d, clk, rst; dff U1 (d, clk, rst, q, qb); always #10 clk = ~clk; initial begin

\$dumpfile("test.vcd");

\$dumpvars(0, dff\_tb);

end

endmodule

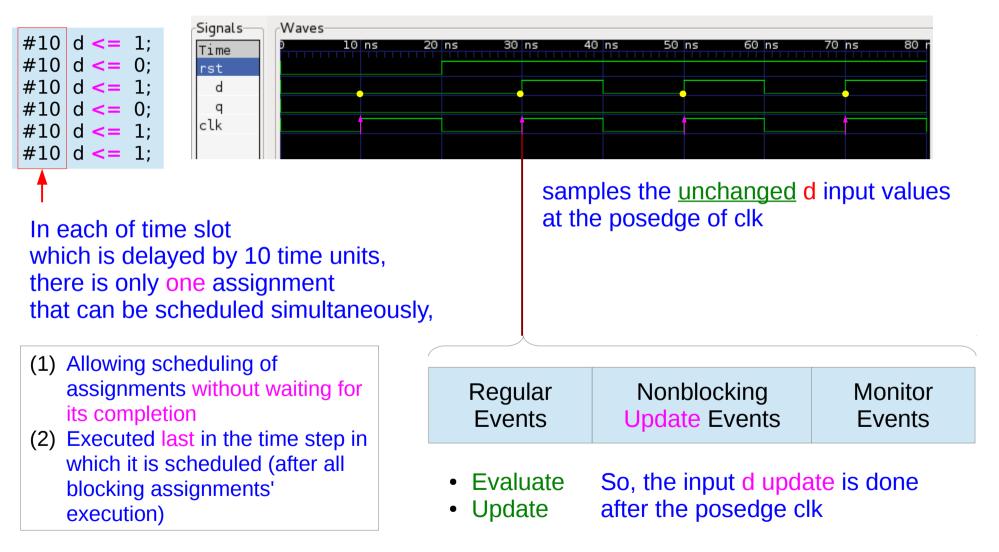

## **Testbench with Nonblocking Assignments**

```

module dff(d, clk, rst, q, qb);

input d, clk, rst;

output q, qb;

reg q;

```

```

always @(posedge clk)

begin

if (\simrst) q = 0;

else

q = d;

end

```

assign  $qb = \sim q$ ; endmodule

initial begin clk = 0: d =0: rst = 1: rst = 0: #20 rst = 1: #10 d <= 1; #10 d <= 0: #10 d <= 1: #10 d <= 0: #10 d <= 1: #10 d <= 1: \$finish; end

`timescale 1ns/100ps module dff tb; reg d, clk, rst; dff U1 (d, clk, rst, q, qb); always #10 clk =  $\sim$  clk; initial begin

\$dumpfile("test.vcd"); \$dumpvars(0, dff tb); end

endmodule

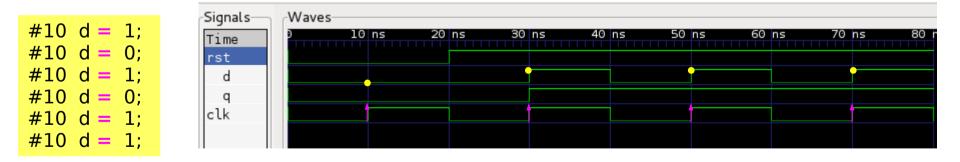

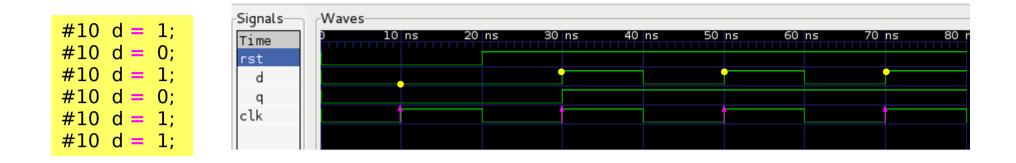

## **DFF Testbench Waveforms**

#### **Nonblocking Assignments**

samples the <u>unchanged</u> d input values at the posedge of clk

#### **Blocking Assignments**

samples the <u>changed</u> d input values at the posedge of clk

### **Blocking Assignments**

# Nonblocking Assignments

#### **Nonblocking Assignments**

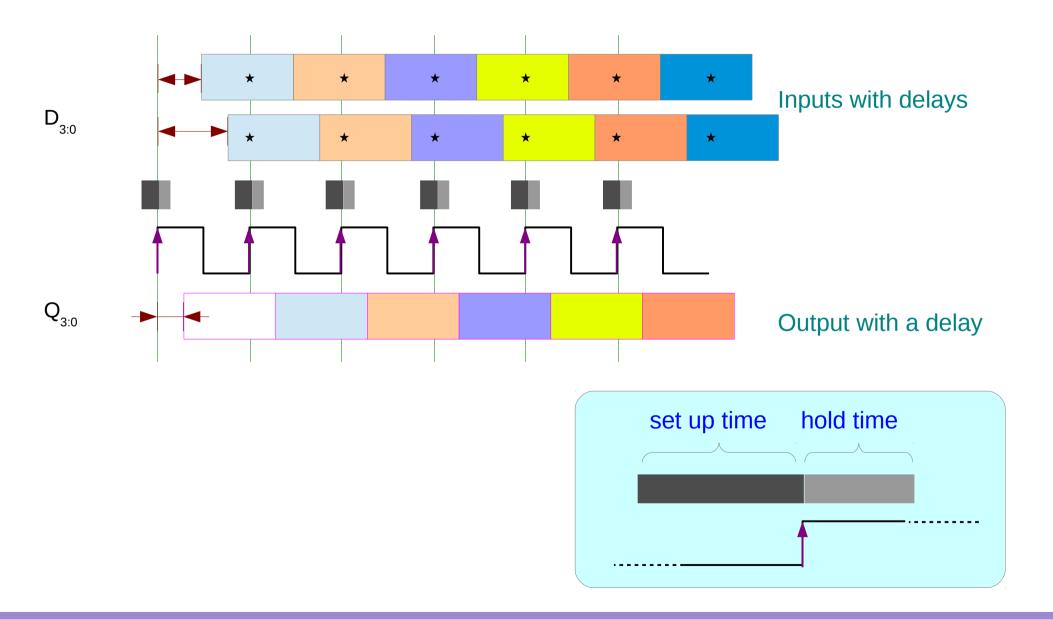

### FF Timing – Input and Output Delays

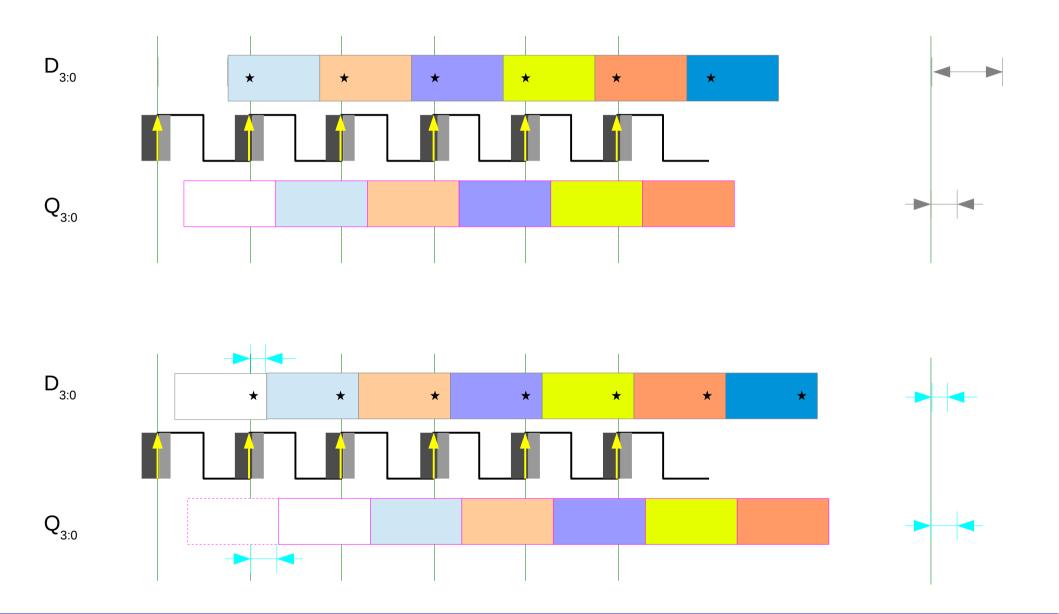

### Reg to Reg Timing

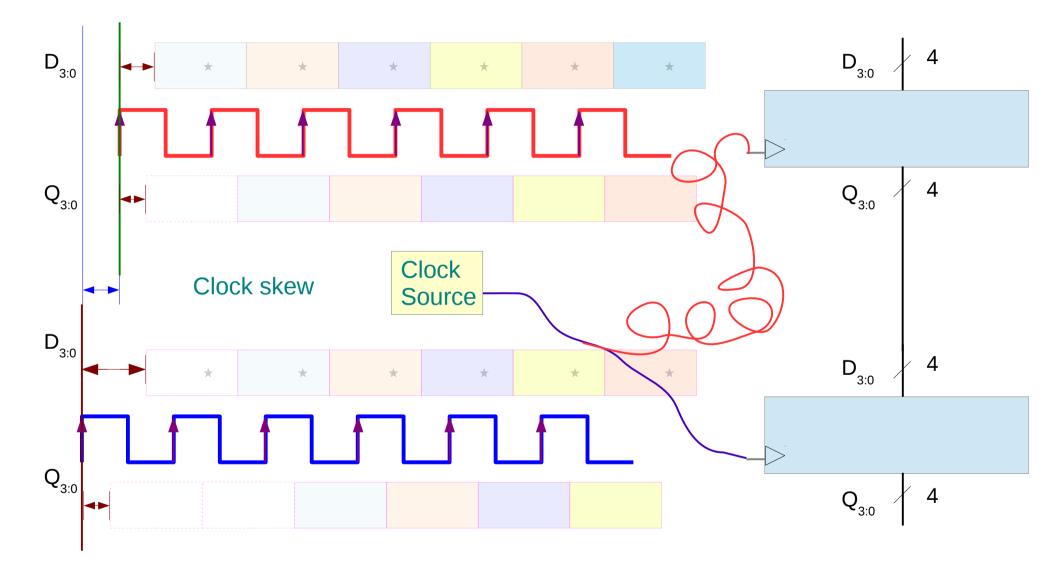

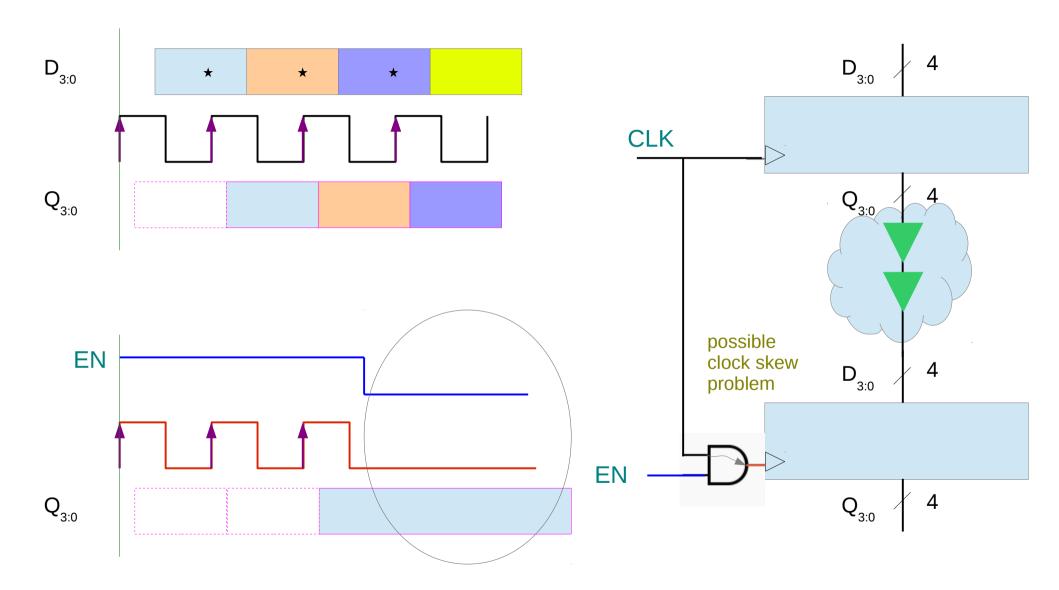

### **Clock Skew**

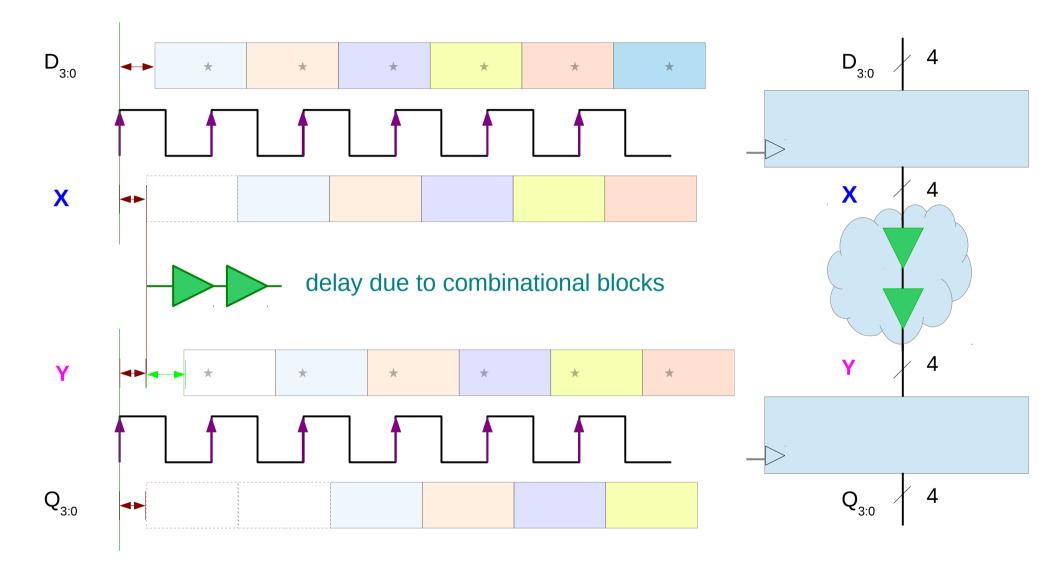

### Path Delay

## Setup & Hold Time (1)

### Setup & Hold Time (2)

**RTL** Timing

27

Young Won Lim 10/20/15

## **Clock Gating**

**RTL** Timing

28

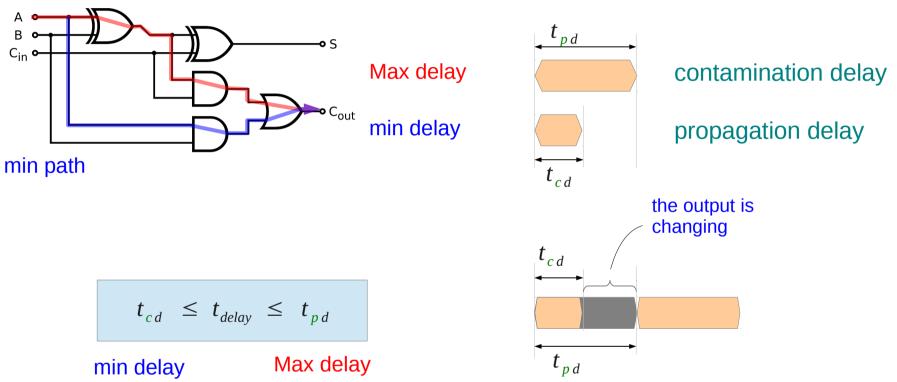

## Min Max Delay

### Max Path / Min Path

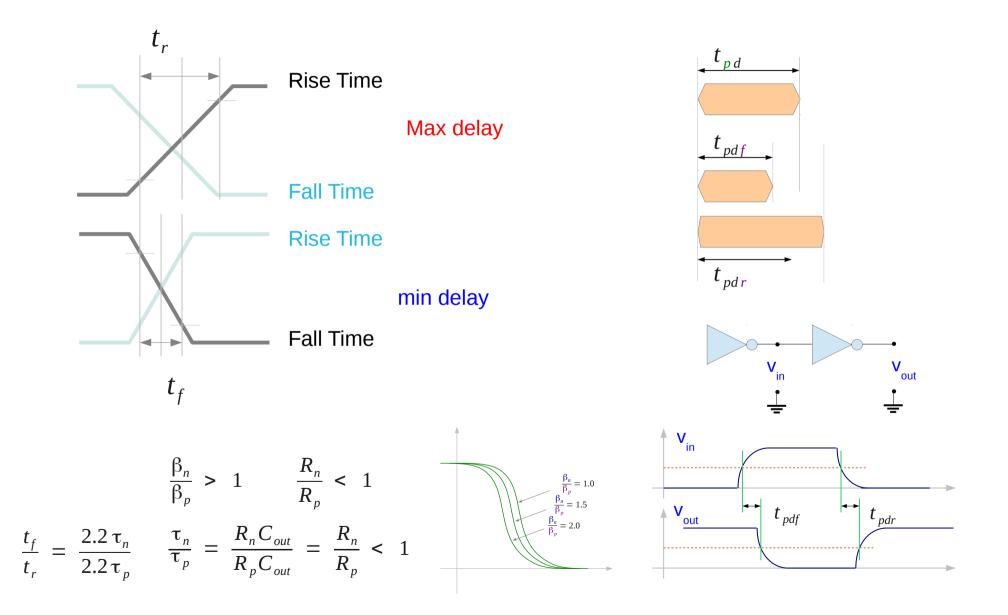

### Rise / Fall Times

### **PVT Variation**

Process Voltage

Temperature

High temperatureMax delayLow temperaturemin delay

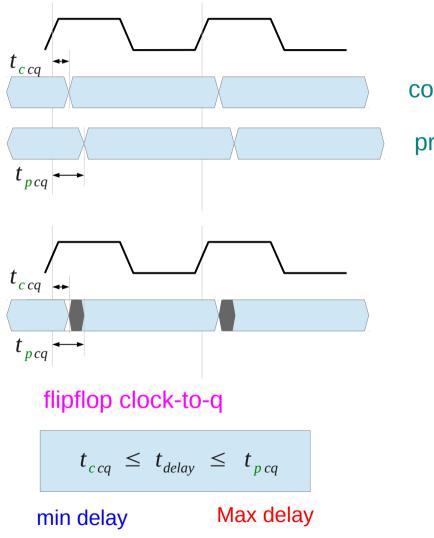

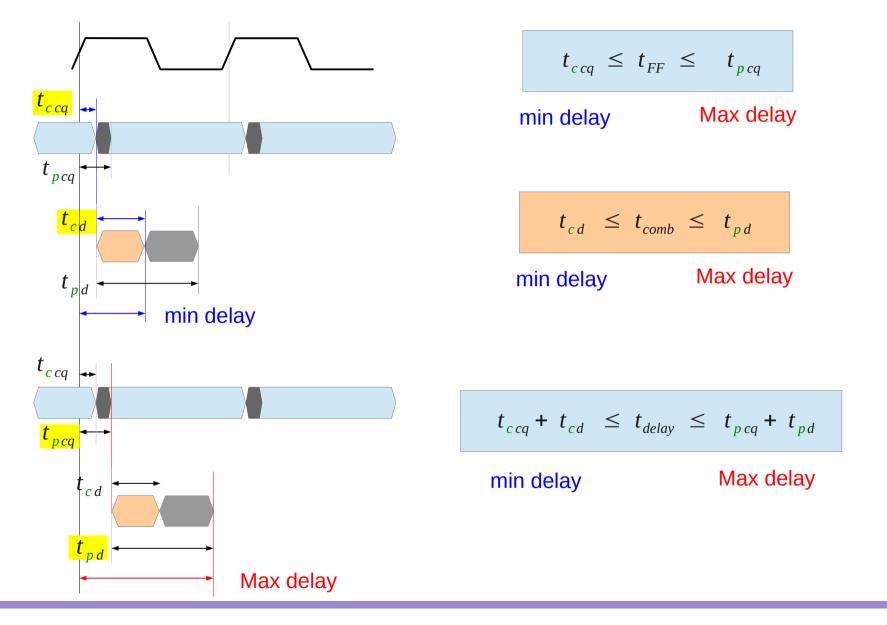

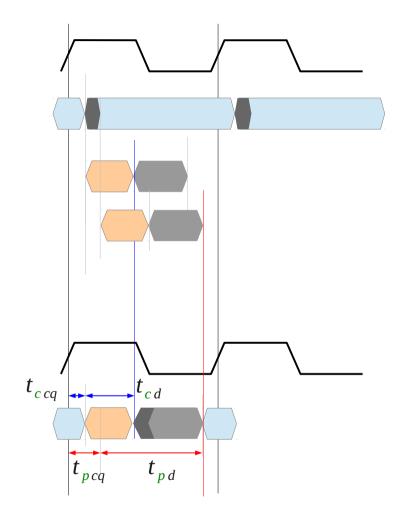

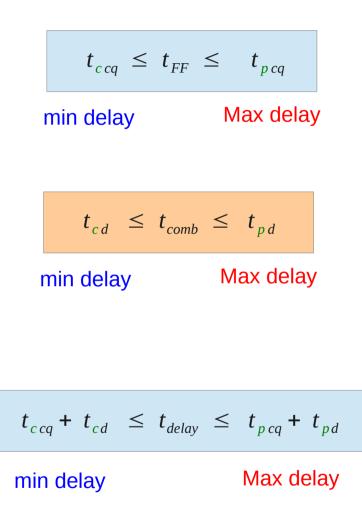

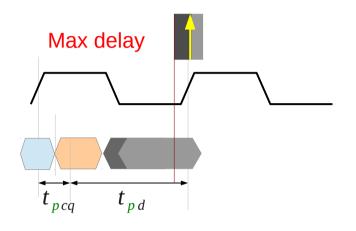

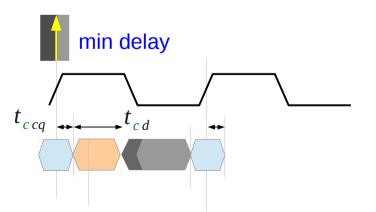

### FF Output Delay

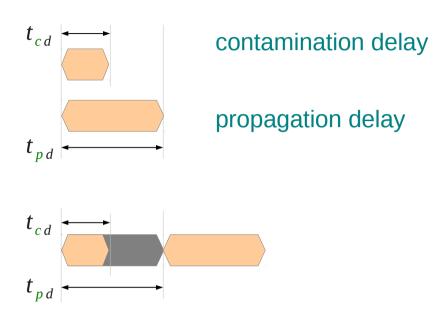

contamination delay

propagation delay

### Path Delay

combinational logic delay

$$t_{cd} \leq t_{delay} \leq t_{pd}$$

min delay Max delay

### Reg-to-Reg Delay (1)

### Reg-to-Reg Delay (2)

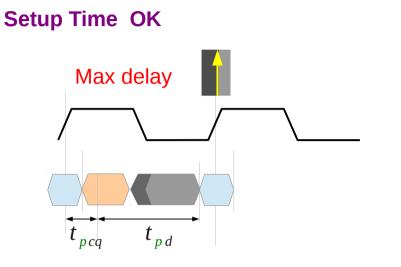

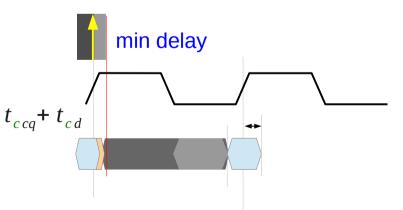

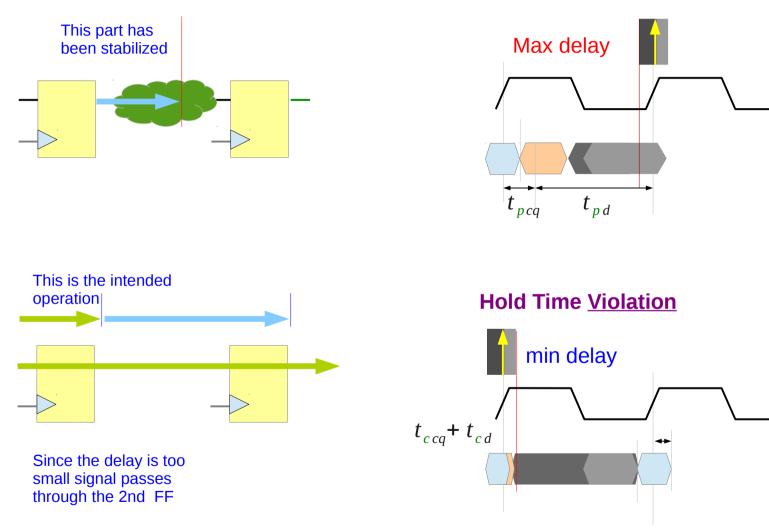

## Setup Time / Hold Time

#### Setup Time Violation

**Hold Time OK**

#### Hold Time Violation

### Setup Time / Hold Time

#### Setup Time Violation

#### References

- [1] http://en.wikipedia.org/

- [2] M. M. Mano, C. R. Kime, "Logic and Computer Design Fundamentals", 4<sup>th</sup> ed.

[3] J. Stephenson, Understanding Metastability in FPGAs. Altera Corporation white paper. July 2009.