## CMOS Delay-5 (H.5) Inverter Chain

20161202

Copyright (c) 2015 - 2016 Young W. Lim.

Permission is granted to copy, distribute and/or modify this document under the terms of the GNU Free Documentation License, Version 1.2 or any later version published by the Free Software Foundation; with no Invariant Sections, no Front-Cover Texts, and no Back-Cover Texts. A copy of the license is included in the section entitled "GNU Free Documentation License".

## References

| Sc | me Figures from the following sites                               |

|----|-------------------------------------------------------------------|

|    |                                                                   |

| [1 | ] http://pages.hmc.edu/harris/cmosvlsi/4e/index.html              |

| -  | Weste & Harris Book Site                                          |

| [2 | ] en.wikipedia.org                                                |

| [2 | Jen.wikipedia.org                                                 |

| [3 | ] http://www.ee.ic.ac.uk/pcheung/teaching/ee4_asic/notes/Topic%20 |

|    |                                                                   |

|    |                                                                   |

|    |                                                                   |

|    |                                                                   |

|    |                                                                   |

|    |                                                                   |

|    |                                                                   |

|    |                                                                   |

|    |                                                                   |

|    |                                                                   |

|    |                                                                   |

|    |                                                                   |

|    |                                                                   |

|    |                                                                   |

|    |                                                                   |

|    |                                                                   |

|    |                                                                   |

|    |                                                                   |

|    |                                                                   |

|    |                                                                   |

Driving Large Capacitive Loads R O <u>⊥</u> Cg R tapa CL how to minimize t ~ RCL

Transconductance B -> R β: Device Transconductance Parameter k: Process Transconductance Parame ter M: Electron/Hole Mobility  $\rho MOS \quad \beta p = k_p \left(\frac{W}{L}\right)_p \qquad k_p = \mu_p C_{ox} \quad Cox = \frac{E \cdot x}{t_{ox}}$ n MOS  $\beta_n = k_n \left(\frac{W}{L}\right)_n$   $k_n = \mu_n C_{ox}$   $C_{ox} = \frac{\varepsilon_{ox}}{t_{ox}}$  $\rho MOS \qquad \beta_{P} = \mu_{P} C_{ox} \left(\frac{\omega}{L}\right)_{\rho} = k_{P} \left(\frac{\omega}{L}\right)_{\rho}$ n MOS  $\beta_n = \mu_n C_{ox} \left(\frac{\omega}{L}\right)_n = k_n \left(\frac{\omega}{L}\right)_n$ Saturation Current  $I_{d_p} = \frac{\rho_p}{2} \left( V_{GSN} - |V_{Tp}| \right)^2 \qquad V_{Tp} < D$  $I_{dn} = \frac{\rho_n}{2} \left( V_{Gsn} - V_{Tn} \right)^3 \qquad V_{Tn} > D$

Transconductance Ratio  $\frac{\partial_{\eta}}{\partial p} = \frac{k_n \left(\frac{W}{L}\right)_m}{k_p \left(\frac{W}{L}\right)_p}$  $\beta \propto \frac{1}{k} \quad \beta \propto \left(\frac{w}{L}\right) \quad \beta \propto k.$  $\begin{array}{c|c} a & \text{unit nMOS} \\ \hline a & \text{unit pMOS} \end{array} \end{array} \qquad \begin{array}{c} \left(\frac{W}{L}\right)_{m} \\ \hline \left(\frac{W}{L}\right)_{P} \end{array} = 1 \end{array}$  $\frac{\Im_n}{\Im_p} = \frac{k_n \left(\frac{W}{L}\right)_m}{k_o \left(\frac{W}{L}\right)_p} = \frac{k_n}{k_p} = \gamma = 2 \sim 3$  $\frac{kn}{kp} = 2n3$  different mobility physical property

R during transient switching  $\frac{\beta_{n}}{\beta_{p}} = \frac{k_{n} \left(\frac{\omega}{\omega}\right)_{n}}{k_{p} \left(\frac{\omega}{\omega}\right)_{p}} \qquad \frac{k'_{n}}{k'_{p}} = \frac{\mu_{n}}{\mu_{p}} = \gamma = 2 \sim 3$ Rn fall time tf  $R_{n} = \frac{|}{\beta_{n} (V_{pp} - V_{T_{n}})}$ l Rp rise time tr  $R_{p} = \frac{1}{\beta_{p} (V_{pp} - V_{T_{p}})}$

Input Capacitance a unit pMos with minimum size min w & min L CGN a unit nMOS with minimum size min w & min L  $\frac{C_{in} = C_{qn} + C_{qp}}{= C_{ox} (A_{qn} + A_{qp})}$ Ag: gate area = Cox (LWn + LWp) the channel length L assumed Cin = Cox L (Wn + Wp)  $= C_{0x} L (W_n + Y W_n)$ =  $C_{0x} L W_n (1 + Y)$ = CGn (1+r)

Owtput Capacitance Cout = Cpan + Ch C drain parasitic cap. Cpan f Cr Cpan + --С<sub>Қ</sub> Coute. Cpan + CL Panasitic Capacitance

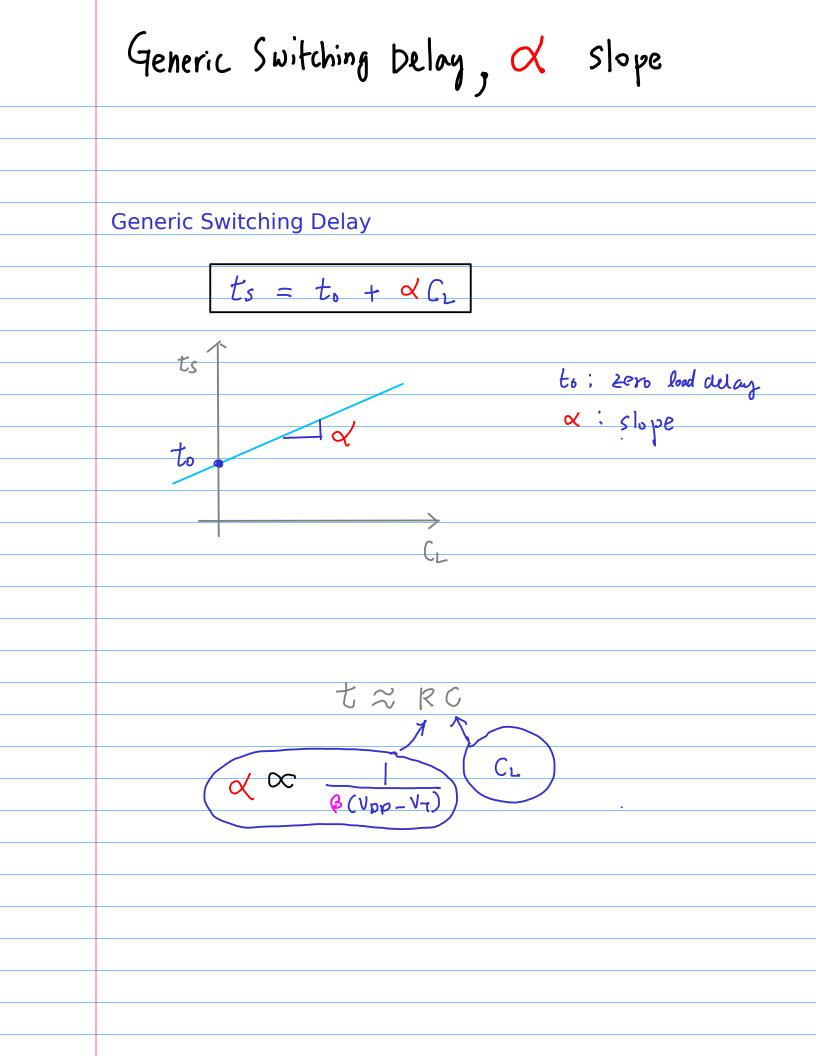

Time Constants  $\begin{cases} V_{out}(t) = V_{pp} \left( 1 - e^{-t/z} \right) & t_{f} \\ V_{out}(t) = V_{pp} e^{-t/z} & t_{r} \end{cases}$ 7= RCout = R(Cpan + CL) **Generic Switching Delay**  $t_s = t_0 + \alpha G_L \implies t_s = t_r = t_f$ When CL=O Zero Load non zero Cpan Panasitic Capacitance

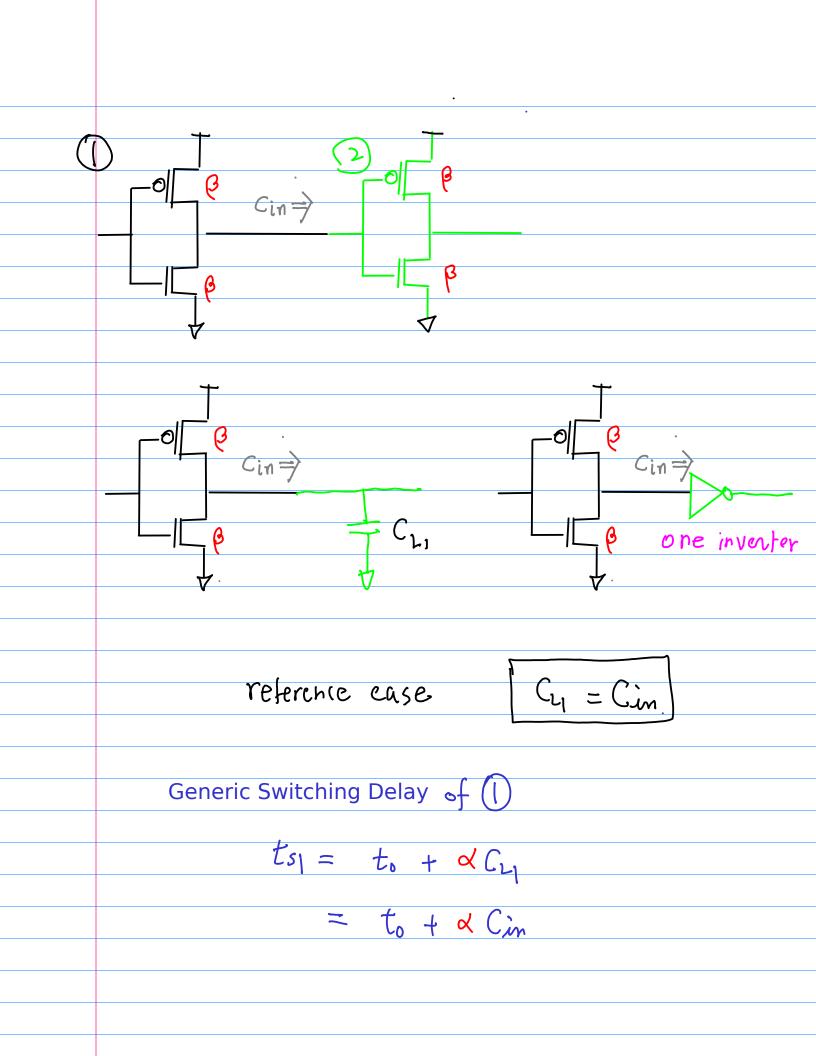

When CL >> Cin many inverters ୧ b ٠ 0 0 to minimize ts (generic switching Delay)  $\forall \downarrow \Rightarrow R \downarrow \Rightarrow \beta \uparrow \Rightarrow bigger size$ speed V.S. area tradeoff  $t_s = t_0 + \alpha C_L$   $t \approx RC$  $(\chi \propto \frac{1}{\beta(V_{pp}-V_{T})})$ CL

to minimize ts  $\mathbb{A} \downarrow \Rightarrow \mathbb{R} \downarrow \Rightarrow \mathbb{B} \uparrow \Rightarrow \text{bigger s:2c}$ speed V.S. area tradeoff Scaling Factor S. B' = SB  $\frac{R_{c}}{t_{s}} = \frac{R'}{s}$   $\frac{R'_{c}}{s}$   $\frac{R'_{c}}{s}$   $\frac{R'_{c}}{s}$   $\frac{R'_{c}}{s}$ Compensation Factor (1) Chables an investor to drive larger values of (CL) If  $C_{L} = 5 C_{in}$  (increased by the scaling factor \$) then the switching time is the same

jh creased bigger inventer Cin should drive 0 β 61  $C_{L}$ it is natural to assume the first driving gate must be comparable to the reference gate input ref inn

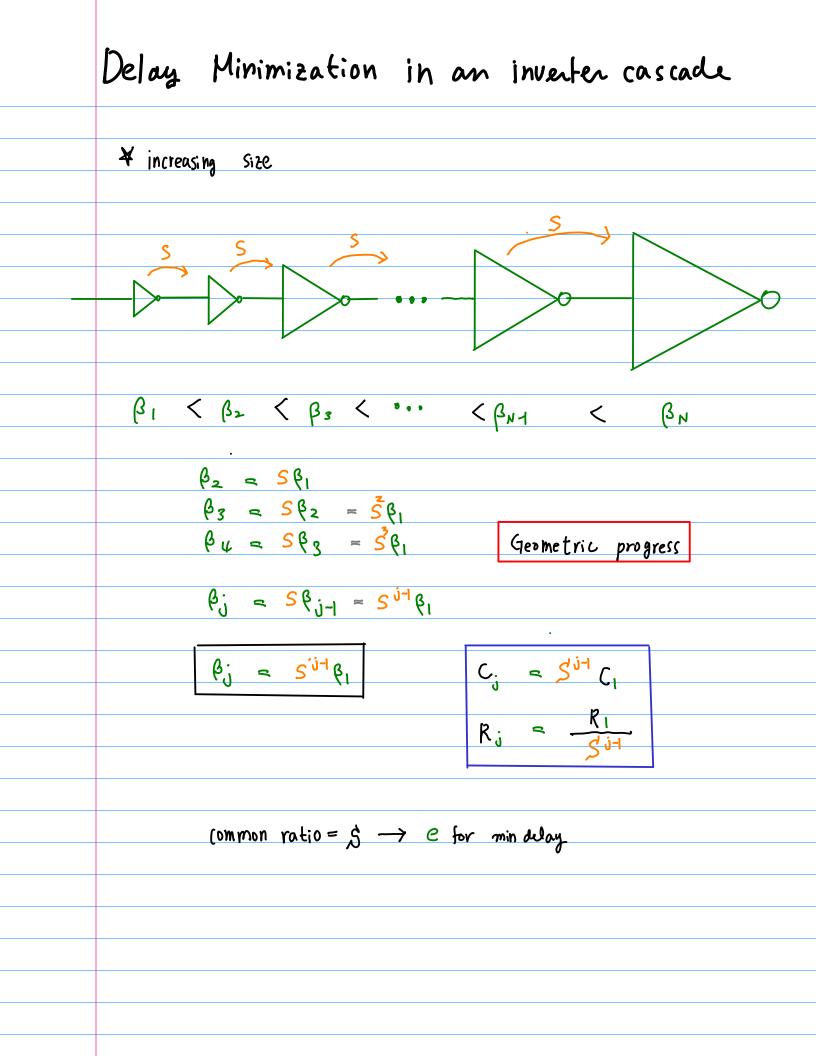

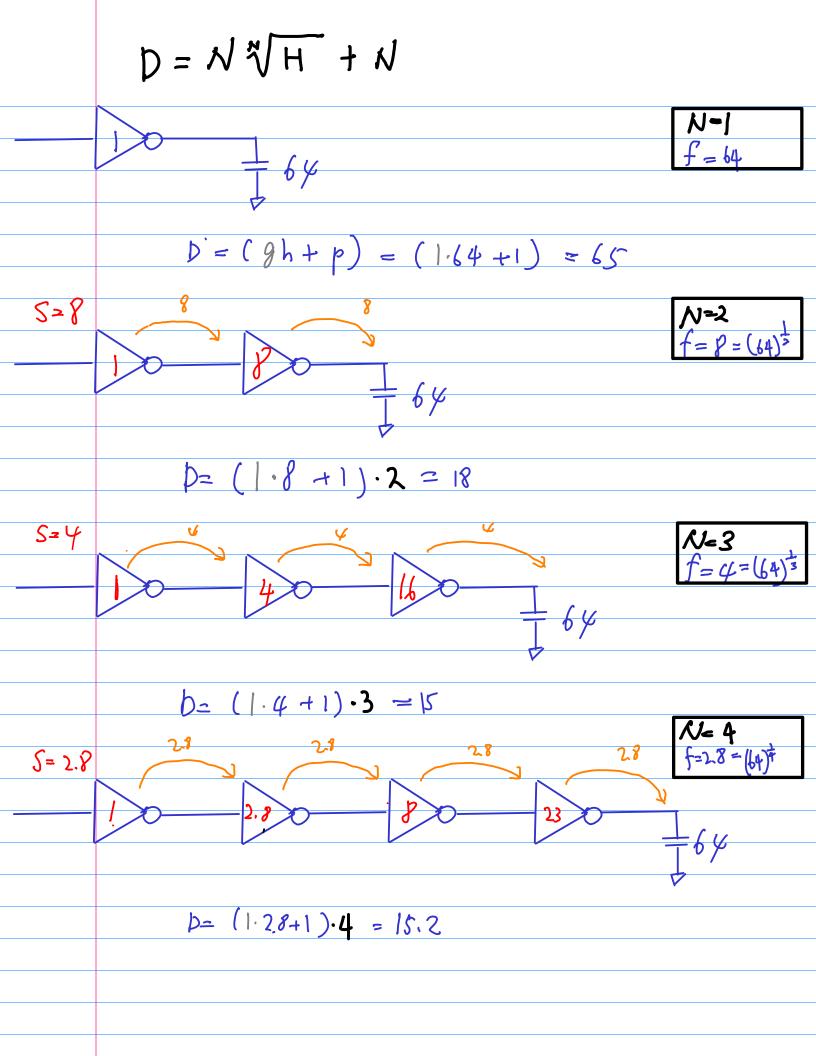

think G.P. (Geometric Progression) in size factors 5 \_\_\_\_S +Arithmetic Progression >/ Geometric Progression V Z path delay min delay. When all equal path delay

Case I: Ignove Parasitic Capacitance Rj R<sub>j+1</sub> change Rj Cpan, j Cjrl ≠ Rj+I Cpan, j << Cj+1 ζj = Rj ζ<sub>j\*1</sub> ← Using di=gihi  $(p_i = 0)$

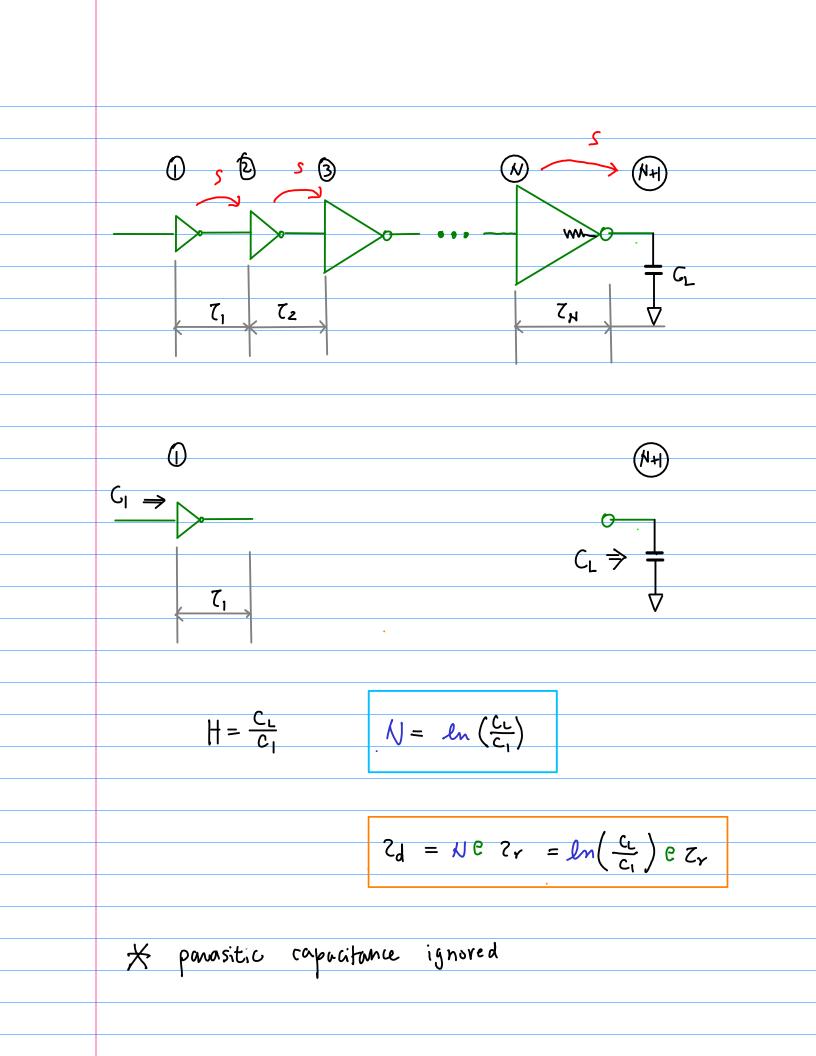

S : size factor 2 0 <u>5</u> 2 <u>5</u> 3 N (ヤ+ๅ) w <del>Т</del> С. ζ1 T2 7<sub>N</sub> N-stage inverter Chain  $\zeta_j = R_j C_{j+1}$  $Z_{d} = Z_{1} + Z_{2} + \cdots + Z_{N}$  $= R_{1}C_{2} + R_{3}C_{3} + \dots + R_{N}C_{L} \qquad (C_{NH} = C_{L})$  $= \left( R_{I} \right) \left( S C_{I} \right) + \left( \frac{R_{I}}{S} \right) \left( S^{2} C_{I} \right) + \left( \frac{R_{I}}{S^{2}} \right) \left( S^{3} C_{I} \right) + \cdots + \left( \frac{R_{I}}{S^{N-1}} \right) \left( S^{N} C_{I} \right)$  $= SR_1C_1 + SR_1C_1 + SR_2C_1 + \cdots + SR_3C_1$  $T_r = R_1 C_1$   $S_T = S_R_1 C_1$  $= N S R_1 C_1$ = N\$ ?r equalize the signal delay through each stage

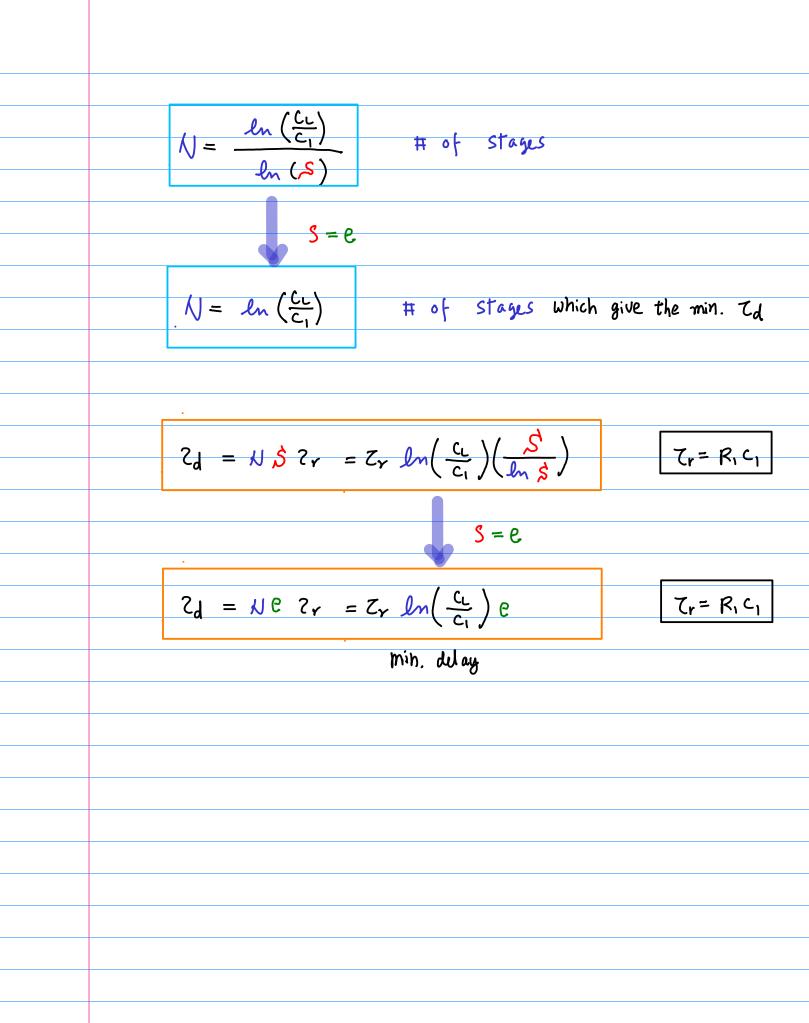

$$C_{L} = S^{H} C_{1} \qquad S^{H} = \frac{C_{L}}{c_{1}}$$

$$D_{N} (S^{H}) = N D_{N} (S) = d_{N} \left(\frac{C_{L}}{c_{1}}\right)$$

$$K_{1} = \frac{d_{N} \left(\frac{C_{L}}{c_{1}}\right)}{d_{N} (S)} \qquad \text{ for stages}$$

$$C_{d} = N S ?_{r} = C_{r} D_{N} \left(\frac{C_{L}}{c_{1}}\right) \left(\frac{S}{d_{N}}S\right) \qquad T_{r} = R_{r} C_{1}$$

$$for bremin dedag$$

$$\frac{ST_{q}}{2S} = 0 \implies \frac{S}{2S} \left[\frac{S}{D_{N}(S)}\right] = 0$$

$$\frac{ST_{q}}{2S} = 0 \implies \frac{S}{2S} \left[\frac{L_{N}(S)}{(L_{N}(S))^{2}}\right] = 0$$

$$C_{d} minimum \ When \ Side \ freetor \ S = 0$$

\_\_\_\_\_

\_\_\_\_\_

\_\_\_\_\_

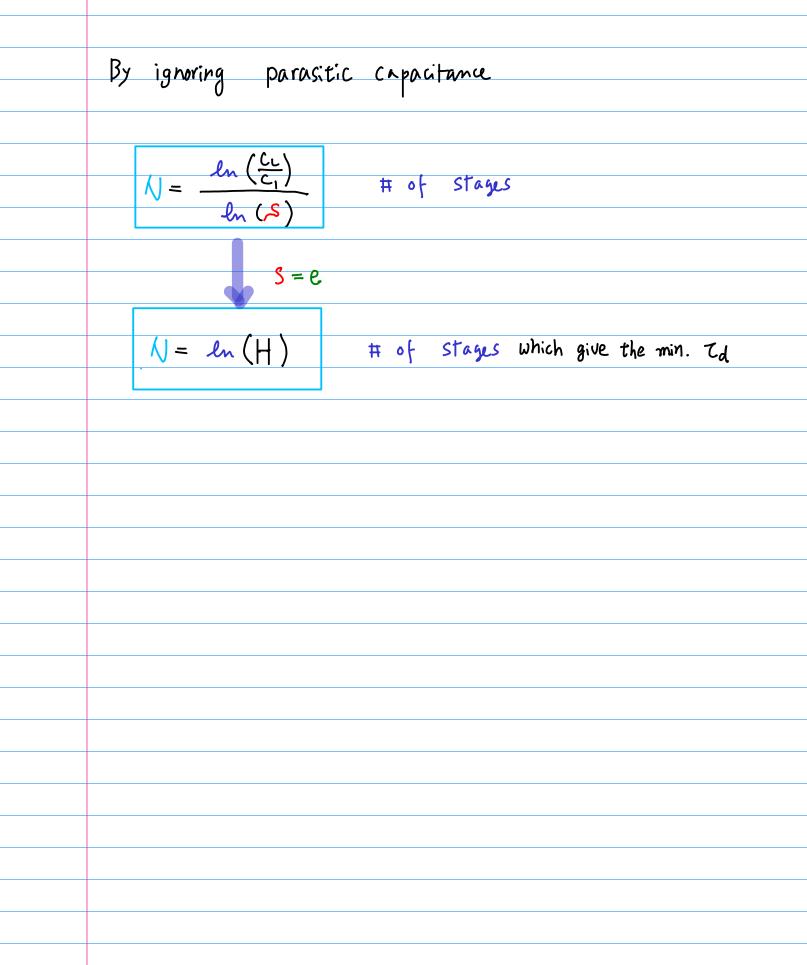

Ignoring Cpm  $C_1 \Rightarrow$  $C_2 \Rightarrow \frac{1}{6} 6 \%$  $N = ln\left(\frac{c_{\rm L}}{c_{\rm 1}}\right) = ln\left(64\right) = 4.15 \Rightarrow N=4$  $Z_d = ln\left(\frac{c_L}{c_1}\right)SZ_r = Sln(64)Z_r (Z_r)=R_1C_1$  $S = \left(\frac{CL}{C_1}\right)^{\frac{1}{N}} = 64^{\frac{1}{4}} = \frac{2.8}{2}$  $= 64^{\frac{1}{4.15}} \Rightarrow C = 2.018$ 28 رگ  $\mathcal{J}$ ンる 28=784  $2.8^3 = 21.95$ Zd= 2.8 In (64) Zr = 11.6 Zr

Case II: p ~ Parasitic Capacitance parasitic delay (P) - delay due to internal (sĊp) parasitic capacitance - excluding external load cap (L) - count only diffusion capacitance of the output - delay without output load (zero load) P = Cref Cdp+Cdn drain parasitis cap Cref Cin of the ref inventer (Symmetric Inventer)

$$P = \frac{7}{2} \frac{pax}{r_{t}} = \left(\frac{Rnf \cdot C_{p} nf}{Rnf \cdot C_{p}}\right)$$

Cin of a reference investor

(Symmetric investor)

$$P = \frac{1}{3} \left(\Sigma \text{ Output scaling factors}\right)$$

$$P = \frac{1}{3} \left(\Sigma \text{ Output scaling factors}\right)$$

$$P = \frac{1}{3} = p = \frac{1}{3} = 2$$

Using di = gihi + pi • di <u>d2</u> (z => 97 C  $\zeta_3$  $h_2 = \frac{C_3}{C_2}$ Electrical  $h_1 = \frac{c_2}{c_1}$ Effort Logical  $g_{2} = 1$  $9_{1} = 1$ Effort (inverter) (inverter) normalized D = Sindividual delays path delay  $+ d_2$ dı = =  $(g_1h_1 + p_1) + (g_2h_2 + p_3)$ =  $(h_1 + p_1) + (h_2 + p_3)$  $= \left(\frac{c_1}{c_1} + p_1\right) + \left(\frac{c_3}{c_2} + p_1\right)$

Path Electrical Effort  $H = \frac{C_{\text{Last}}}{C_{\text{first}}} = \frac{C_3}{C_1} = \begin{pmatrix} C_2 \\ C_1 \end{pmatrix} \begin{pmatrix} C_3 \\ C_1 \end{pmatrix} = h_1 h_2$  $h_{1} = \frac{H}{R}$ Path peloy () =  $(h_1 + p_1) + (\frac{l_1}{h_1} + p_2)$ Minimize path delay D(h, h)  $\frac{\partial D}{\partial h_1} = \frac{\partial}{\partial h_1} \left( \begin{pmatrix} h_1 + p_1 \end{pmatrix} + \begin{pmatrix} \frac{h}{h_1} + p_2 \end{pmatrix} \right) = 0$ =  $\left| - \frac{H}{e^2} \right| = 0$  $\frac{1}{p_{2}} \left( h_{1}^{2} - h_{2}h_{2} \right) = \frac{1}{p_{1}} \left( h_{1} - h_{2} \right) = 0$ When  $h_1 = h_2$ ,  $D(h_1, h_2)$  has a minimum. minimum delay by equalizing the delay di=di through each stage

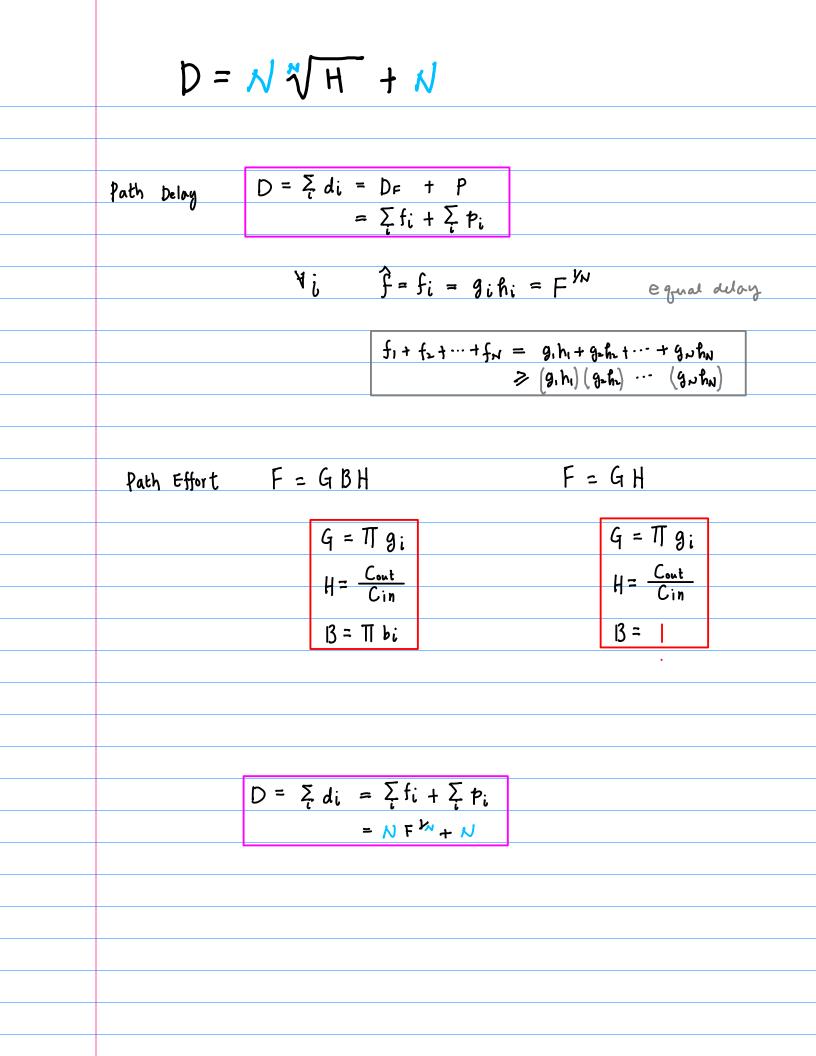

Path peloy  $D = (h_1 + p_1) + (h_2 + p_2) + (h_3 + p_3)$  $\frac{h_1 + h_2 + h_3}{3} > \sqrt[3]{h_1 h_2 h_3}$  $h_1 + h_2 + h_3 > 3\sqrt{h_1 + h_2} = 3 H^{\frac{1}{3}}$ Minimum When  $h_1 = h_2 = h_3$ arithmetic > geometric average average

## N ?

N Stages  $\leftarrow$ n₁ stages N-n₁ stages  $D = g_1h_1 + g_2h_2 + \dots + g_Nh_N \ge (g_1h_1)(g_2h_2) \dots (g_Nh_N) = GH = F$  $g_1h_1 = g_2h_2 = \cdots = g_Nh_N = F^{N_N} \rightarrow minimum$  $D = N F^{N} + \sum_{i=1}^{n_i} p_i + (N - n_i) P_{iN}$  $p_i$ : i-th stage parasitic capacitance  $(1 \le i \le n_i)$ pinvi inverter "" ( $n_i+1 \le i \le N$ )

$$D = N F^{N} + \sum_{i=1}^{n} p_i + (N - n_i) P_{iPV}$$

Find N s.t  $\frac{2D}{2N} = 0$  for  $p_i n_i mum dulay D$

$$\frac{d}{dx} (e^{ax}) = e^{ax} \ln c \cdot a, \quad c > 0$$

$$\frac{2D}{2N} = F^{N} + (N) \frac{(-1)}{N^3} [F^{N}] l_n F + p_{iPV}$$

$$= F^{N} - (\frac{1}{N} l_n F) F^{N} + p_{iPV} = 0$$

$$f_{ax} = -(l_n F^{N}) F^{N} + F^{N} + p_{iPV} = 0$$

$$f_{ax} = F^{N} - (p_{an} F) + p = [p_{iPV} + p((- p_{an} F) = 0]$$

$$F^{N} = p \quad l_n F^{N} = l_n p \quad \frac{1}{N} l_n F = l_n p$$

$$\frac{2D}{2N} = 0 \quad N = \frac{l_n F}{l_n p} = l_n F$$

$$\frac{\partial D}{\partial N} = f_{inv} - f d_{in} f_{in} + f_{inv}$$

$$= f_{inv} + f(1 - d_{in} f_{in}) = 0$$

$$assume f_{inv} = 0 \qquad f(1 - d_{in} f_{inv}) = 0$$

$$P = 0, \quad d_{in} f_{inv} = 1 \qquad f_{inv} + f(1 - d_{in} f_{inv}) = 0$$

$$mumerical \quad solution \qquad f = 3.59$$

$$D = N F^{\mu} + \sum_{i=1}^{n} p_i + (N - n_i) P_{\mu\nu}$$

$$F^{\mu} = p$$

$$\frac{2p}{2N} = p_{\mu\nu} + p(1 - 2n_i) = 0$$

$$P_{\mu\nu} = 0 \qquad p = e = 2.n_18 \qquad \text{Min } D$$

$$p_{\mu\nu} = 1 \qquad p = 3.59 \qquad \text{Min } D$$

$$F^{\mu} = p \qquad l_n F^{\mu} = l_n p \qquad \frac{1}{N} l_n F = l_n p$$

$$N = \frac{l_n F}{l_n p} = l_{op} F \qquad \text{# of stages}$$

$$N = l_{op} F \approx N - \text{jnte gav approximation}$$

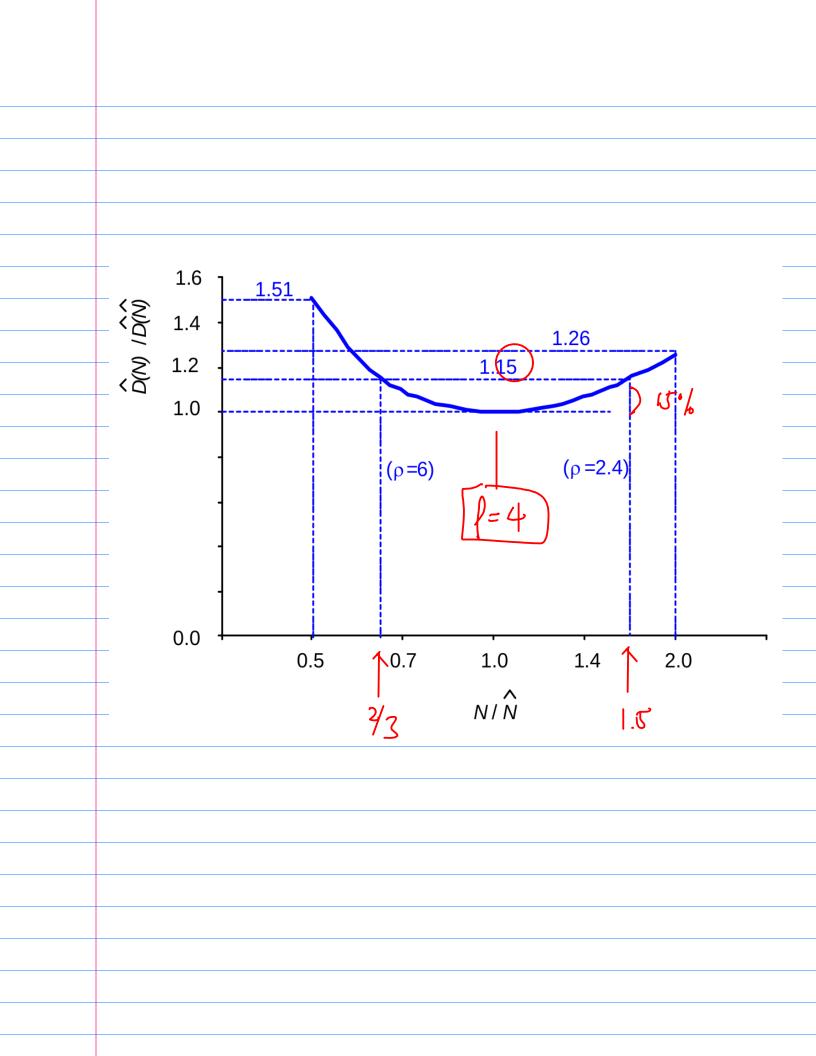

$$D(N) \qquad D(N)$$

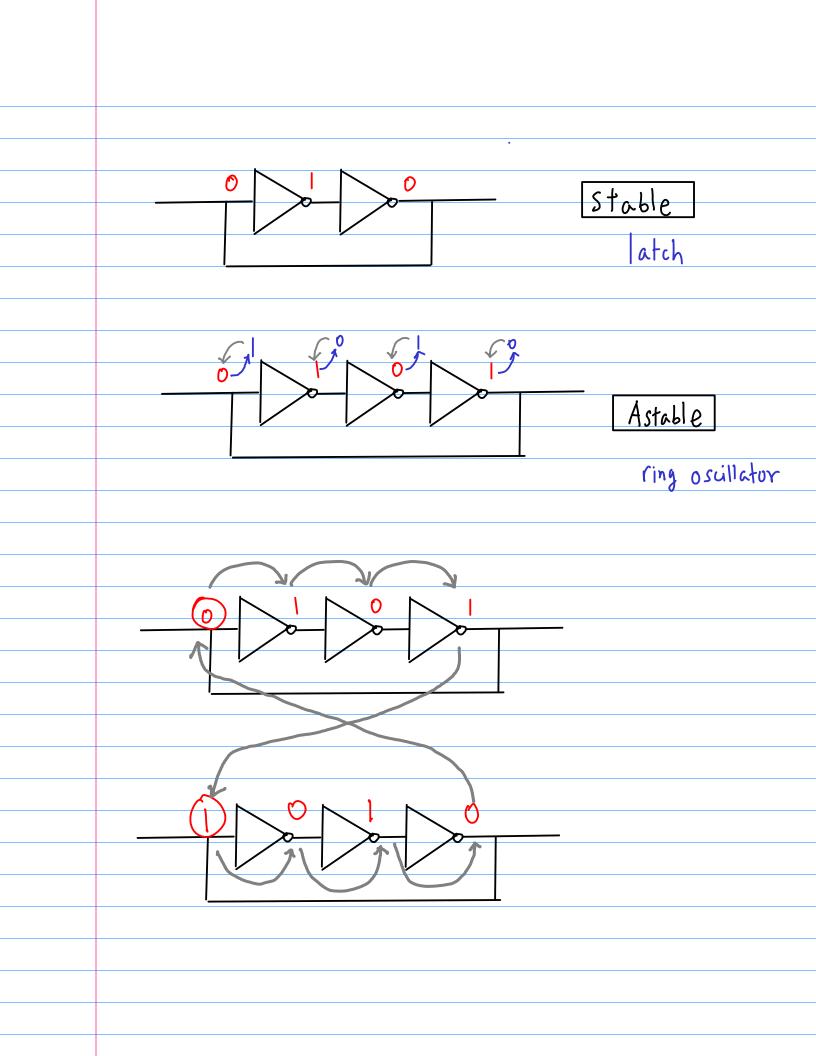

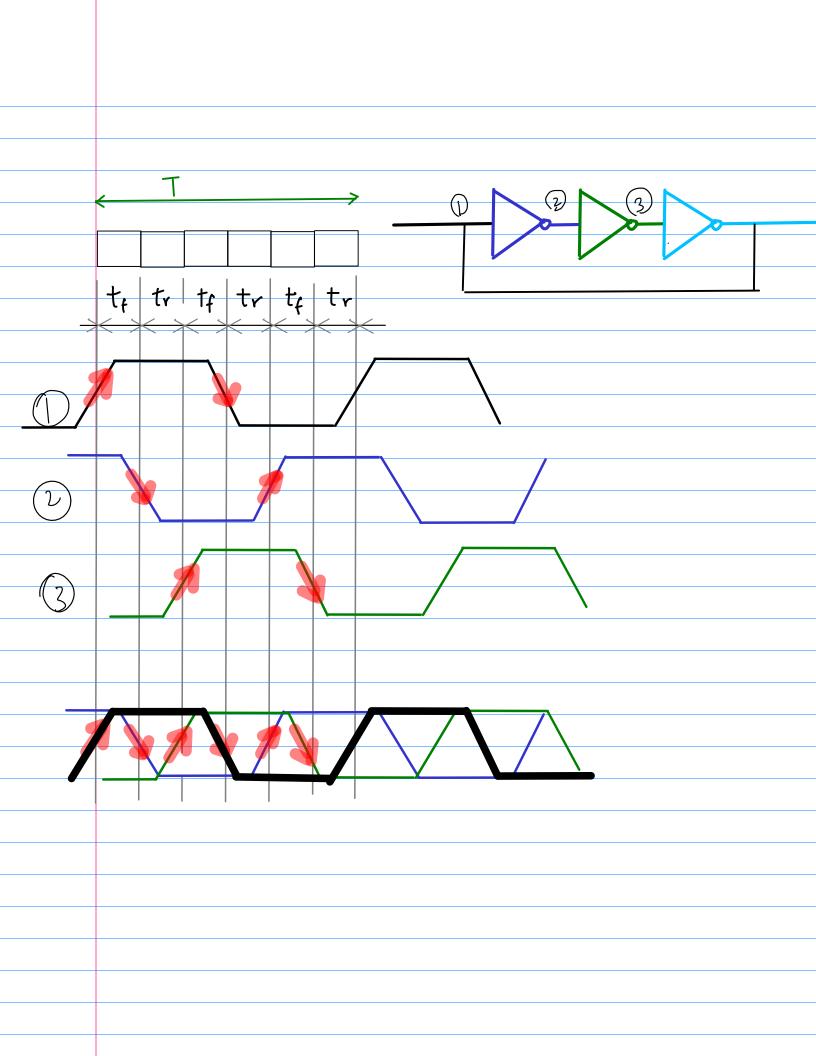

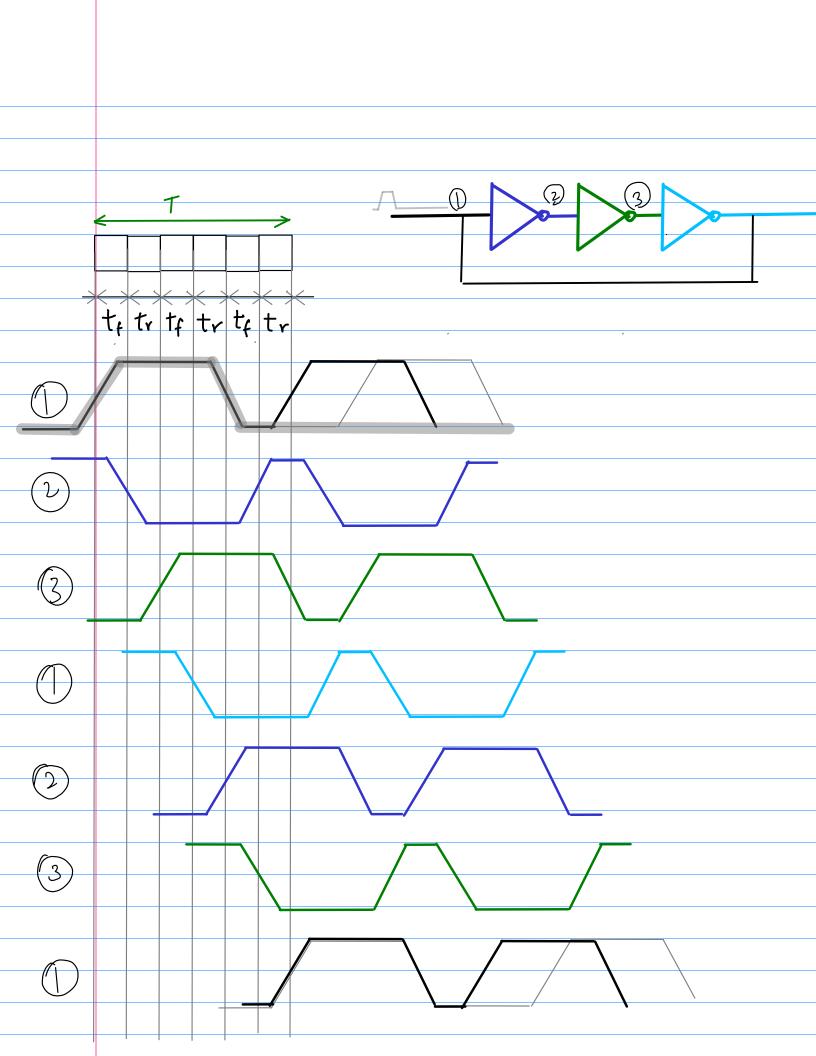

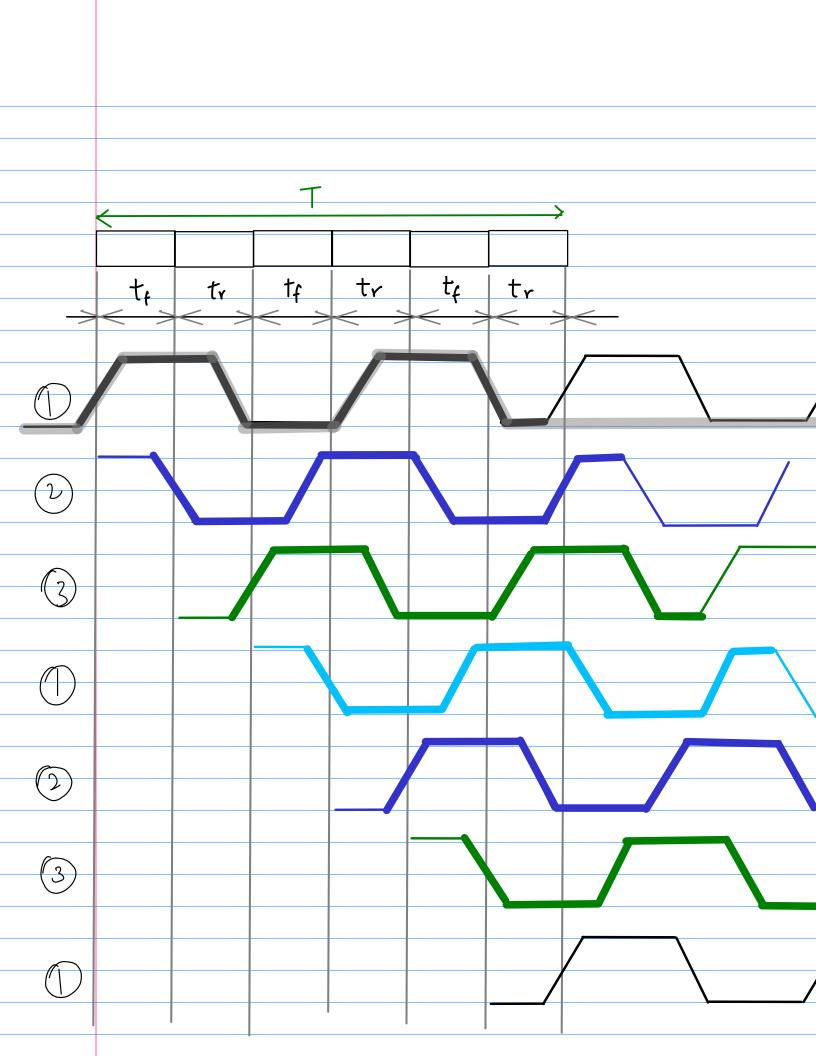

Ring Oscillators a uniform way of measuring  $t_p = \frac{t_{pr} + t_{pf}}{2}$ ring Oscillator Odd number of inventers Connected in circular chain

Odd Number of Inverters - 3 inverters 5 invaters 7 inverters Odd number of inverters No stable operating points -> Oscillating ring oscillator

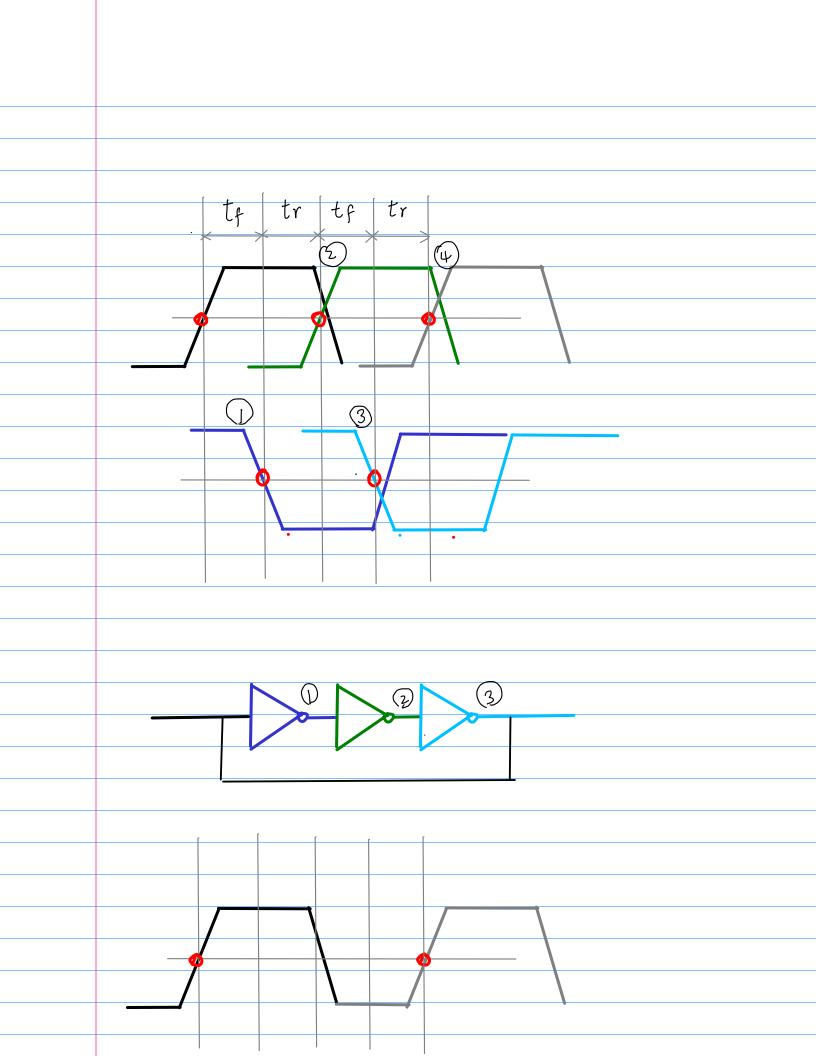

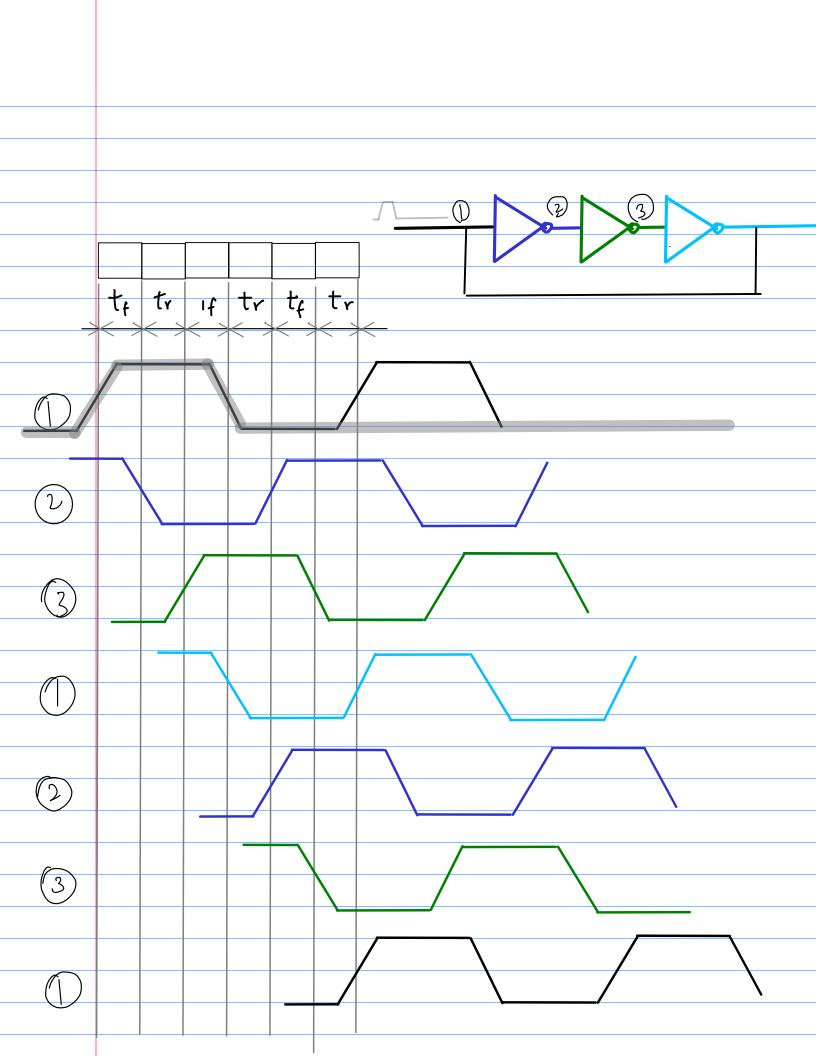

$T = 2 \cdot t_{P} \cdot N$ tp: propagation dulay N: # of inverters in chain T>> tf + tr - used to measure the average propagation delay of a typical inverter with minimum Capacitive Loading  $t\rho = \frac{1}{2.N}$ Characterise a particular design/fabrication process - used as a simple on chip clock

N inverters (odd number) g = <u>Cin</u> = <u>Cvef</u> = | h = Cout = Cref = |  $P = \left(\frac{C_{p, ref}}{C_{ref}}\right) = \left(\frac{\text{internal diffusion cap}}{\text{gate cap of ref inv}}\right) = \frac{3}{3} = 1$ d = gh + p = 2dass = 22  $J = yn + \gamma = 2$   $freg = \frac{1}{2N dabs} = \frac{1}{4N c}$