## CMOS Delay-4 (H.4) Device Delay (Inv, NAND, NOR)

20161105

Copyright (c) 2015 Young W. Lim.

Permission is granted to copy, distribute and/or modify this document under the terms of the GNU Free Documentation License, Version 1.2 or any later version published by the Free Software Foundation; with no Invariant Sections, no Front-Cover Texts, and no Back-Cover Texts. A copy of the license is included in the section entitled "GNU Free Documentation License".

|   | References                                                                        |

|---|-----------------------------------------------------------------------------------|

|   |                                                                                   |

|   |                                                                                   |

|   | Some Figures from the following sites                                             |

|   |                                                                                   |

|   | 1] http://pages.hmc.edu/harris/cmosvlsi/4e/index.html<br>Weste & Harris Book Site |

|   |                                                                                   |

| [ | [2] en.wikipedia.org                                                              |

|   |                                                                                   |

|   |                                                                                   |

|   |                                                                                   |

|   |                                                                                   |

|   |                                                                                   |

|   |                                                                                   |

|   |                                                                                   |

|   |                                                                                   |

|   |                                                                                   |

|   |                                                                                   |

|   |                                                                                   |

|   |                                                                                   |

|   |                                                                                   |

|   |                                                                                   |

|   |                                                                                   |

|   |                                                                                   |

|   |                                                                                   |

|   |                                                                                   |

|   |                                                                                   |

|   |                                                                                   |

•

.

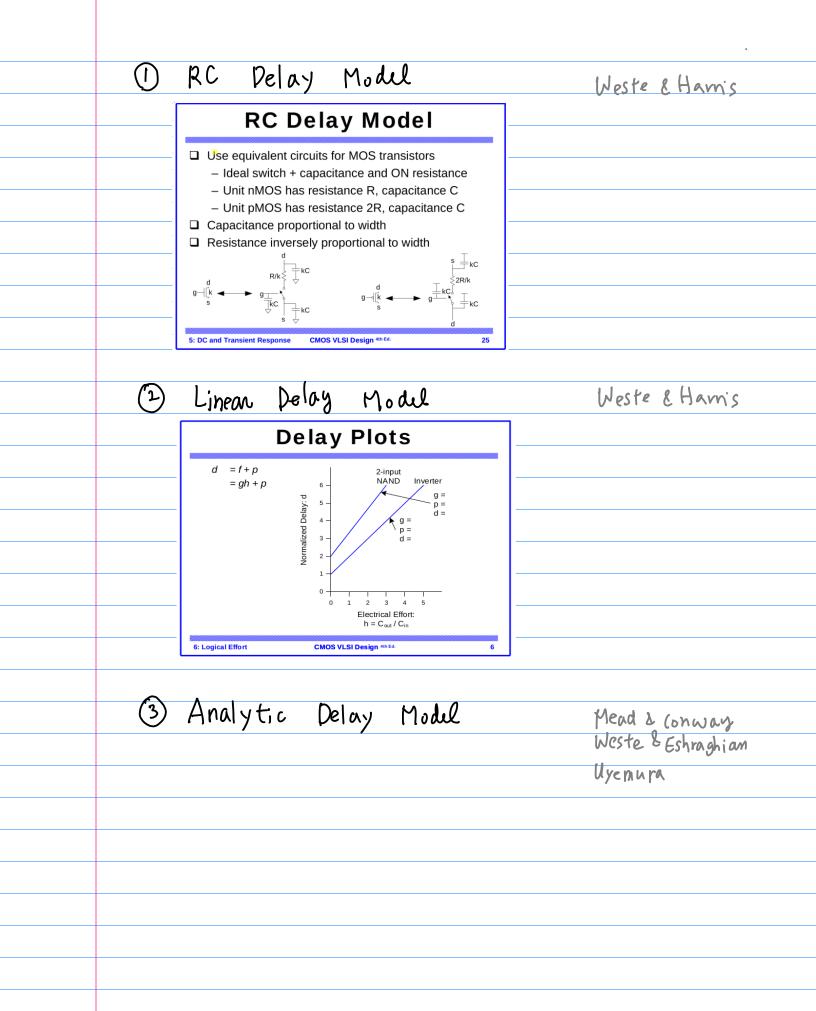

## MODEL

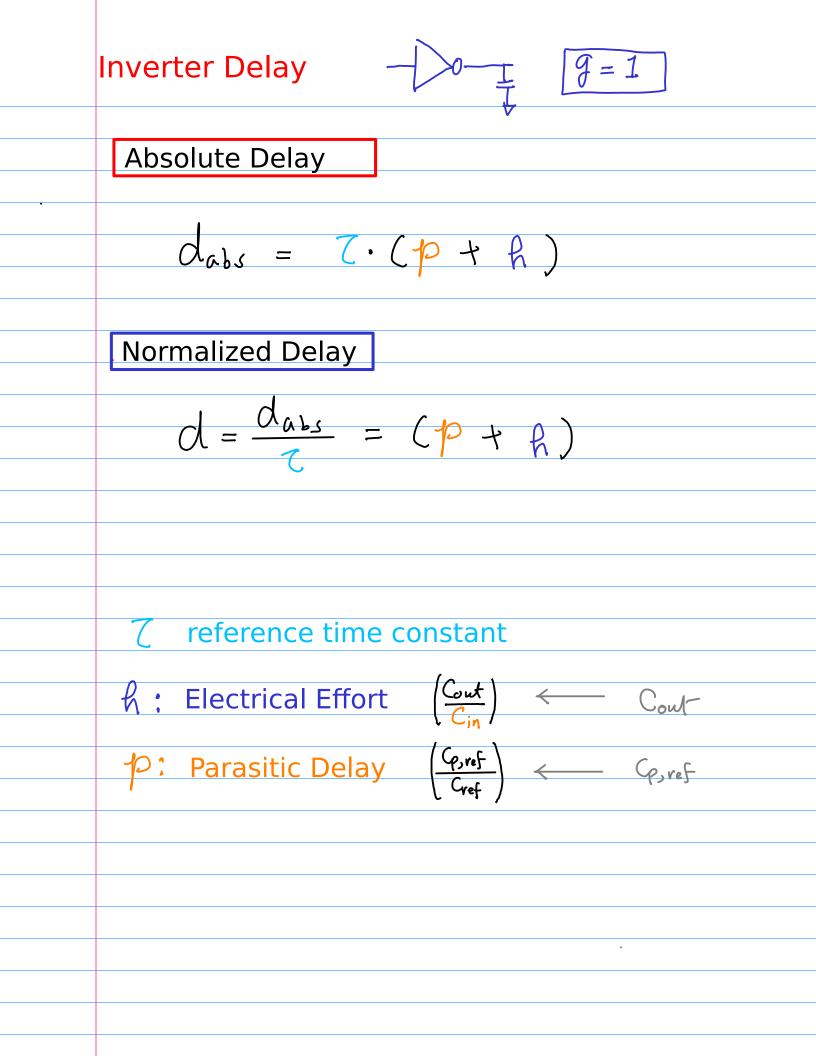

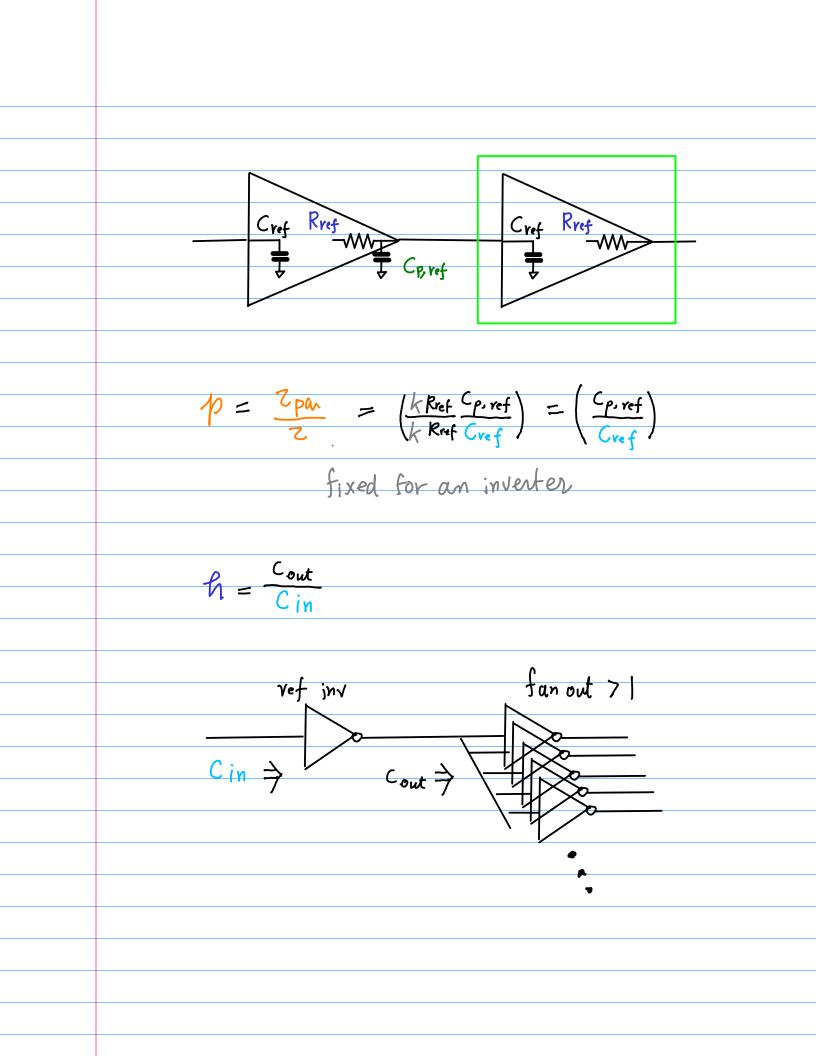

**Inverter Delay** for every kind of inverter g = 1 Cout Normalized Delay  $d = (p + g \cdot (k)) = (p + (k))$ = dabs Absolute Delay dabs = Zref (p+h)

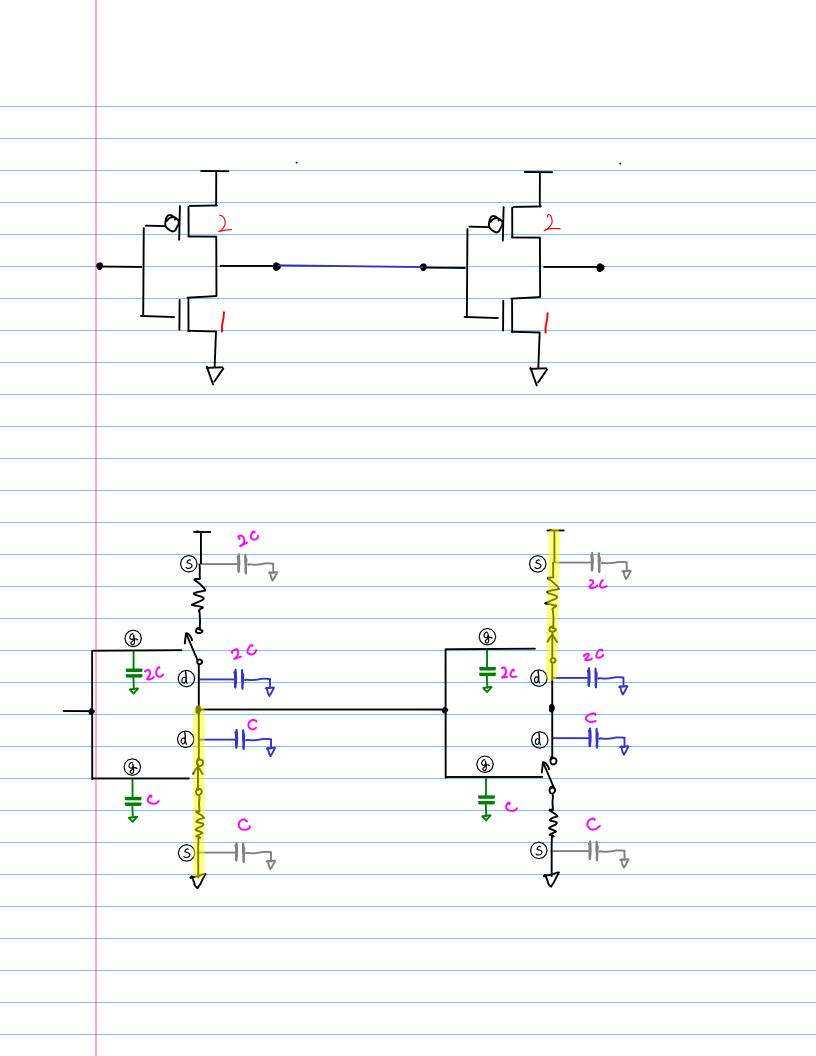

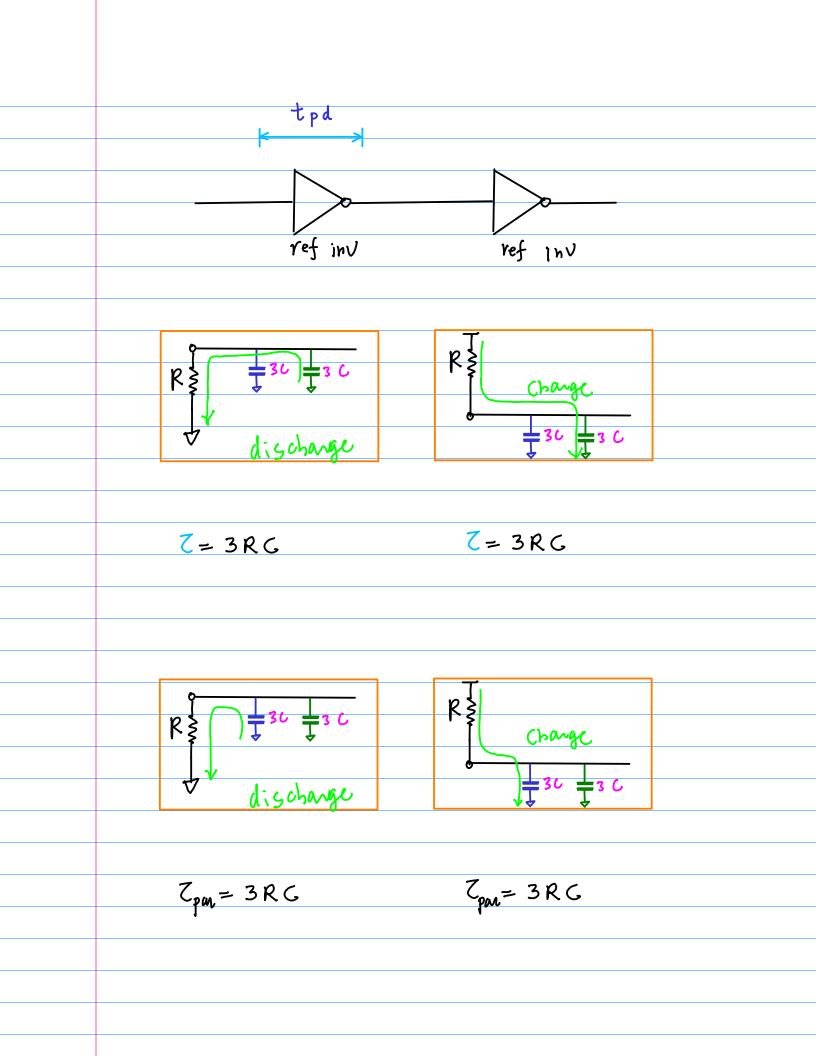

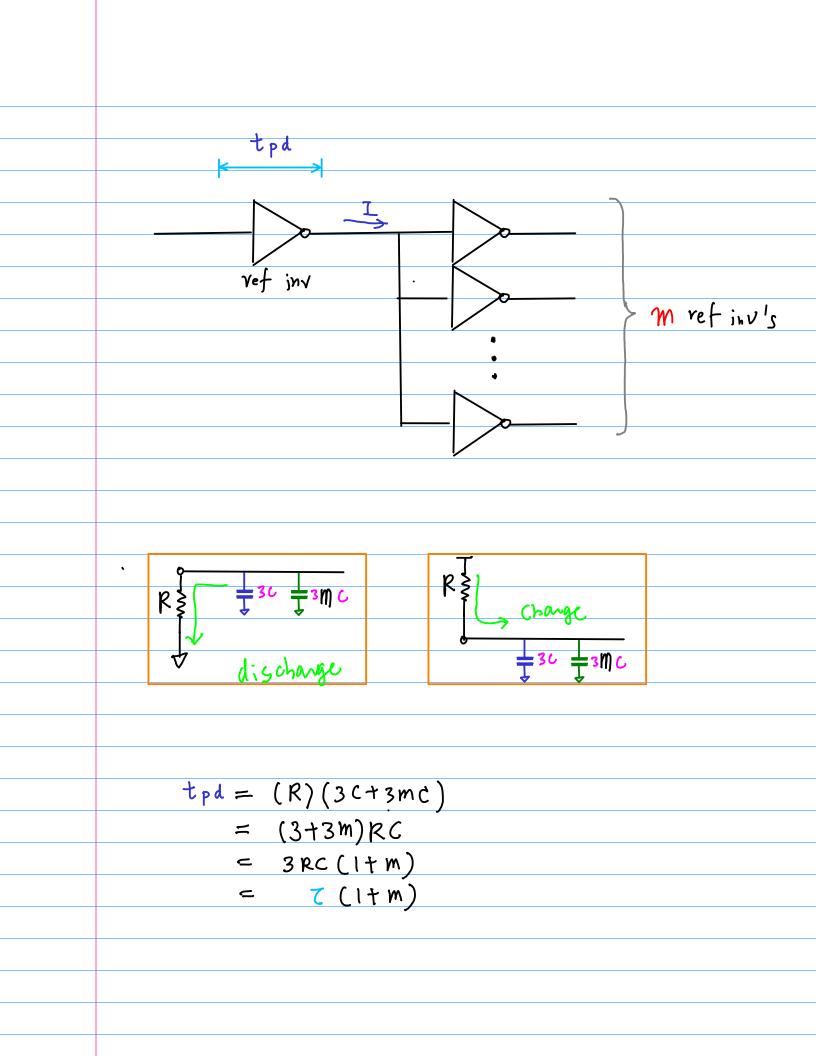

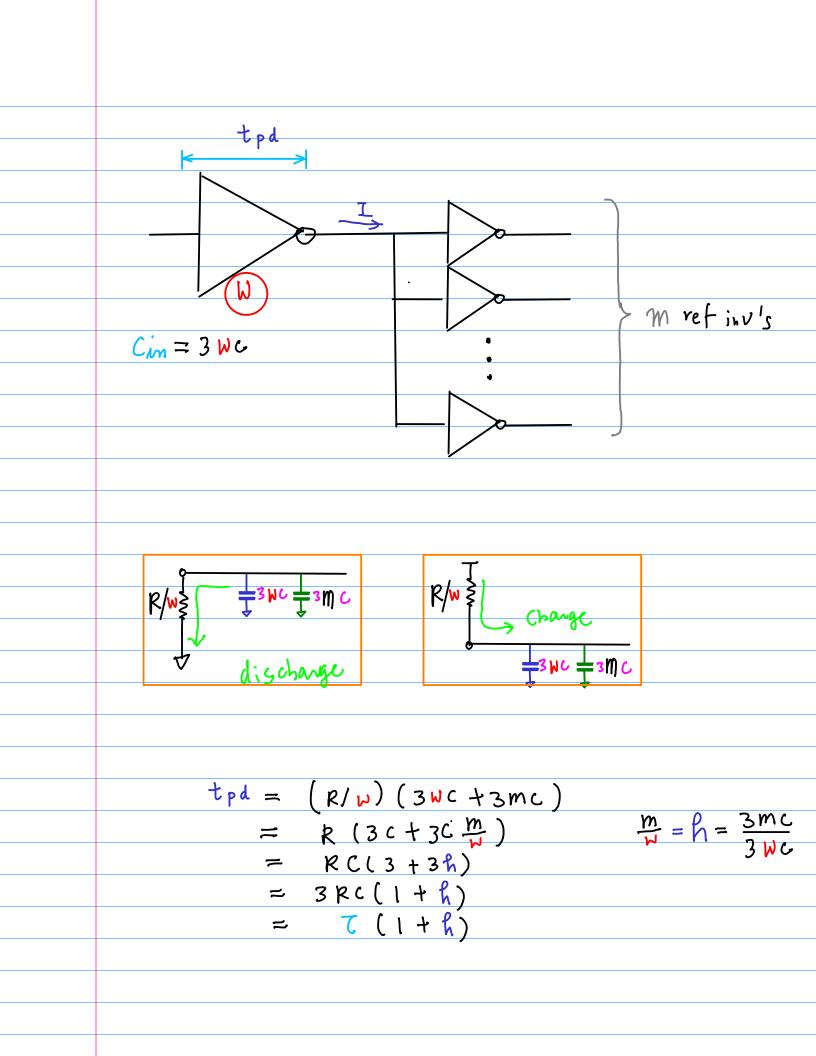

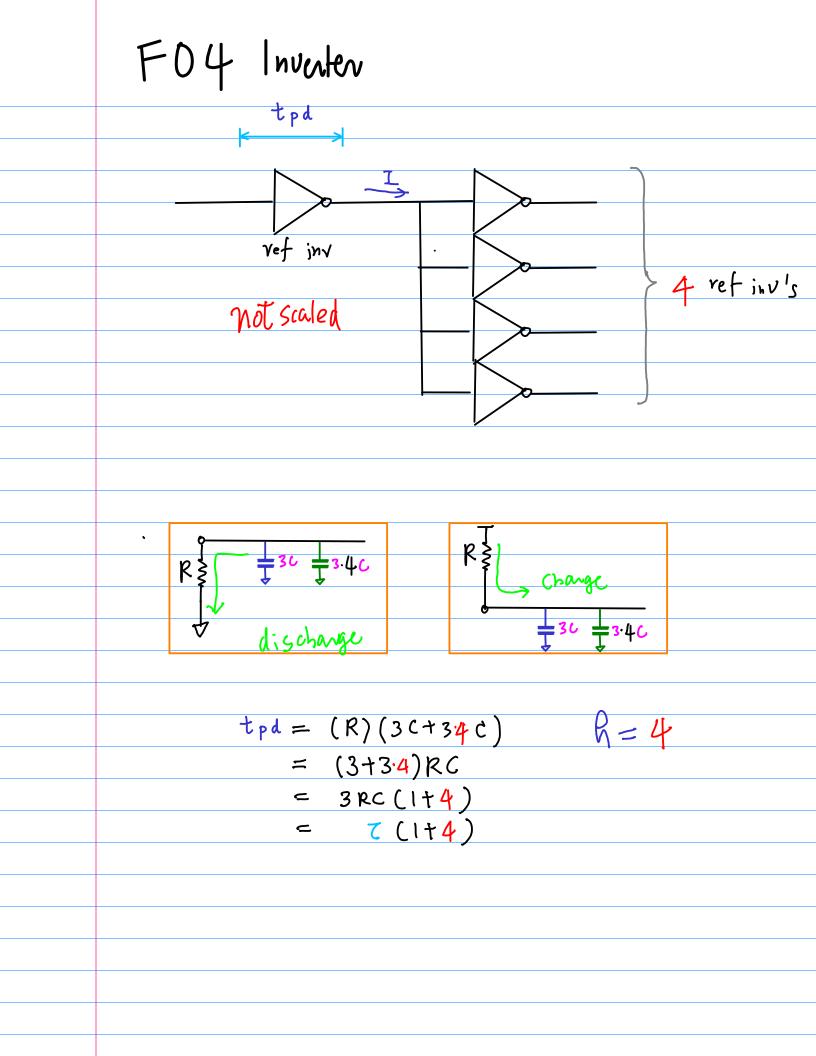

Propagation Delay tpd . vef jnv ref inv tpd fanout 71 vef jnv 50%, Jpp -> 50% Vpp

to get the same current, need bigger inverter tpd large load big inv R=>Rief RIS Cout <mark>⊢</mark>₅С Cin >> 5Cp sCp = RIS RCp

| •                         |                                       |                                               |

|---------------------------|---------------------------------------|-----------------------------------------------|

| fall time                 | t <sub>f</sub> =                      | $0.9 \ V_{pp} \rightarrow 0.1 \ V_{pp}$       |

| <br>rise time             | tr =                                  | $0.  \vee_{pp} \longrightarrow 0.9 \vee_{pp}$ |

| propagation delay time    | $t_p = \frac{1}{2} (t_{pf} + t_{pr})$ | 0.5 Vpp -> 0.5 Vpp                            |

| <br>propagation fall time | tpf                                   | $V_{PP} \rightarrow 0.5 V_{Pp}$               |

| <br>propagation rise time | tpr                                   | $0 \rightarrow 0.5 V_{Pb}$                    |

|                           |                                       | •                                             |

|                           |                                       |                                               |

|                           |                                       |                                               |

|                           |                                       |                                               |

|                           |                                       |                                               |

|                           |                                       |                                               |

|                           |                                       |                                               |

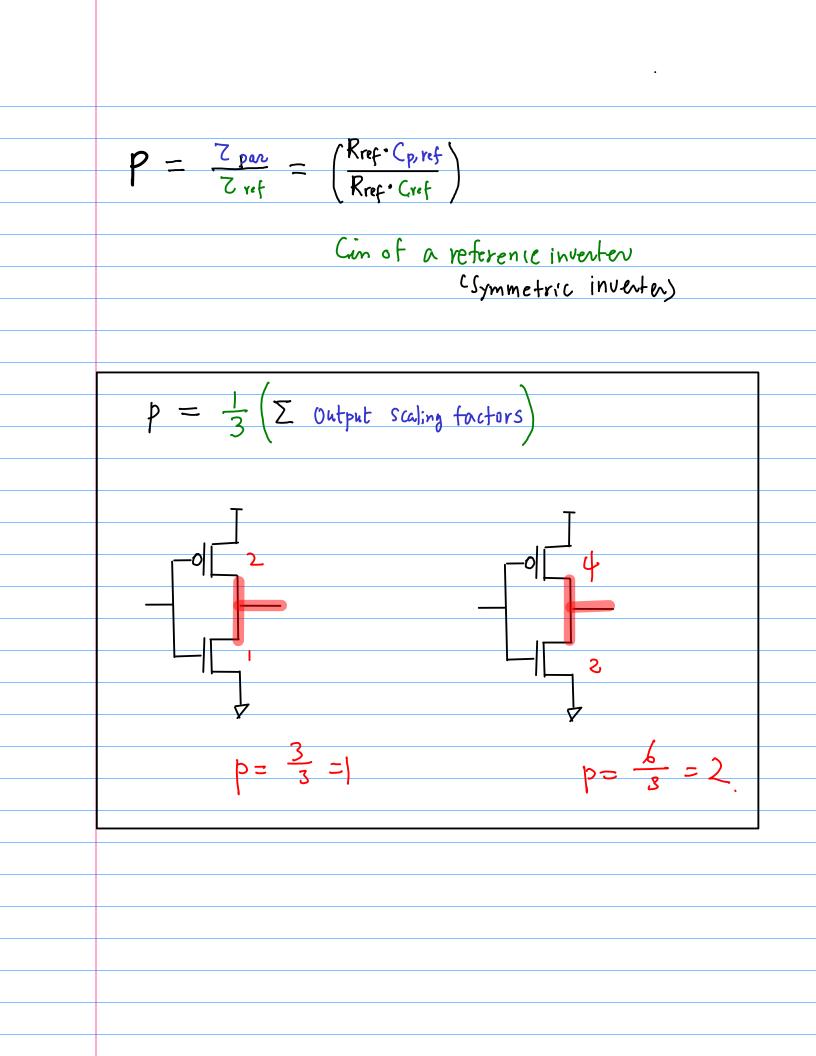

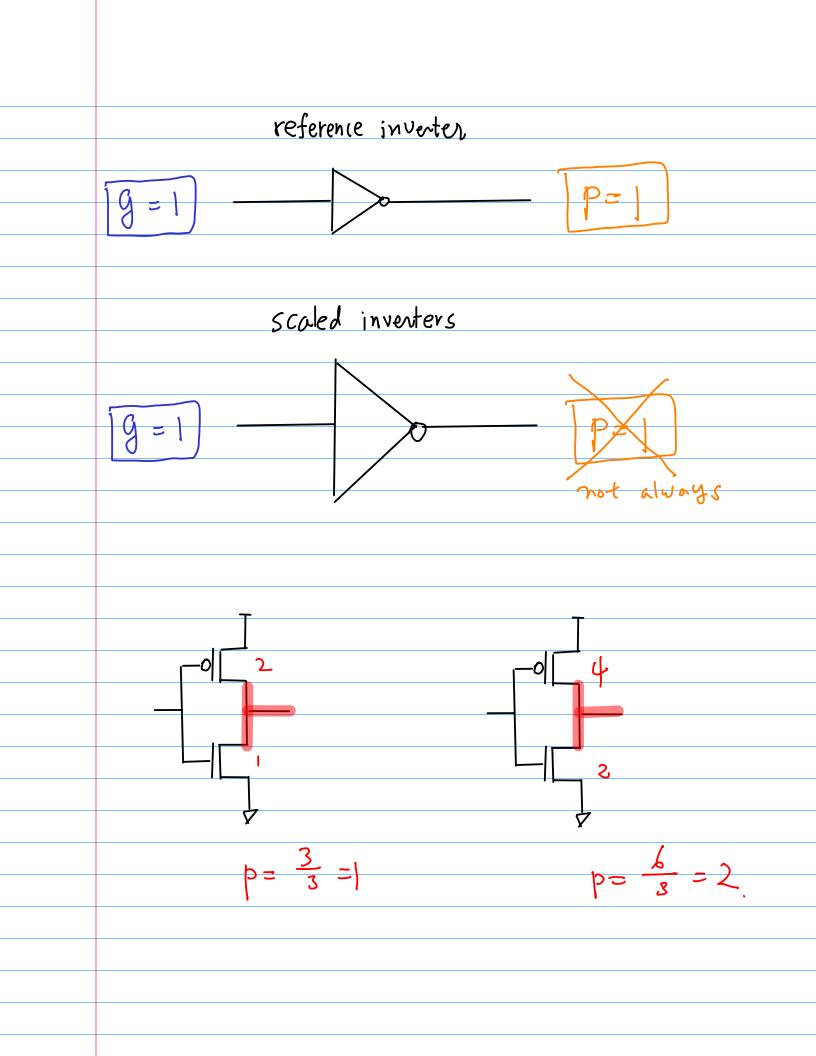

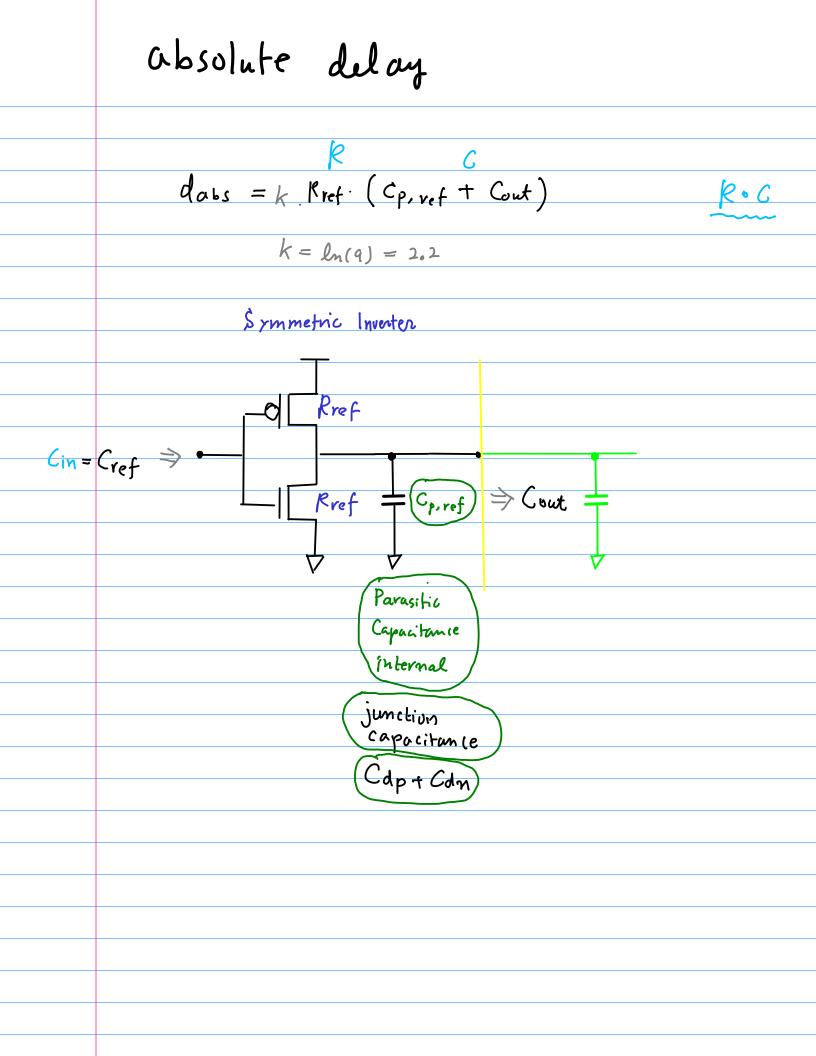

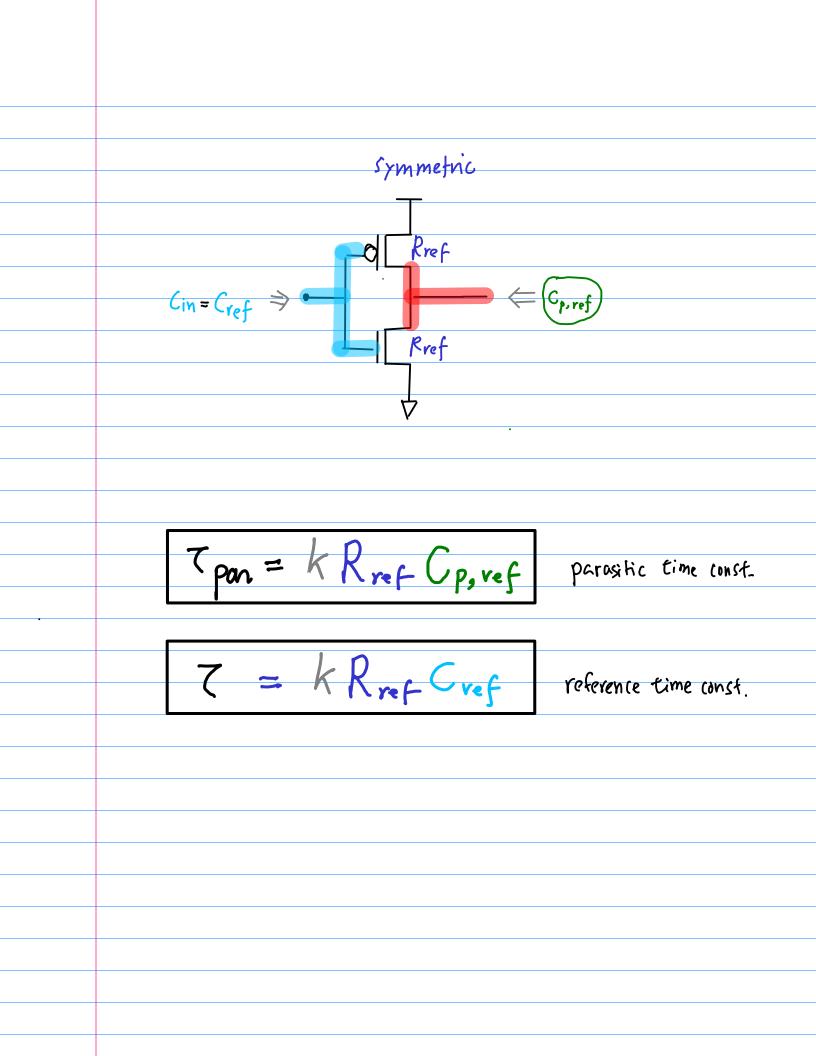

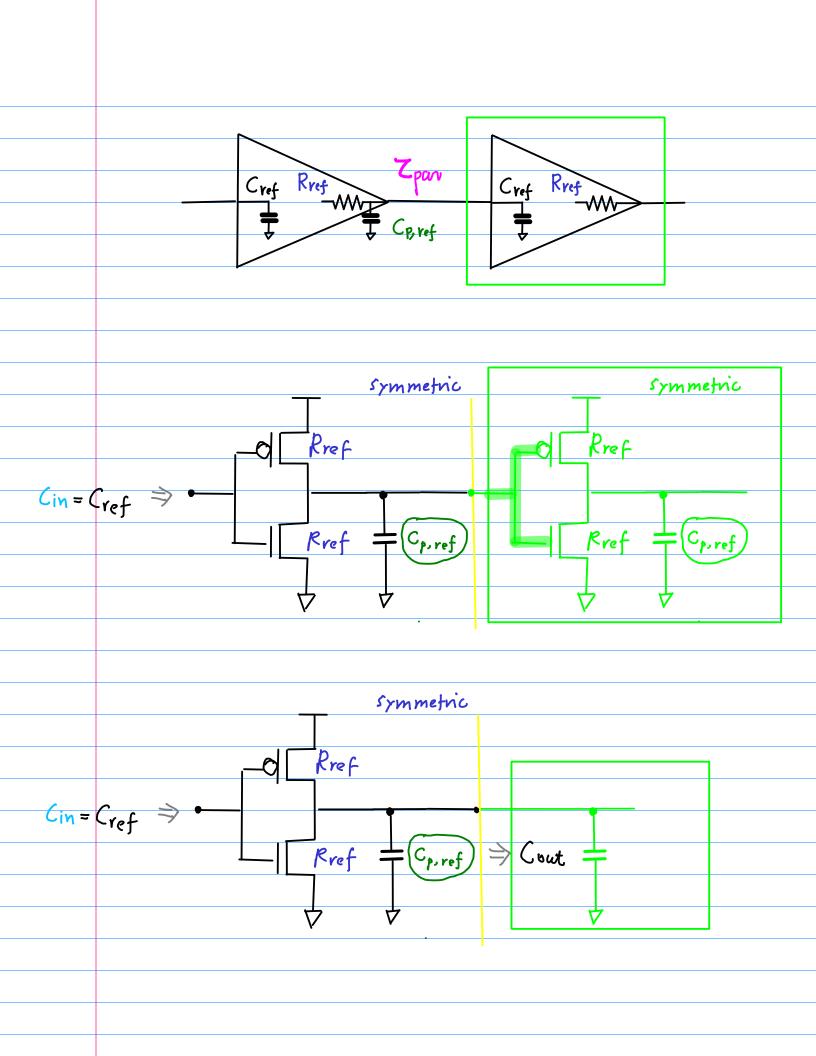

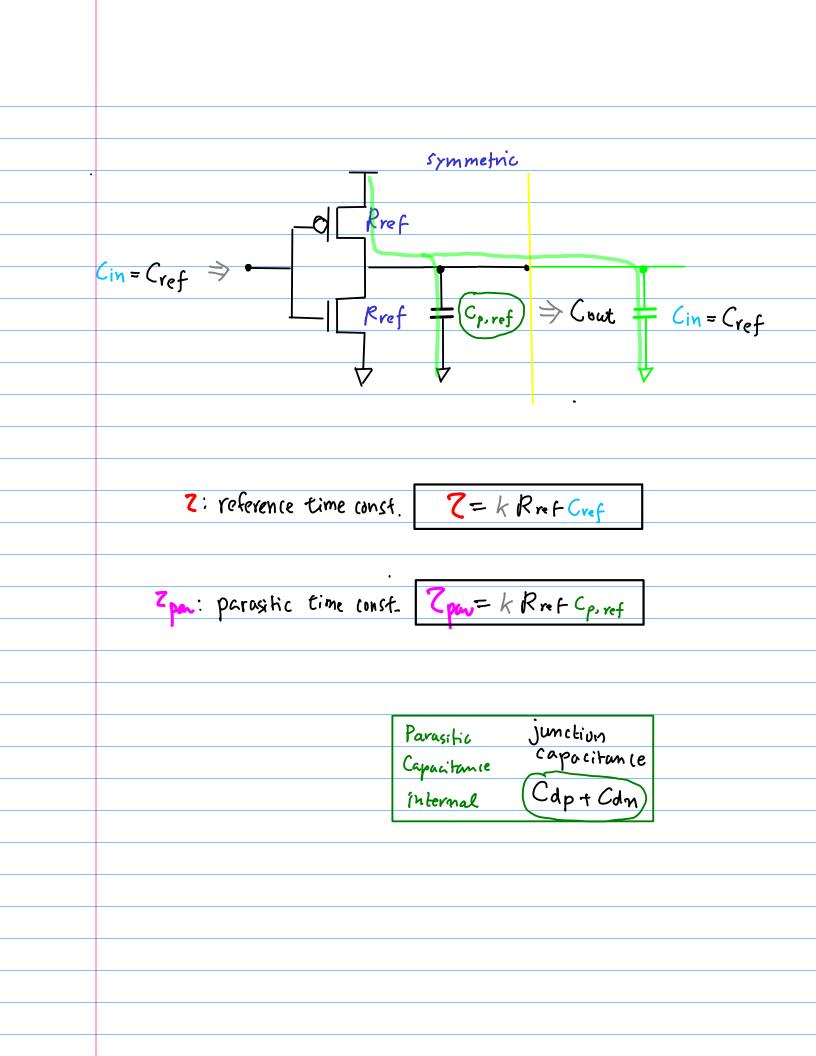

parasitic delay (P) - delay due to internal sCp parasitic capacitance - Excluding external load cap (Cout) - count only diffusion capacitance of the output - delay without output load Cdp+Cdn) drain parasitic cap P = Cref Cin of the ref inventer (Symmetric Inventer)

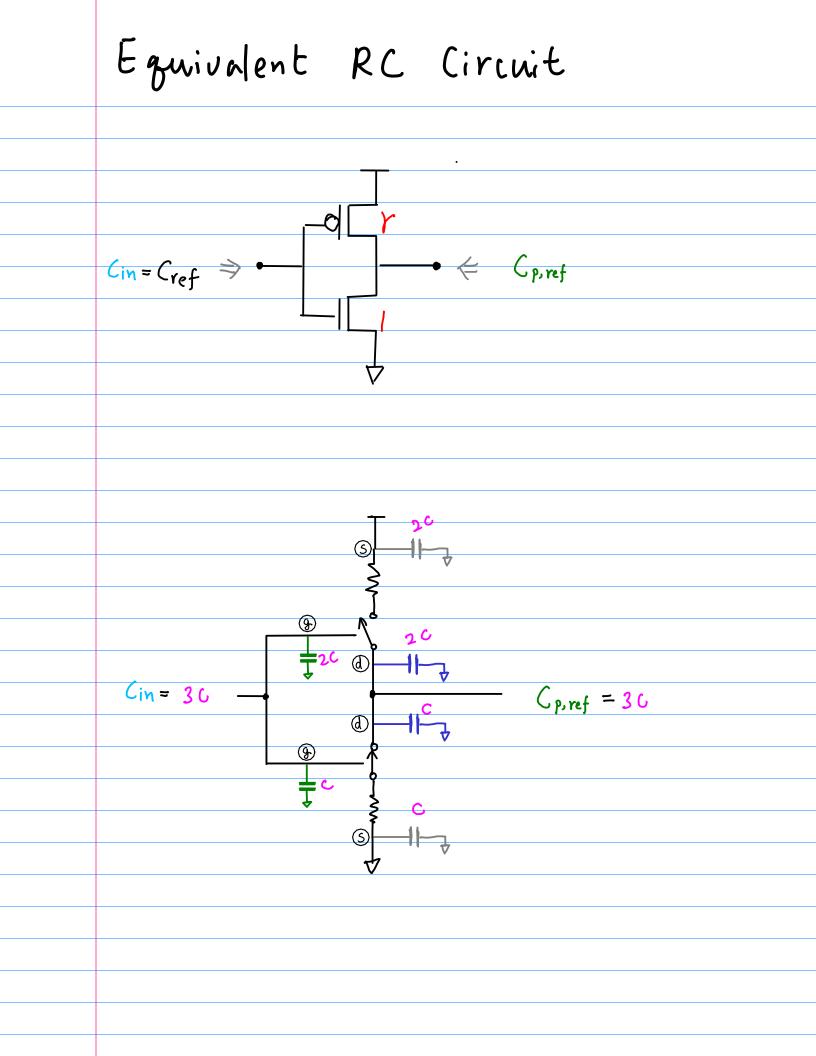

R= Rief Cout =<mark>૬</mark>િ Cin > SCp sCp = RIS RCp  $\left(\frac{C_{p,ref}}{C_{ref}}\right) = \left(\frac{internal diffusion cap}{gate cap of ref inv}\right)$ P =  $= \frac{7 \text{ par}}{7 \text{ ref}} = \left(\frac{\text{Rref} \cdot \text{Cp, ref}}{\text{Rref} \cdot \text{Cy} \cdot \text{F}}\right)$ Cin of a reference inventer CSymmetric inventer)

For the ref inventer dabs = Zref (h+1)  $d = \frac{da_{bs}}{Z_{ref}} = (h+1)$

Scaling Factor \$ >1

$R = \frac{R_{ref}}{s}$  $C_p = S \cdot C_{p, ref}$  $C_{in} = S C_{ref}$ dabs = k Kref (Cp, ref + Cout) Ofter scaling  $\Longrightarrow k \frac{Rref}{S} (S \cdot C_{p,ref} + Cout)$ = k Rref Cpref + k Rref Cout = k Rref Cp, ref + k Rref (Cout) Cref Cin=Cref = k Rref Cp. ref + k Rref (Cout Cin) Cref = k Rref Cref (Cp, ref Cref) + k Rref Cref (Cout)

$$d_{abs} = k Rnt Cost \left(\frac{C_{P} nt}{C_{eq}}\right) + k Rnt Cost \left(\frac{C_{est}}{C_{in}}\right)$$

$$= \left(k Rnt Cost \left(\frac{k Rut}{k Rut}\right) - \frac{c_{est}}{c_{in}}\right)\right)$$

$$= \left(2 \left(\frac{k Rut}{c_{in}}\right) + \left(\frac{C_{out}}{C_{in}}\right)\right)$$

$$= 2 \left(p + h\right)$$

$$= 2 \left(p + h\right)$$

$$= 2 \cdot h$$

$$Tpan = k Rnt Cp, vsf parashic time tenst.$$

$$T = k Rnt Cost reference time const.$$

$$Tpan = T \cdot \rho$$

$$d_{abs} = T \cdot d$$

7= k Rref Cref reference time const. Cref Rref Cref Rref Ĵ 7pm= k Rref Cp. ref parasitic time const. Rref Cp. ref Cref Rref Cref

Electrical Effort  $h = \frac{C_{out}}{C_{in}}$ Panasitic Delay  $p = \frac{2pan}{2} = \left(\frac{kRref}{kRref}\frac{C_{p,ref}}{C_{ref}}\right) = \left(\frac{C_{p,ref}}{C_{ref}}\right)$ Symmetric Rref d Cin=Cref > •  $Rref = C_{p,ref} \Rightarrow Cout = = C_{ref}$ Zpur 7

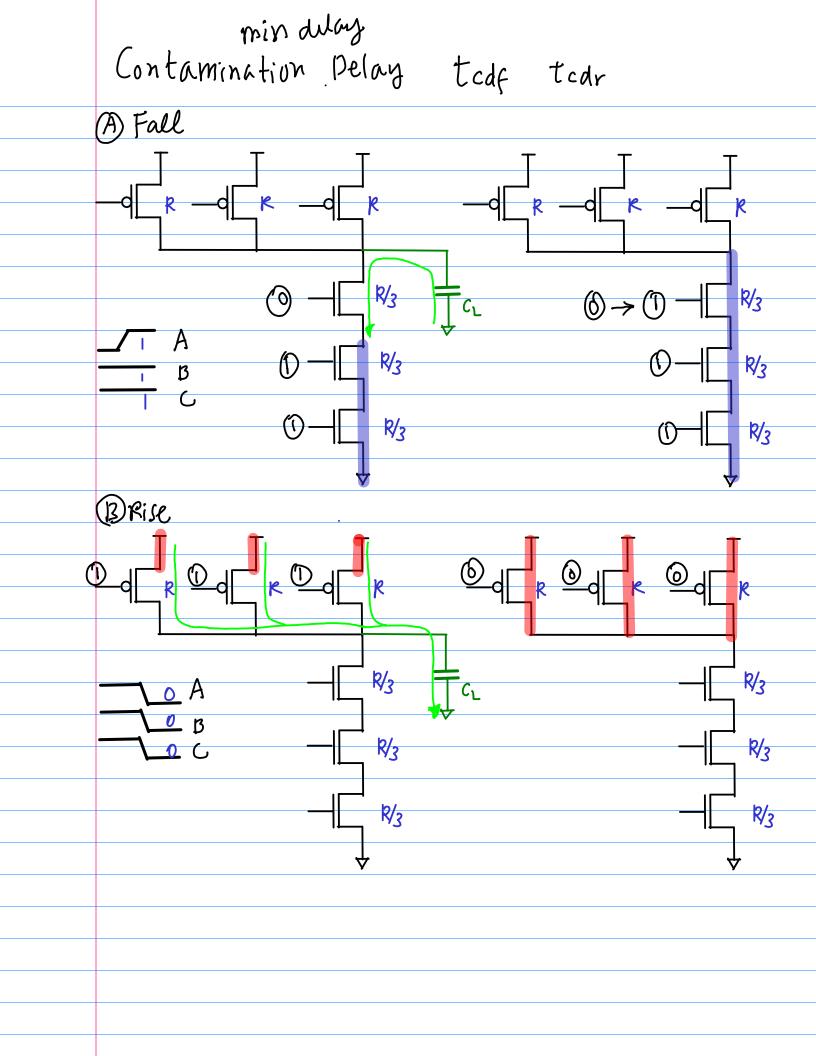

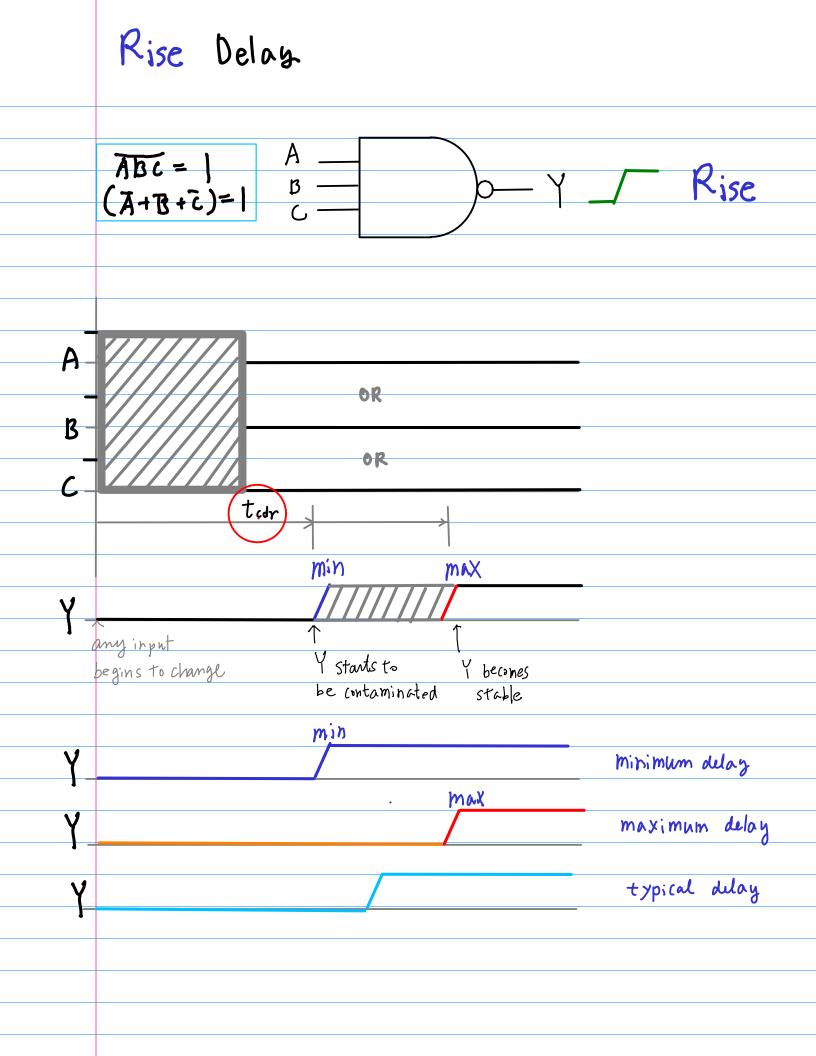

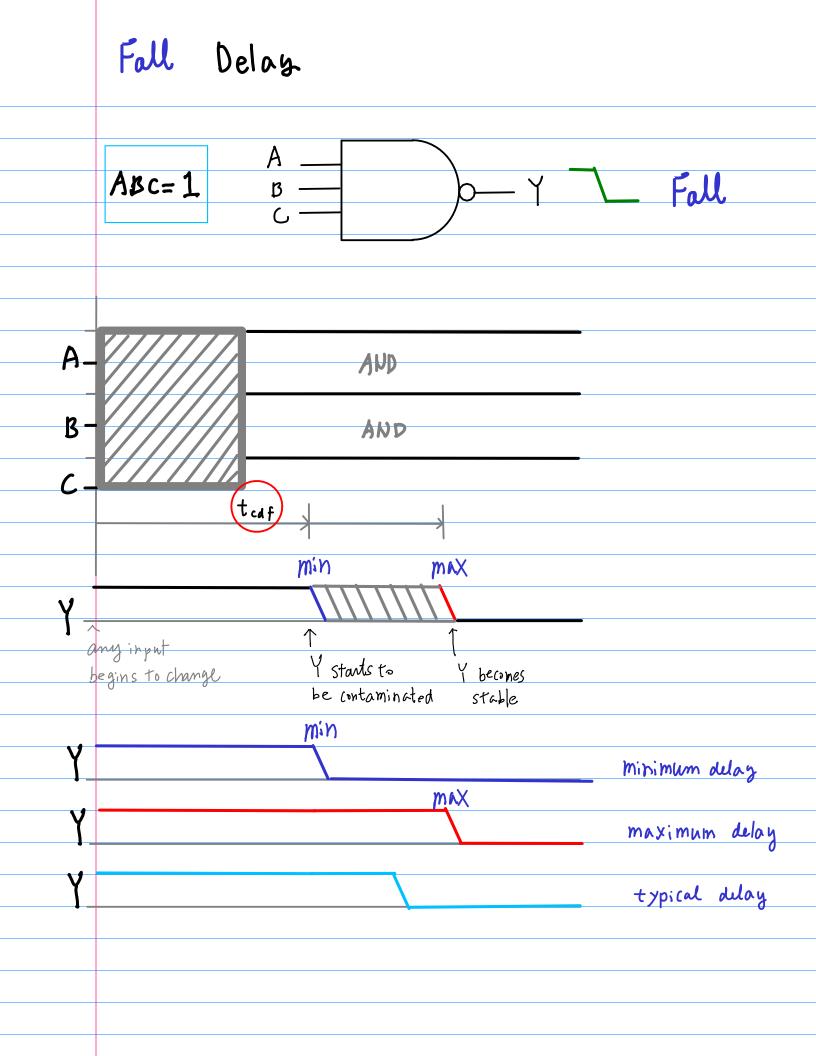

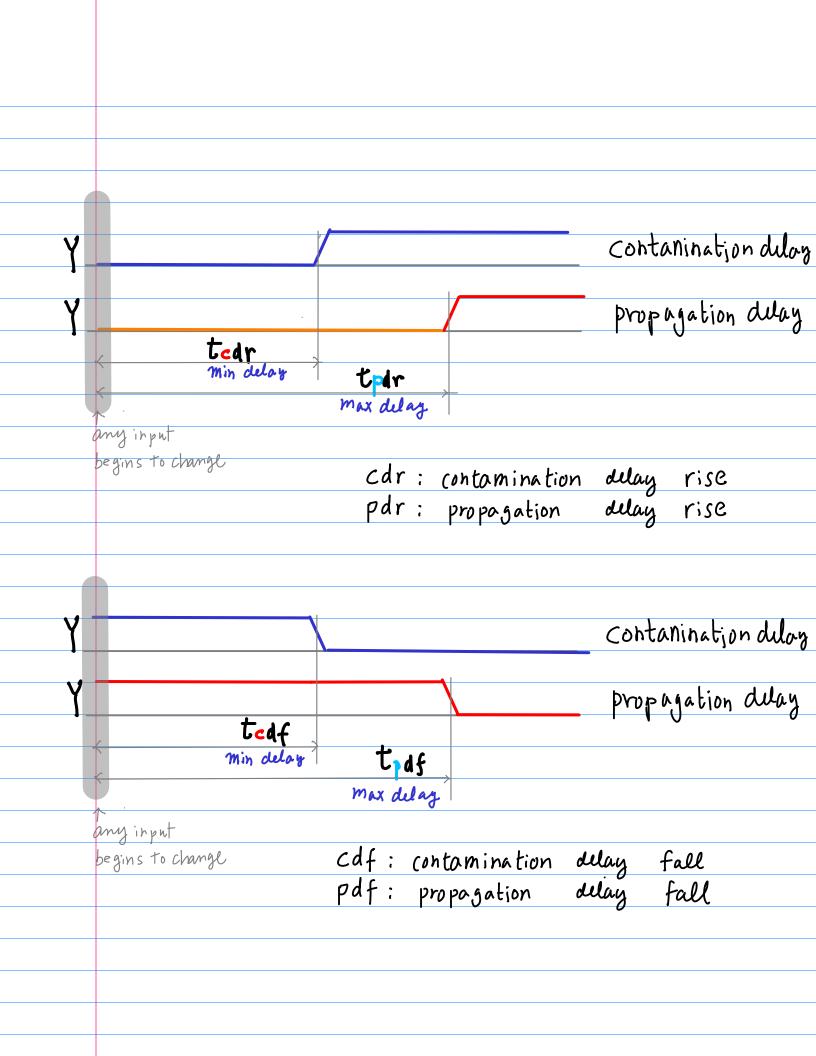

## **Contamination Delay**

In digital circuits, the contamination delay (denoted as tcd) is the minimum amount of time from when an input changes until any output starts to change its value.

This change in value does not imply that the value has reached a stable condition.

The contamination delay only specifies that the output rises (or falls) to 50% of the voltage level for a logic high.

The circuit is guaranteed not to show any output change in response to an input change before tcd time units (calculated for the whole circuit) have passed.

The determination of the contamination delay of a combined circuit requires identifying the shortest path of contamination delays from input to output and by adding each tcd time along this path.

https://en.wikipedia.org/wiki/Contamination\_delay

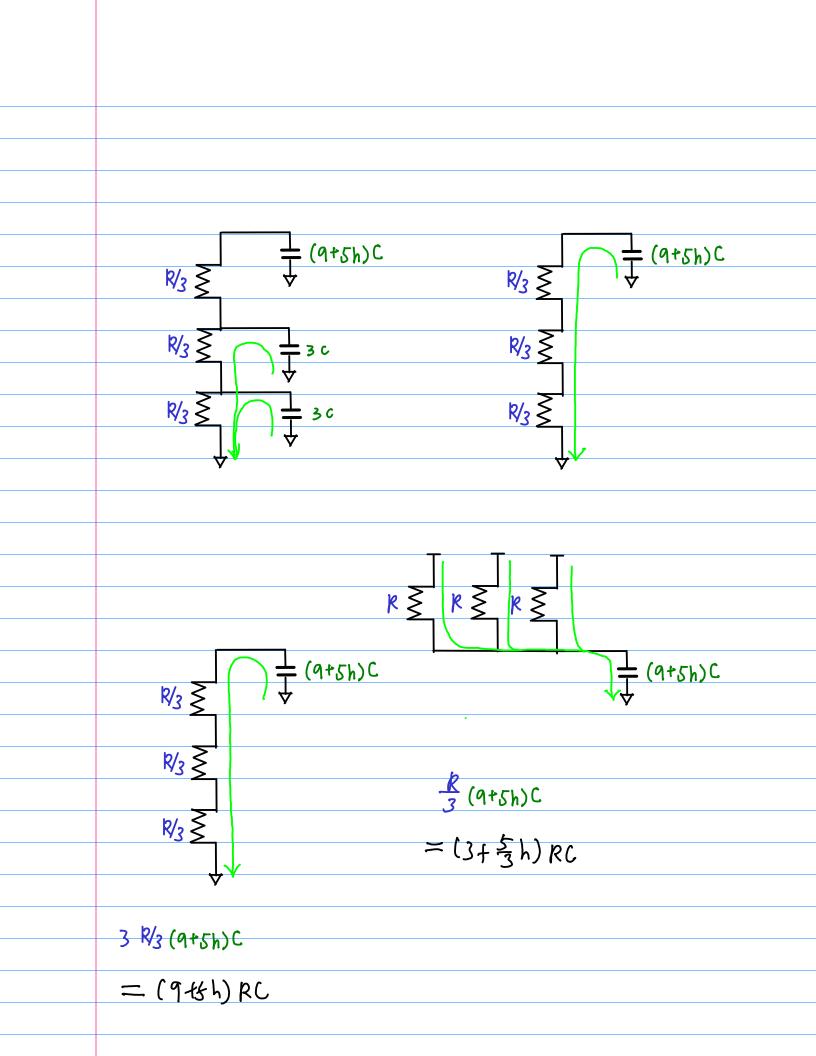

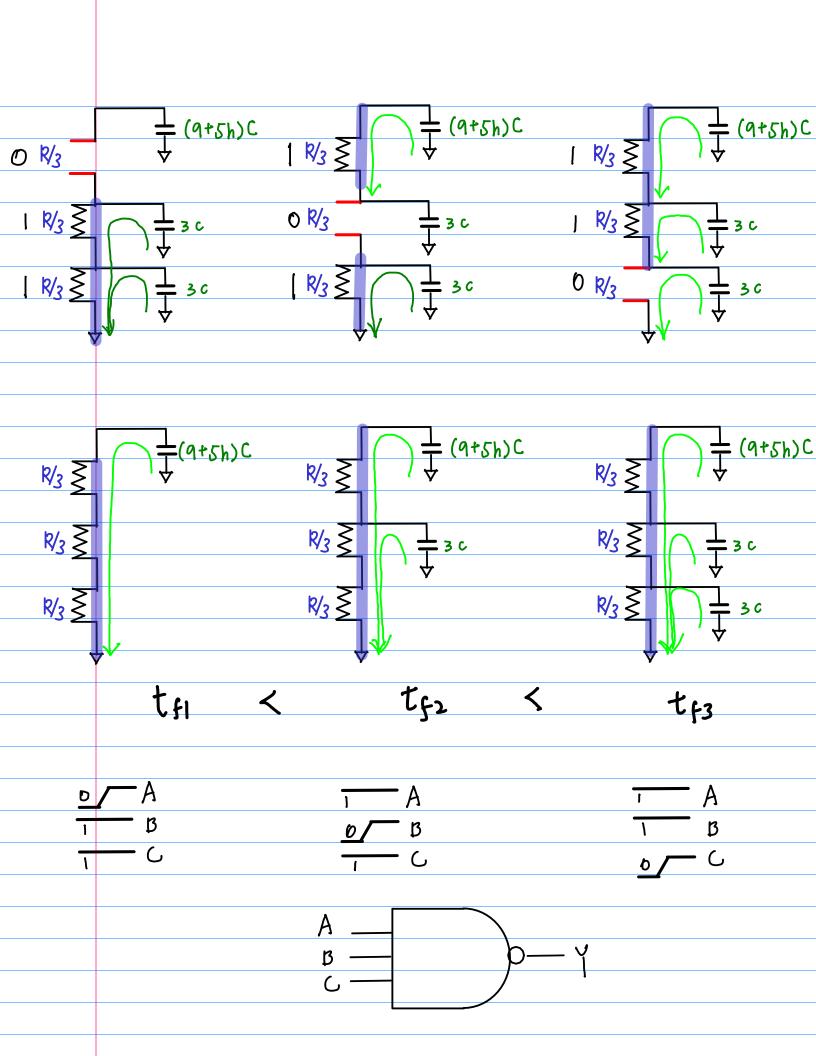

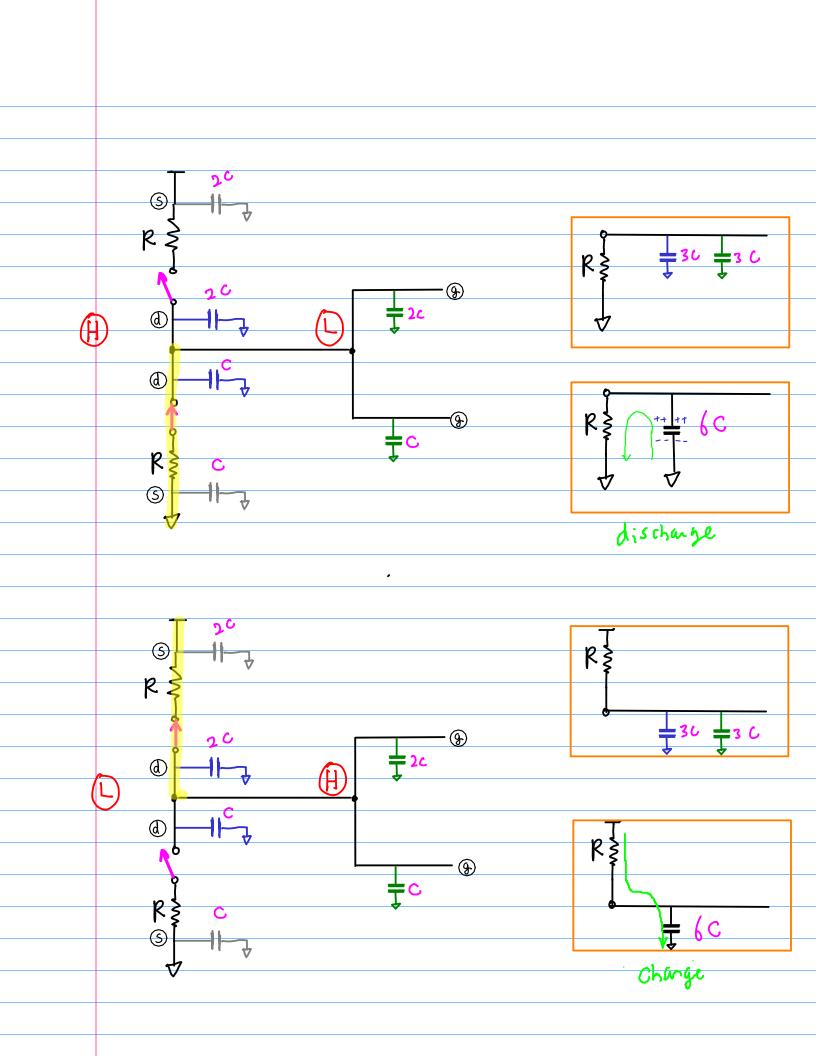

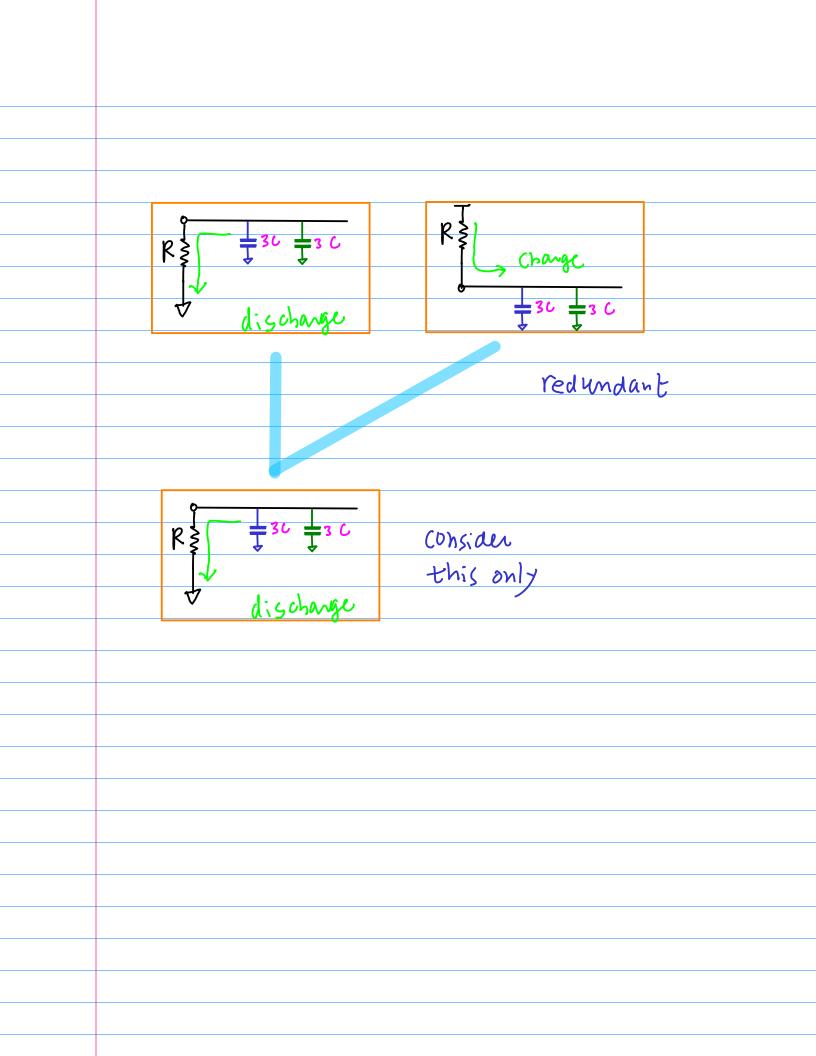

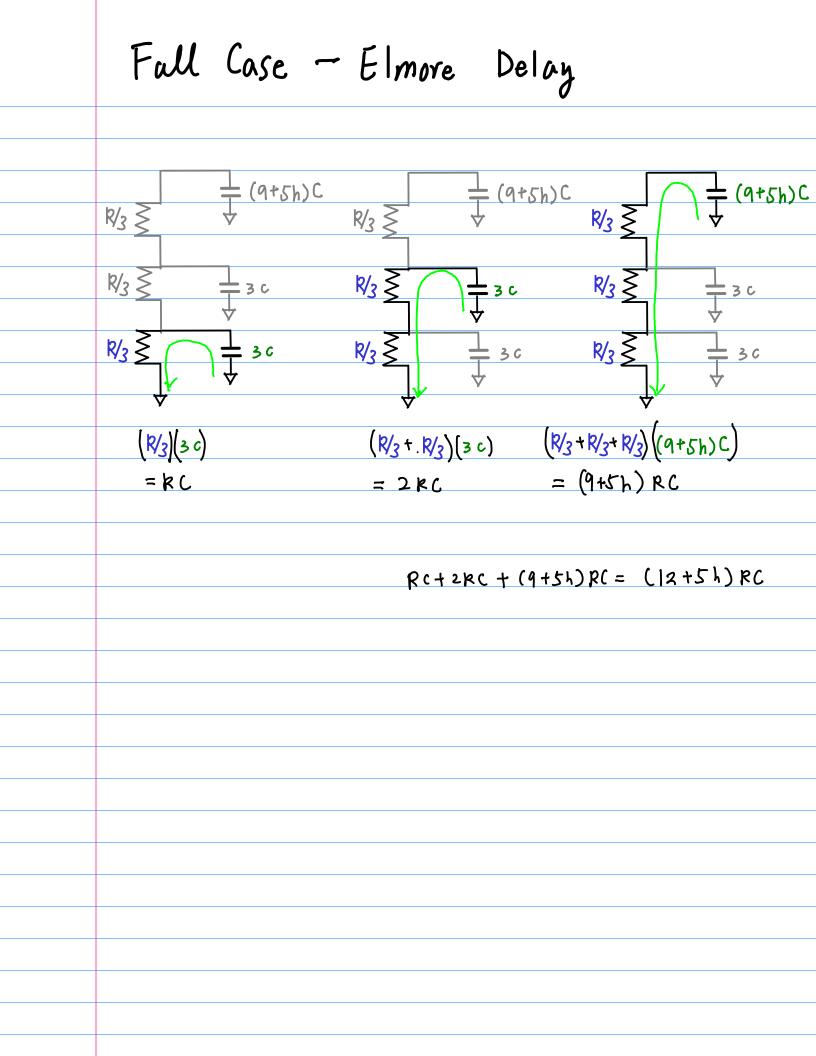

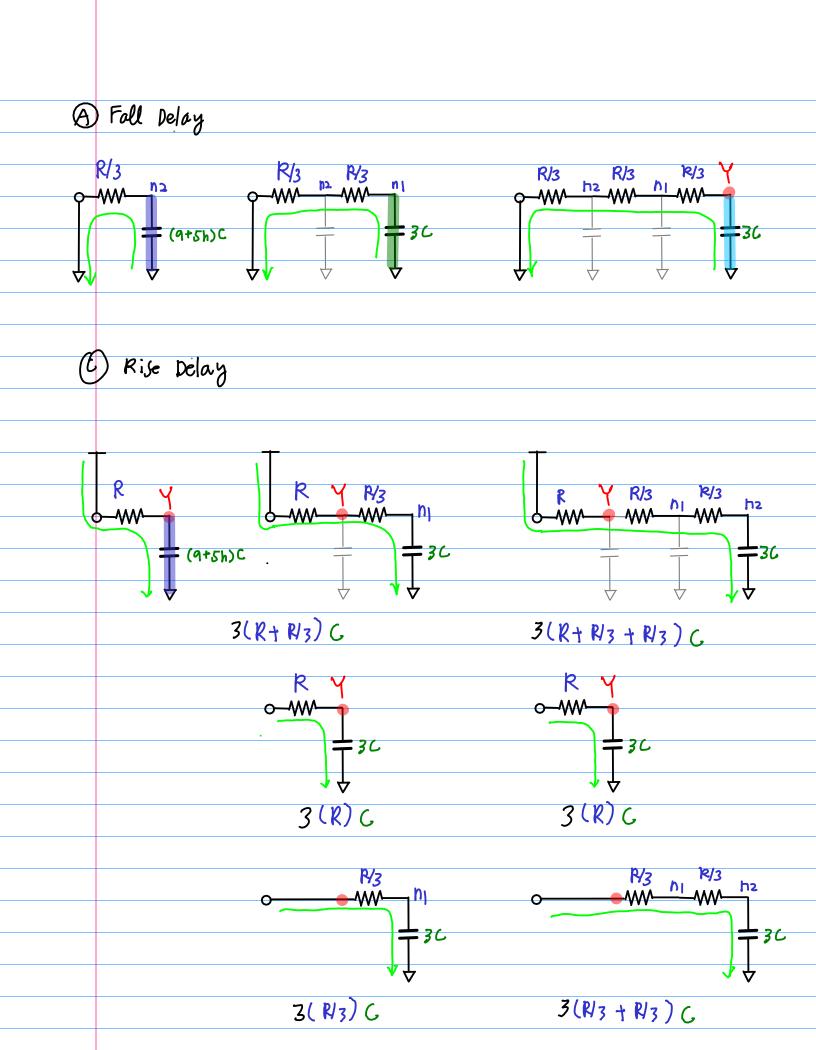

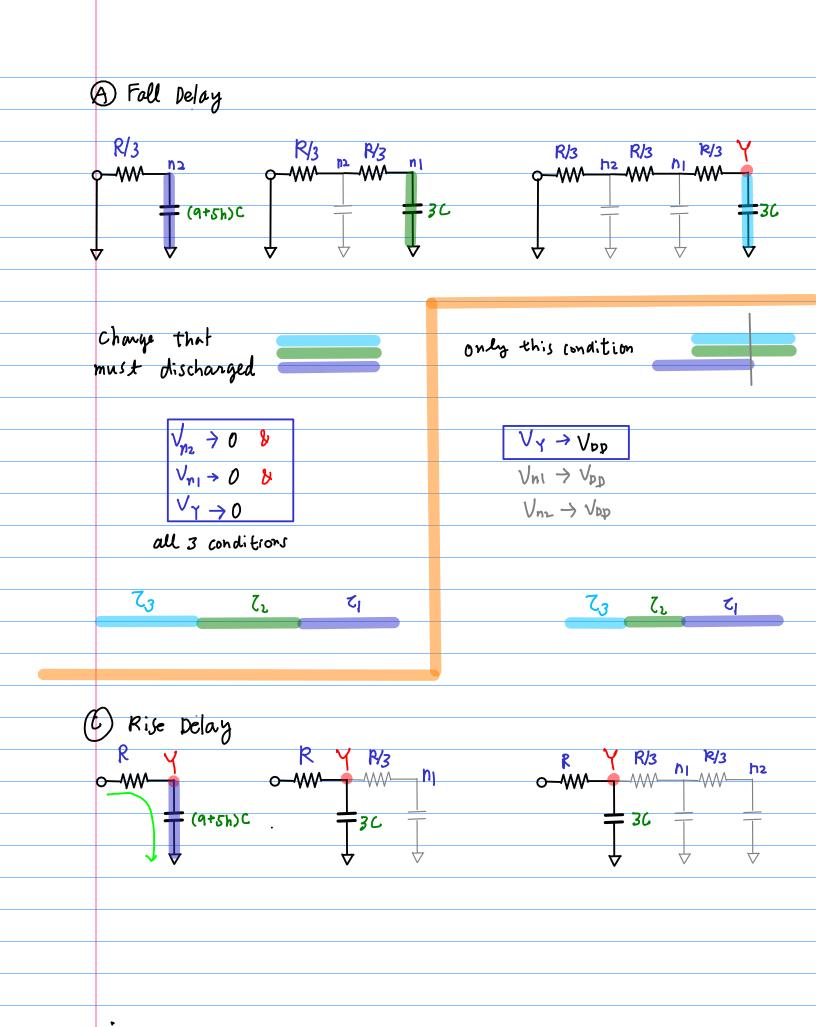

Fall Case - Elmore Delay  $\frac{1}{4} (9+5h)C$  $\frac{1}{\sqrt{2}} (9+5h)C \\ \frac{1}{\sqrt{2}} \\ \frac{1}{\sqrt{2$ <u>↓</u> (9+5h)C  $\mathbb{R}_3 \ge$ 7  $\sqrt{\frac{1}{2}}$  3 c  $\sqrt{\frac{1}{3}}$  $R_{3} \ge \frac{1}{3c}$   $R_{3} \ge \frac{1}{3c}$ 3 C  $\frac{\sqrt{3}}{\sqrt{3}}$  $\downarrow$  3 c  $\aleph_3 \ge$ ₽/3 ₹ 30 R/3 R/3 P/3 n1 R/3 K/3 R/3 hz W hI W <u>na</u> <u></u>+3C + (9+5h)C **≑**30 12 n Zm 7. 24 discharge first n2, then n1, finally Y the discharging change must be added 7= (n1 + (n2 + 7)

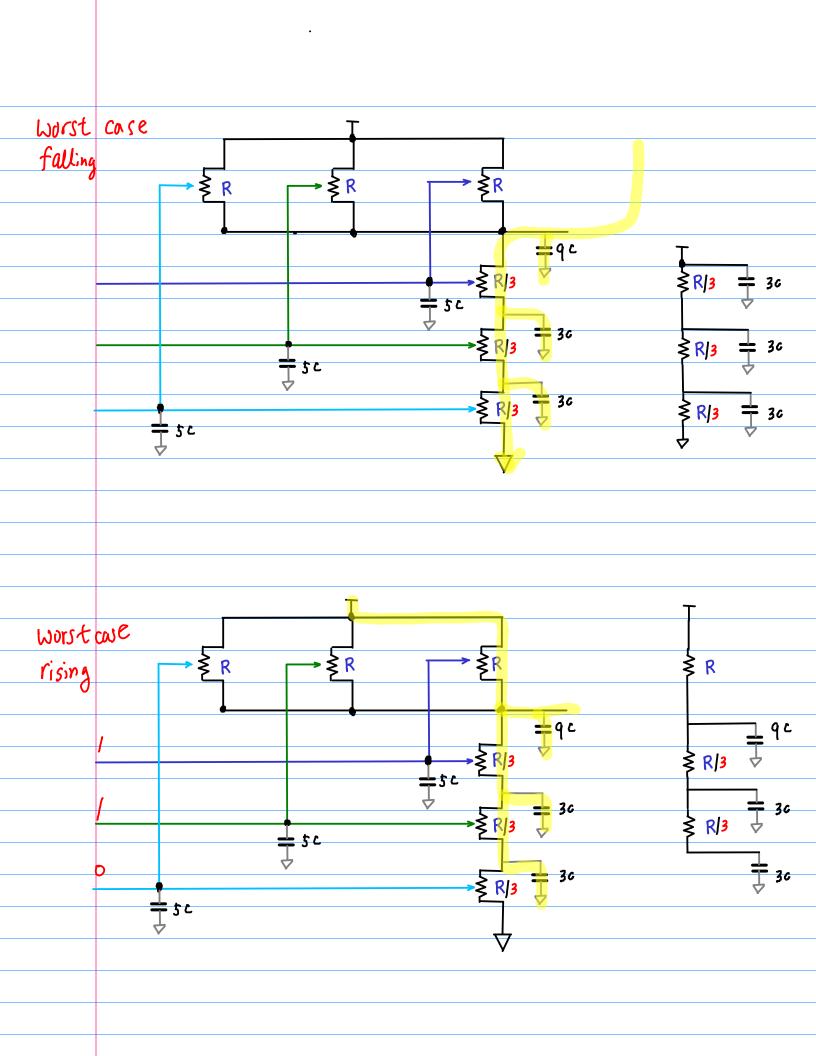

Input Transitions for a Minimum Delay Rise ₿ ABC = (A+B+C)=13 current sources Simultaneous falling to charge CL \_ Fall ABC=1One input rising lately Only have to discharge other inputs the parasitic capacitance already "H" of one nmos transistor Smallest resistance. this lately rising input is feed to the n Mos that is close to Y