#### CMOS Delay-3 (H.3) Logical Effort Applications

20160919

Copyright (c) 2015 - 2016 Young W. Lim.

Permission is granted to copy, distribute and/or modify this document under the terms of the GNU Free Documentation License, Version 1.2 or any later version published by the Free Software Foundation; with no Invariant Sections, no Front-Cover Texts, and no Back-Cover Texts. A copy of the license is included in the section entitled "GNU Free Documentation License".

| Based on                                  |

|-------------------------------------------|

| <b>D</b> 43 C 4 C 11                      |

| Uyemura                                   |

| Introduction to VLSI Circuits and Systems |

|                                           |

|                                           |

| Weste                                     |

| CMOS VLSI Design                          |

|                                           |

|                                           |

|                                           |

|                                           |

|                                           |

|                                           |

|                                           |

|                                           |

|                                           |

|                                           |

|                                           |

|                                           |

|                                           |

|                                           |

|                                           |

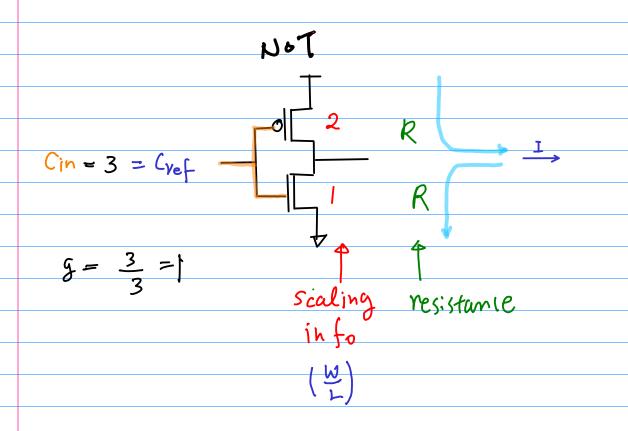

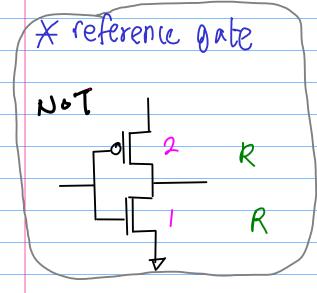

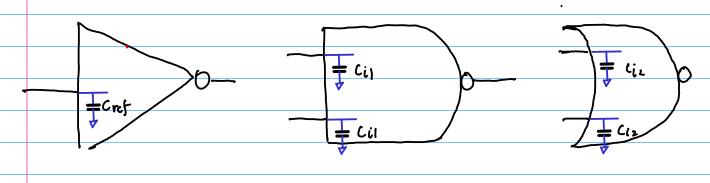

$$Cin = Cox (WnL + WpL)$$

$$= Cox (WnL + FWnL)$$

$$= Cox WnL (I+Y)$$

$$= Cqn(I+Y) = Cvef$$

$$Y = 2^{-3}$$

$$G = Cvef$$

$$Cvef$$

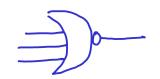

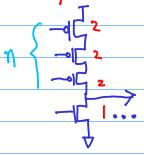

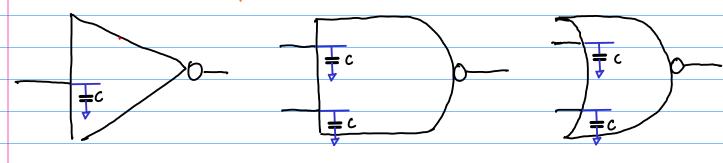

Comparing the performance of other gates

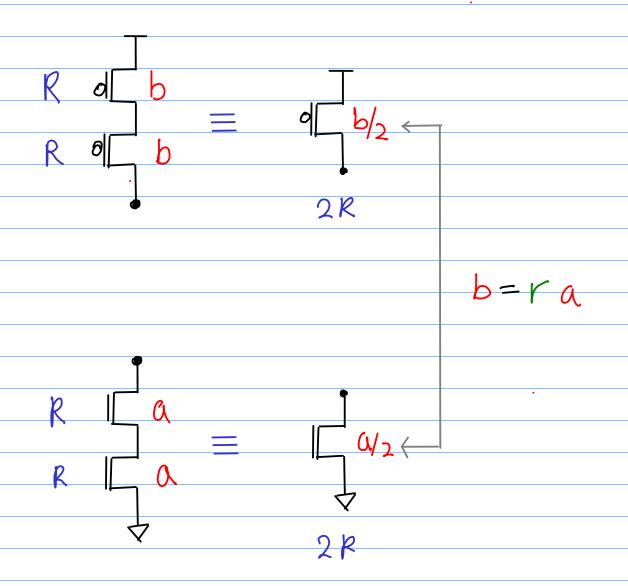

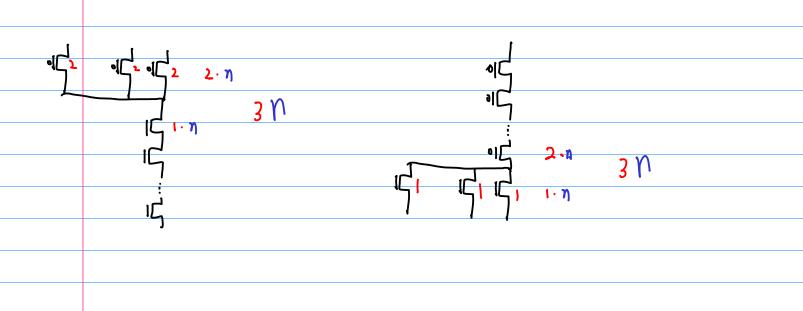

### Series Connection

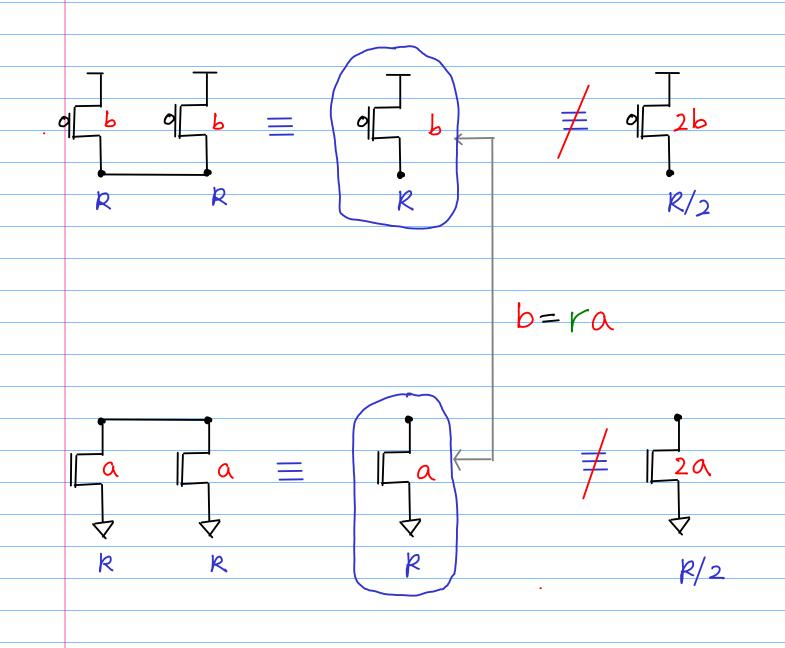

#### Parallel Connection

considering only one input at a time

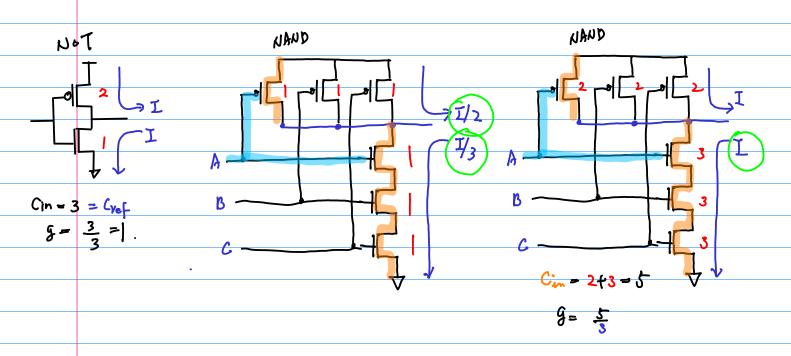

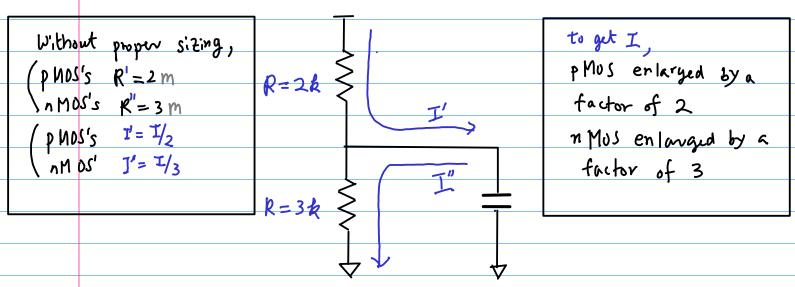

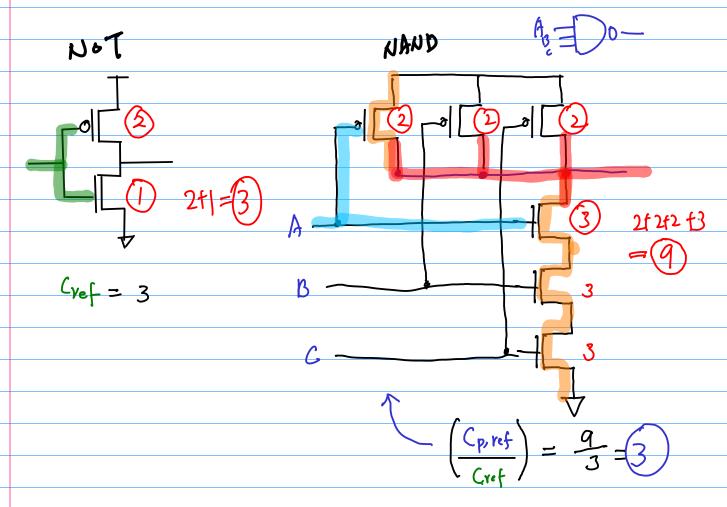

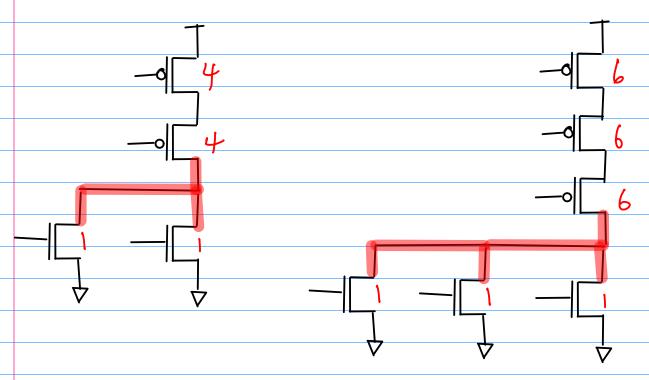

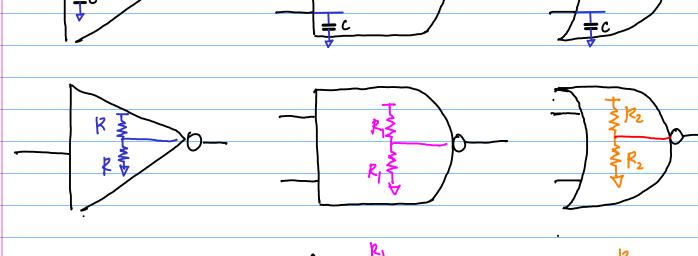

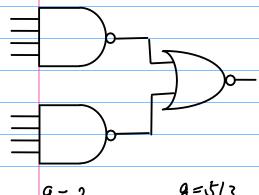

### NAND 1/2 = Do-

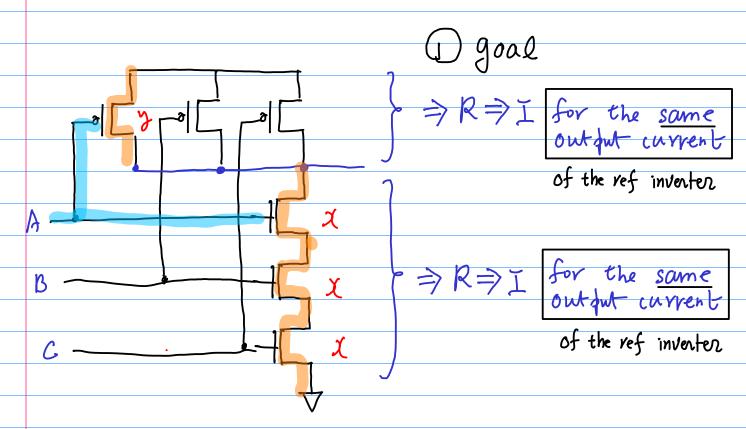

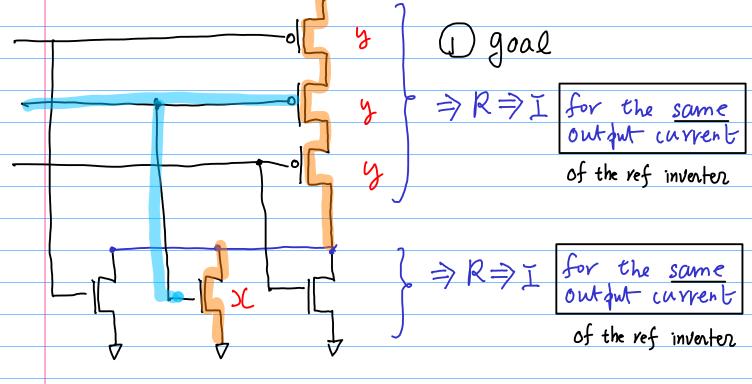

(1) Find Scaling info

R:

$$y = \frac{1}{2}$$

$y = 2$

R:  $x + x + \frac{1}{2} = \frac{1}{2}$   $y = 3$

$$9 = \frac{Cin}{Cref} = \frac{2+3}{2+1} = \frac{5}{3}$$

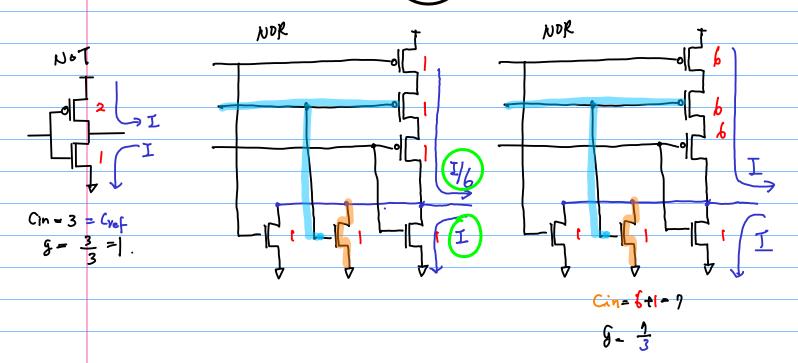

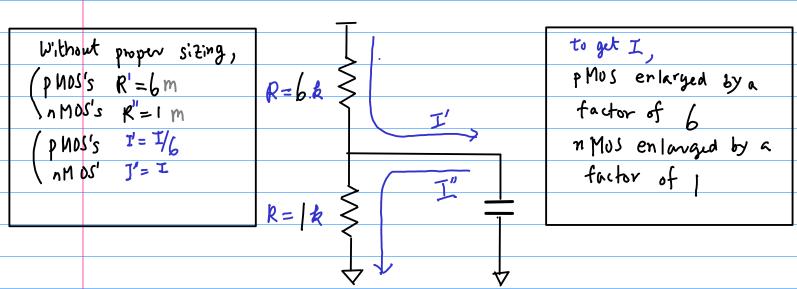

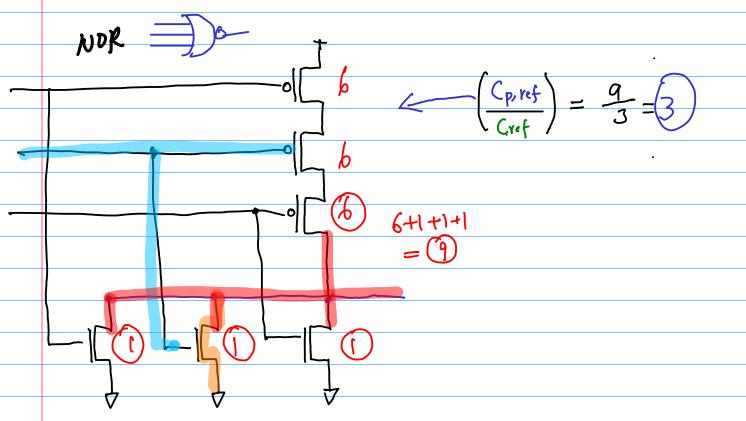

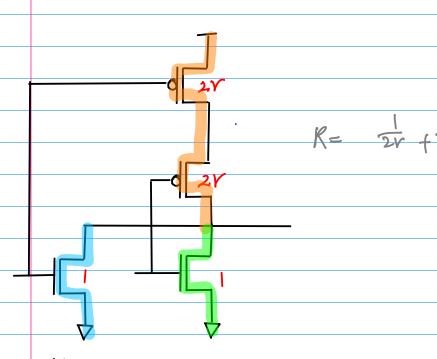

#### NOR

1) Find Scaling info

$$R: \frac{3}{y} = \frac{1}{2}$$

$y = 6$

$$R : \frac{1}{x} = \frac{1}{1}$$

$\chi = 1$

4

$$g = \frac{Cin}{Cref} = \frac{6+1}{2+1} = \frac{7}{3}$$

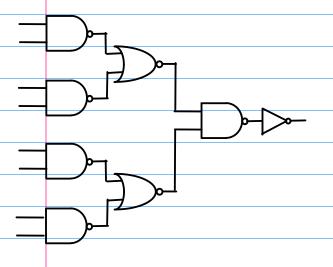

# Logical Effort (3): Topological Effect

$$t_f \propto RC$$

$t_r \propto RC$

$t_r \propto 2$

$$t_{Ng} = \frac{t_f + t_r}{2} \propto (3+2)$$

$$t_f + t_r \propto (3+2)$$

$$g = \frac{\text{Cin}}{\text{Cref}} = \frac{\text{tavg of NAND}}{\text{tavg of NOT}}$$

# Logical Effort (3): Topological Effect

$$t_{\text{avg}} = \frac{f_f + t_r}{2} \propto (1 + b)$$

$$t_f + t_r \propto (1 + b)$$

$$g = \frac{\text{Cin}}{\text{Cref}} = \frac{\text{tavg of NOR}}{\text{tavg of NOT}}$$

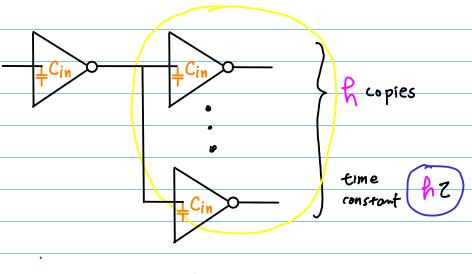

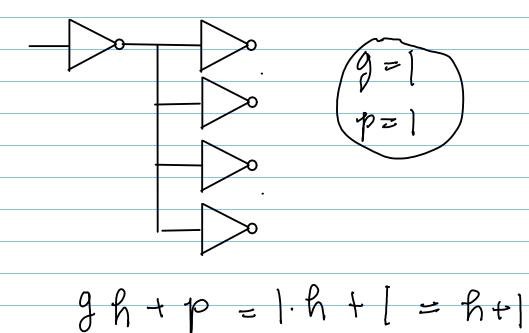

## Electrical Effort (h) : Fan Out Load

Electrical Effort: the output & input cap ratio

$$h = \frac{Cout}{Cin}$$

the ratio of the drive strength to drive Cout to the drive strength to drive its own capacitance Cin

Cout is h times larger than Cin

A copies of the same gate

h.Cin

### Parasitic Delay p

- \_ delay due to internal parasitic capacitance

- SCP

- excluding external load cap Cout

- count only diffusion capacitance of the output

- delay without output load

P =

$$\left(\frac{C_{p,ref}}{C_{ref}}\right) = \left(\frac{\text{internal diffusion cap}}{\text{gate cap of refinv}}\right) = \frac{7 \text{ par}}{7 \text{ ref}}$$

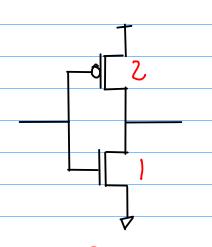

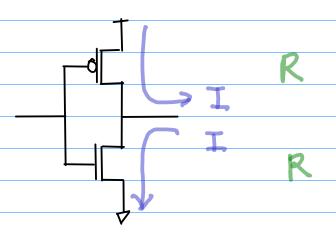

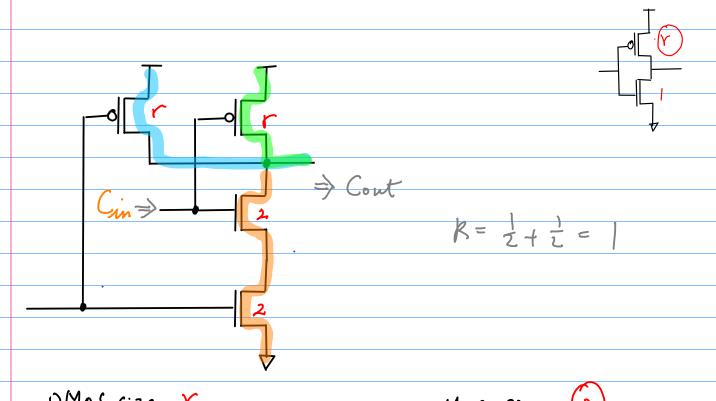

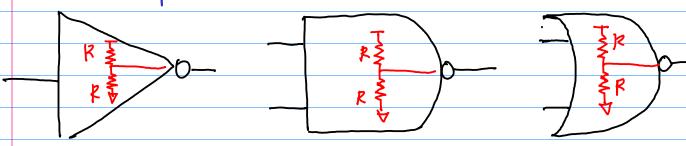

2,1): scaling into in order for PUN & PDN to have the same R, I

Tref = R. Cim = Pref. Cref = R.3C = 3RC

Tiny = Rref. Cp, ref = R.3C=3RC

Cpref > Count Scaling factors

Connected to

the output

$$C_{p,ref} = 2 + 1 = 3$$

$$P = \left(\frac{C_{p,ref}}{C_{ref}}\right) = \left(\frac{\text{internal diffusion cap}}{\text{gate cap of ref inv}}\right) = \frac{7 \text{ par}}{7 \text{ ref}}$$

P =

$$\frac{7 \text{ par}}{7 \text{ ref}} = \frac{\text{Rref} \cdot \text{Cp, ref}}{\text{Rref} \cdot \text{Cref}}$$

Cin of the reference inventor

(Symmetric inventor)

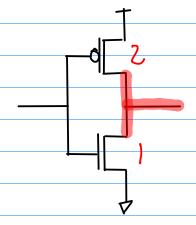

$$(2)$$

+  $(2)$  +  $(2)$  = 6

$$(4) + (1) + (1) = 6$$

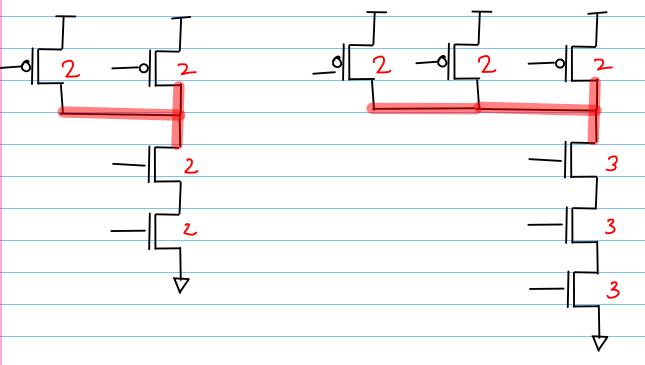

$$p_{\text{NAND2}} = \frac{6}{3} = 2$$

$$P_{\text{Slor}_2} = \frac{b}{3} = 2$$

$$P = \frac{1}{3} \left( \sum_{\text{Output Scaling factors}} \right)$$

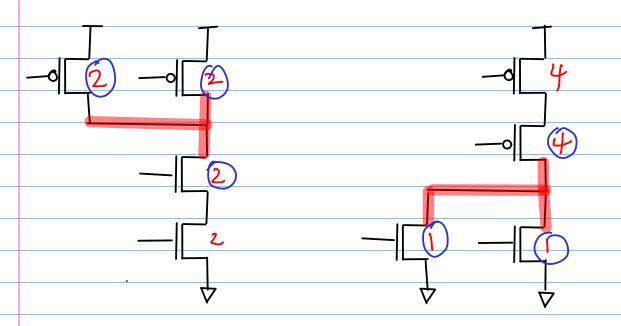

### Parasitic Delay

#### NAND3

$$\frac{23}{3} = 2$$

$$\frac{3.1}{3} = 3$$

3+(2+2+2) = 3(1+2)

#### NOKZ

#### NOK3

$$4+1+1=2\cdot\lambda+2\cdot1=6$$

$$|4+1+|=2\cdot2+2\cdot1=6$$

6+6+2 + 1+1+1 = 3·2+3·] = 3(2+1)=9

$$\frac{1}{3}=2$$

$$\frac{9}{s}=3$$

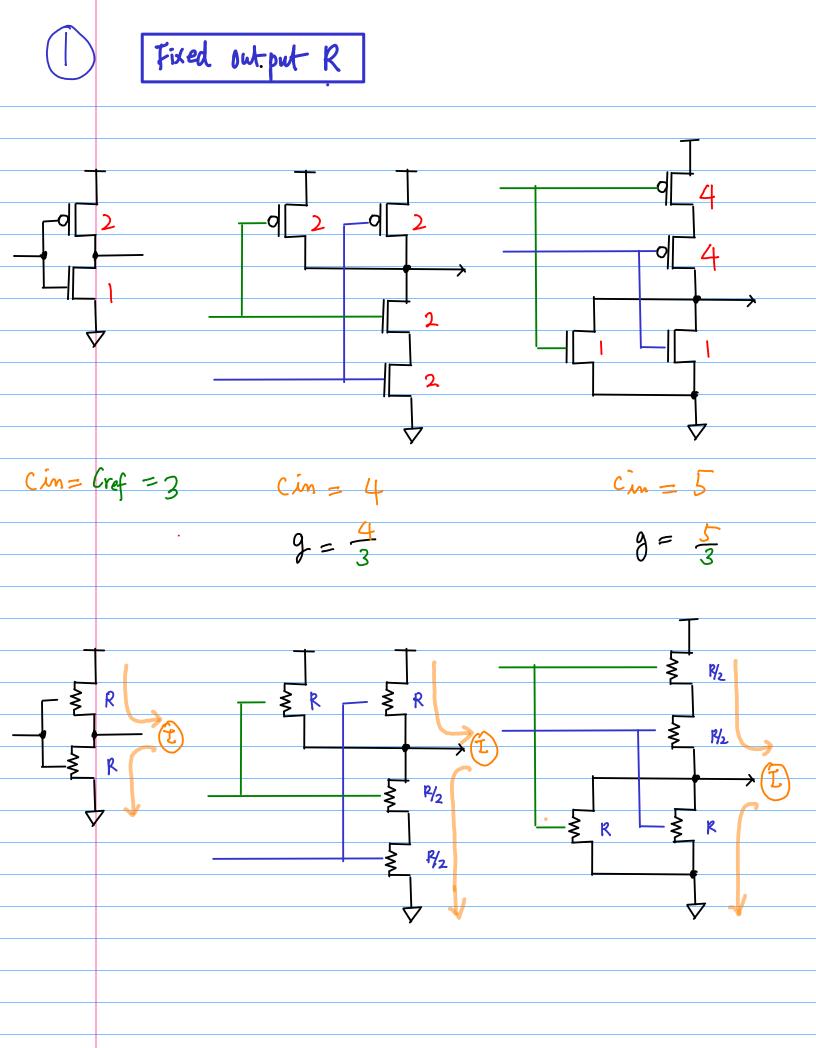

# Symmetric NAND2 (G)

$$g = \frac{Cin}{Cref} = \frac{Cgn(2+r)}{Cgn(1+r)} = \frac{2+r}{1+r}$$

### Symmetric NOR2

PMos size 2r

the worst case path from Vap to Vout

must be twice as the inverter

(Series Connection)

nMos size

< the worst case path from GND to Vout must be the same as as the inventor

$$G = \frac{Cin}{Cref} = \frac{Cgn(1+2r)}{Cgn(1+r)} = \frac{1+2r}{1+r}$$

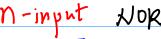

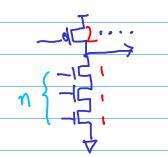

# M-input NAND, NOR

$$g = \frac{2+r}{1+r}$$

$$g = \frac{1+2\gamma}{1+\gamma}$$

$$(1\cdot n + 2)$$

# Logical Effort &

$$\frac{C_1}{3} = \frac{(2+2)}{(1+2)} \qquad \frac{5}{3} = \frac{(3+2)}{(4+2)} \qquad \frac{6}{3} = \frac{(4+2)}{(4+2)}$$

$$\frac{C_1}{3} = \frac{(2+2)}{(1+2)} \qquad \frac{5}{3} = \frac{(3+2)}{(4+2)} \qquad \frac{6}{3} = \frac{(4+2)}{(1+2)} \qquad \frac{(n+2)}{(1+2)}$$

$$\frac{5}{3} = \frac{(1+2i)}{(1+2i)} \qquad \frac{7}{3} = \frac{(1+2i)}{(1+2i)} \qquad \frac{9}{3} = \frac{(1+2i)}{(1+2i)}$$

$$g = \frac{(M+r)}{(I+r)}$$

$$\theta = \frac{(1+r)}{(1+r)}$$

# Parasitic delay P

$$\frac{6}{3} = \frac{2(1+2)}{(1+2)}$$

$$\frac{6}{3} = \frac{3(1+2)}{(1+2)}$$

$$\frac{12}{3} = \frac{4(1+2)}{(1+2)}$$

$$\frac{12}{3} = \frac{4(1+2)}{(1+2)}$$

$$\frac{12}{3} = \frac{4(1+2)}{(1+2)}$$

$$\frac{12}{3} = \frac{4(1+2)}{(1+2)}$$

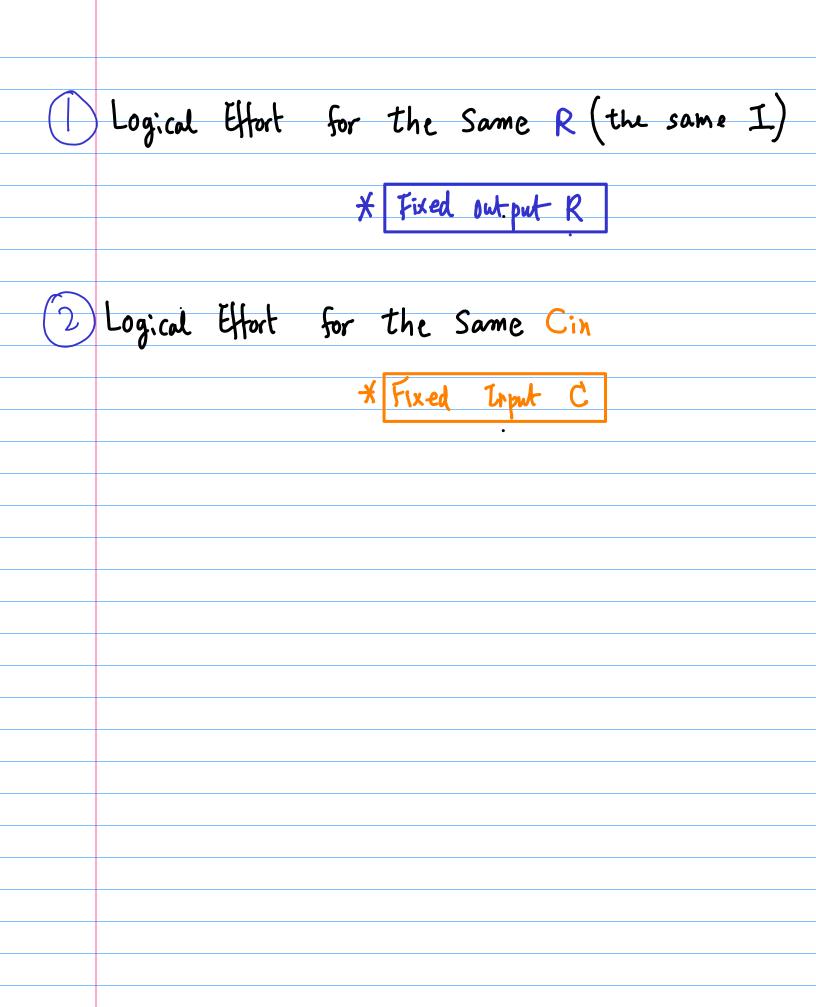

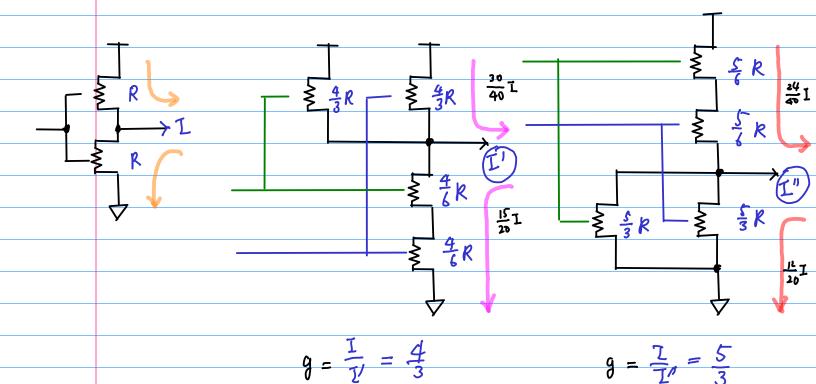

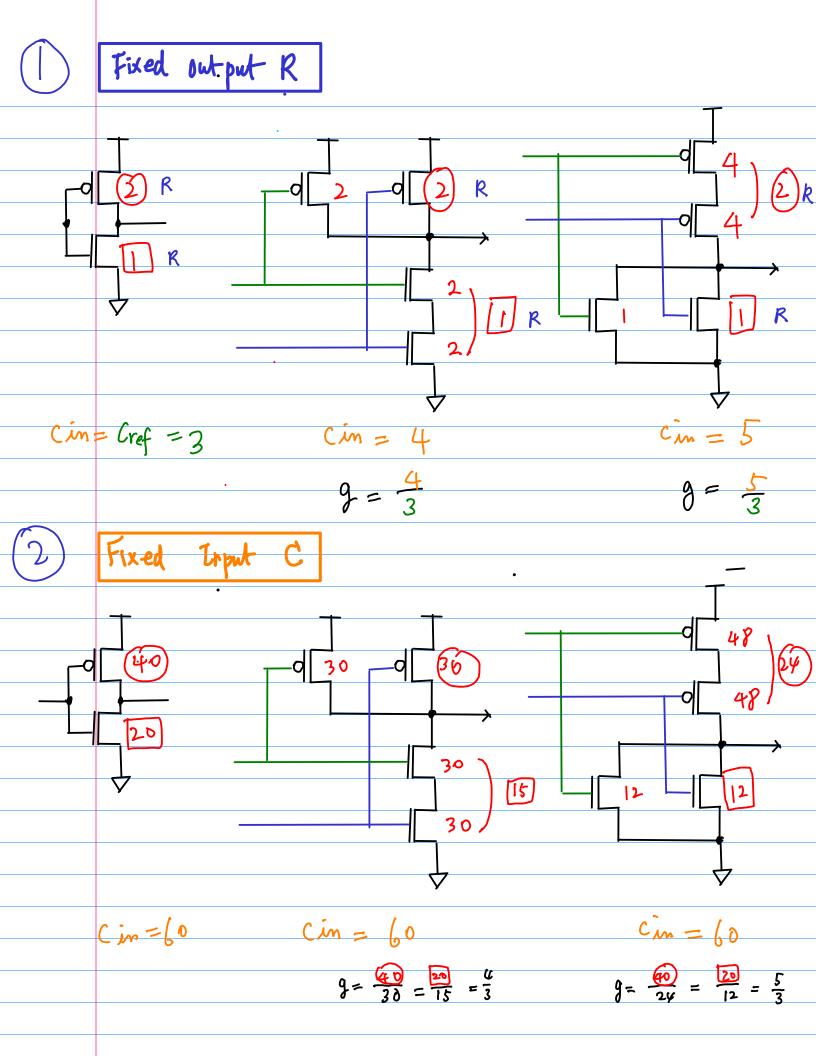

#### \* Fixed output R -> must increase size -> Cint

$$g = \frac{Ci1}{Cref}$$

$g = \frac{Ci2}{Cref}$

\* Fixed Trput Cap -> Complexity of logic gate increase R\$

$$g = \frac{k_1}{k}$$

$g = \frac{k_2}{k}$

the same output I as that of o

more complex to pology than -Do-

for the same I

the size must be increased.

ratio

$$g = \frac{Cin}{Cref}$$

#### \* Fixed Input C

**→**>0**-**

more complex

to pology than -Do-

the out put current be comes smaller

the output R becomes greater

ratio

$$g = \frac{R}{Rref}$$

Symmetric =>

fall time = Vise time

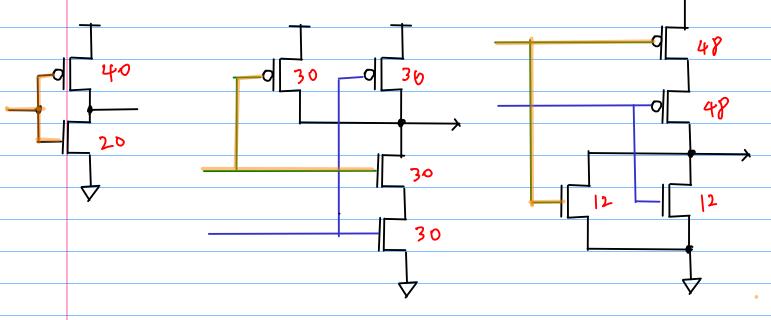

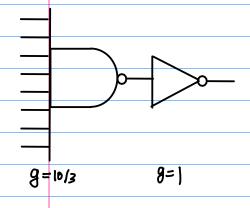

### F04

$$\frac{8+2}{1+2} = \frac{10}{3} \qquad \frac{1+2}{1+2} = 1$$

$$G = \frac{10}{3}$$

$$\frac{4+2}{1+2} = \frac{1}{3} = 2$$

$\frac{1+2\cdot 2}{1+2} = \frac{5}{3}$

$$G = \frac{10}{3}$$

$$\frac{2+2}{1+2} = \frac{4}{3} \qquad \frac{1+2\cdot 2}{1+2} = \frac{5}{3}$$

$$G = \frac{4}{3} \times \frac{5}{3} \times \frac{4}{3} = \frac{80}{21}$$