## CMOS Delay-1 (H.1) Transistor Sizing

20160905

Copyright (c) 2015 Young W. Lim.

Permission is granted to copy, distribute and/or modify this document under the terms of the GNU Free Documentation License, Version 1.2 or any later version published by the Free Software Foundation; with no Invariant Sections, no Front-Cover Texts, and no Back-Cover Texts. A copy of the license is included in the section entitled "GNU Free Documentation License".

## Based on

Uyemura Introduction to VLSI Circuits and Systems

Weste CMOS VLSI Design

Logical Effort Techniqus shows how many stages of logic are required for the fastest implementation of any given logic function Scaling of logic cascades Characterize logic gates & their interaction to provide techniques to minimize the delay (high speed chains)

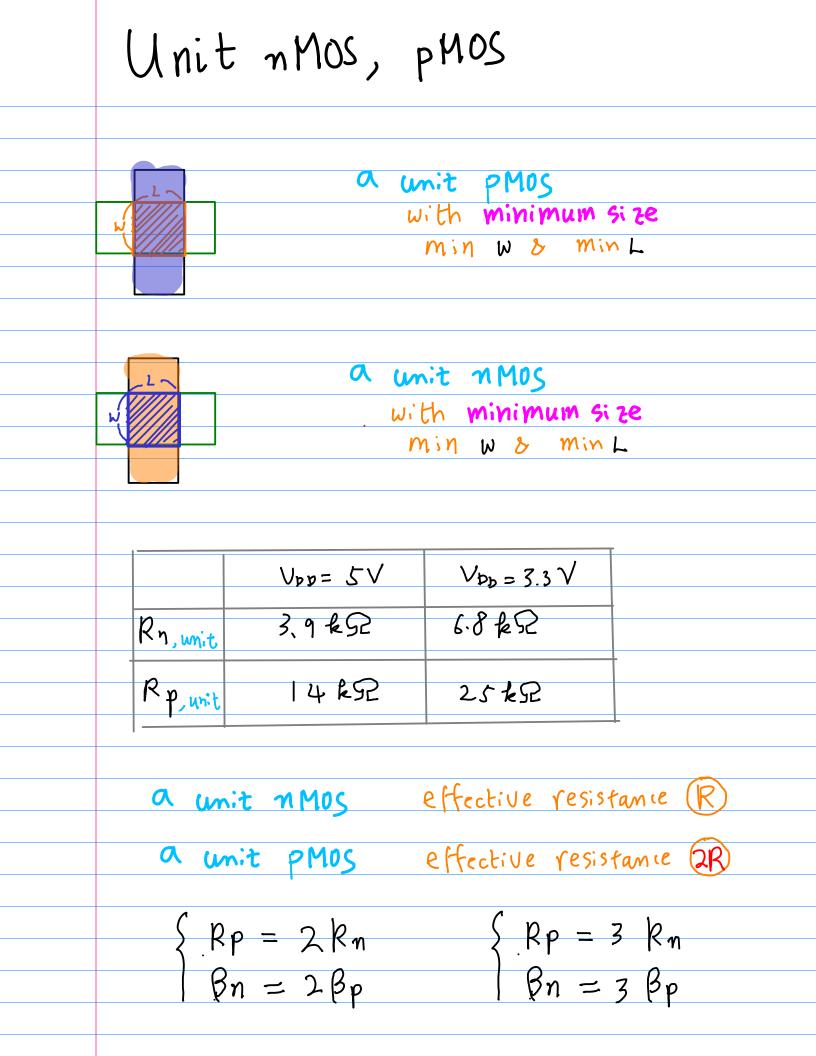

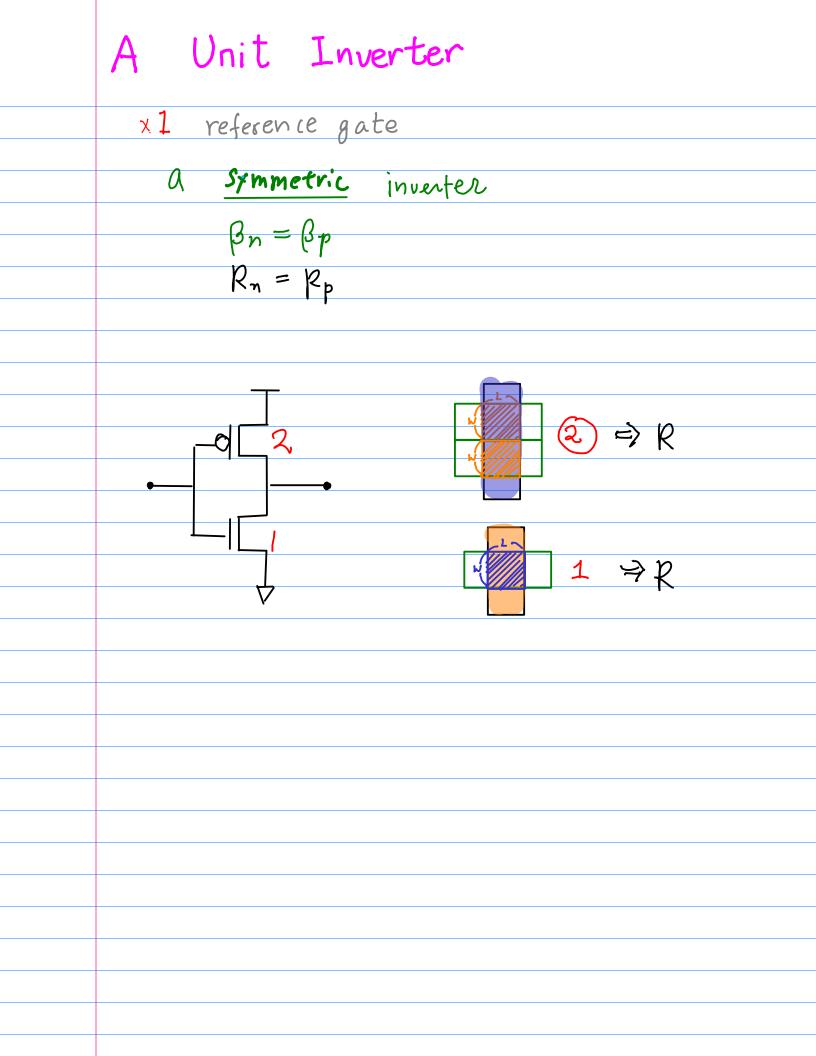

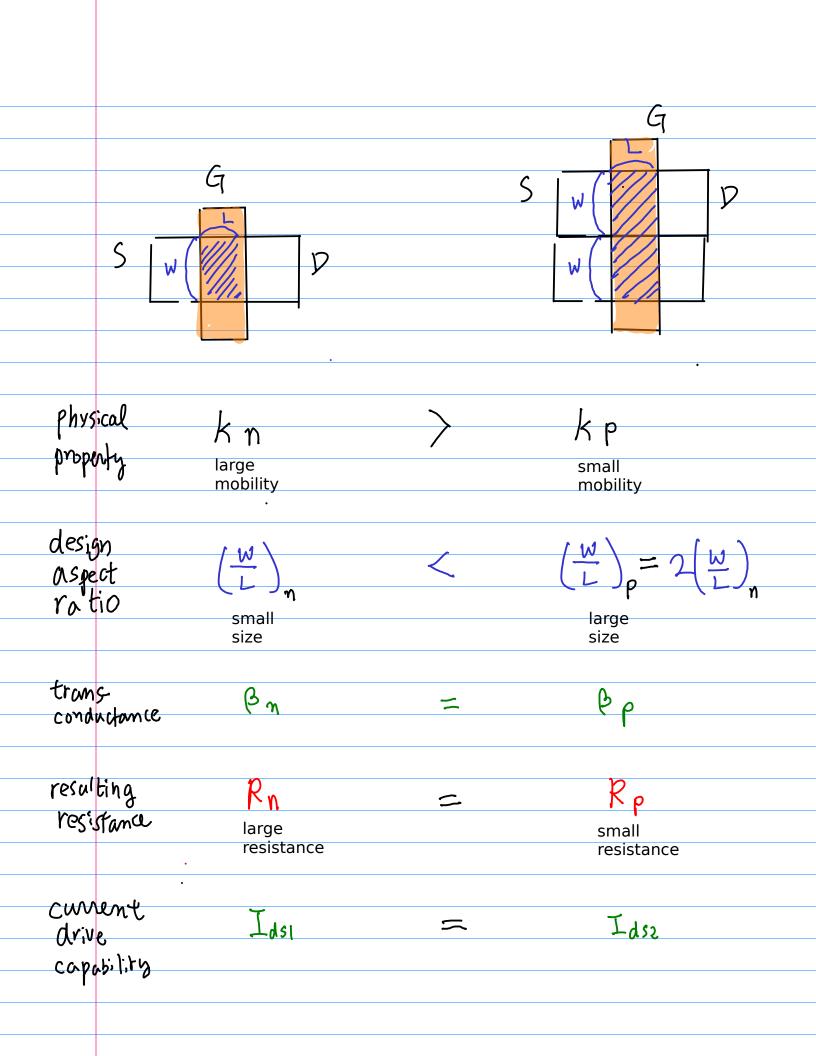

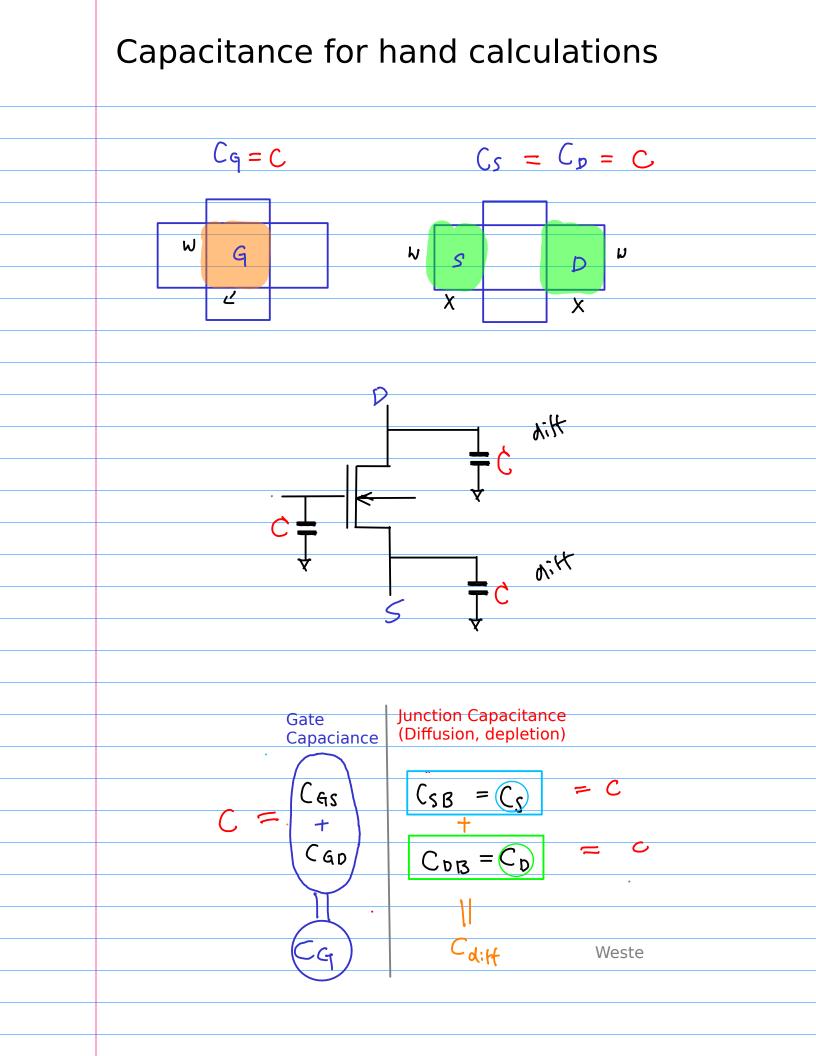

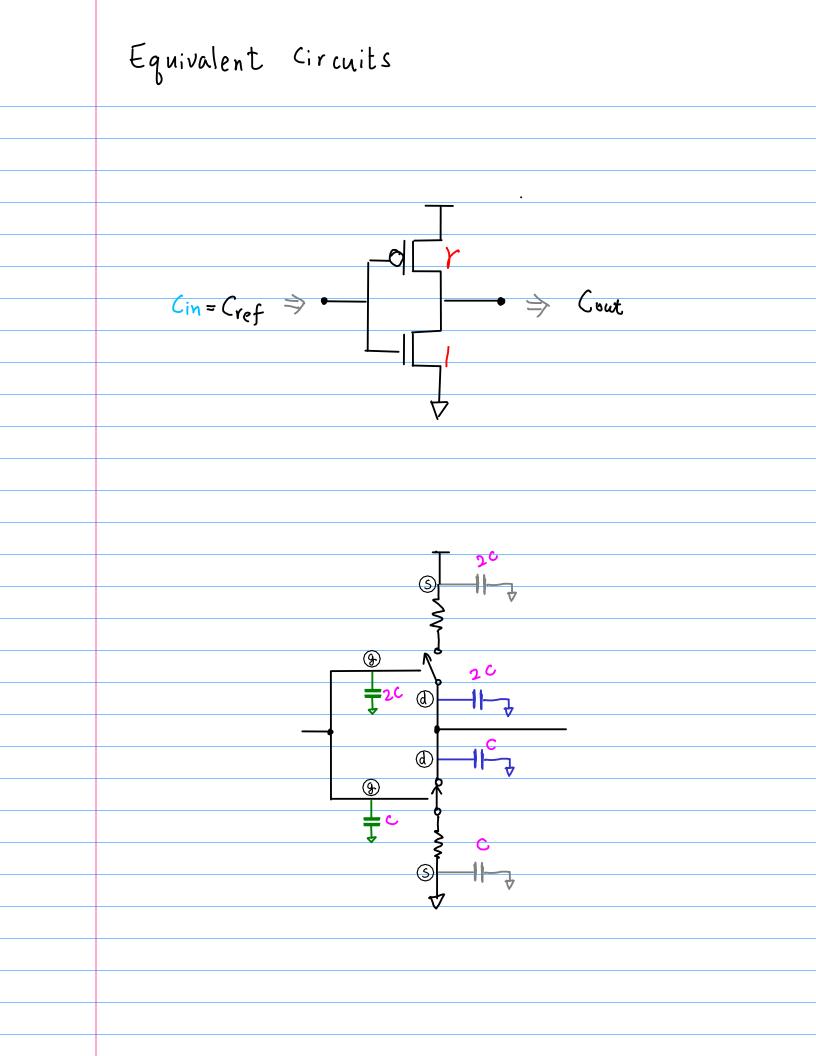

reference gate which gate? ->0+ =) )> an inverter What kind of inventers? a symmetric inverter Rp d  $R_n = R_p$ Rn  $\beta_n = \beta_p$

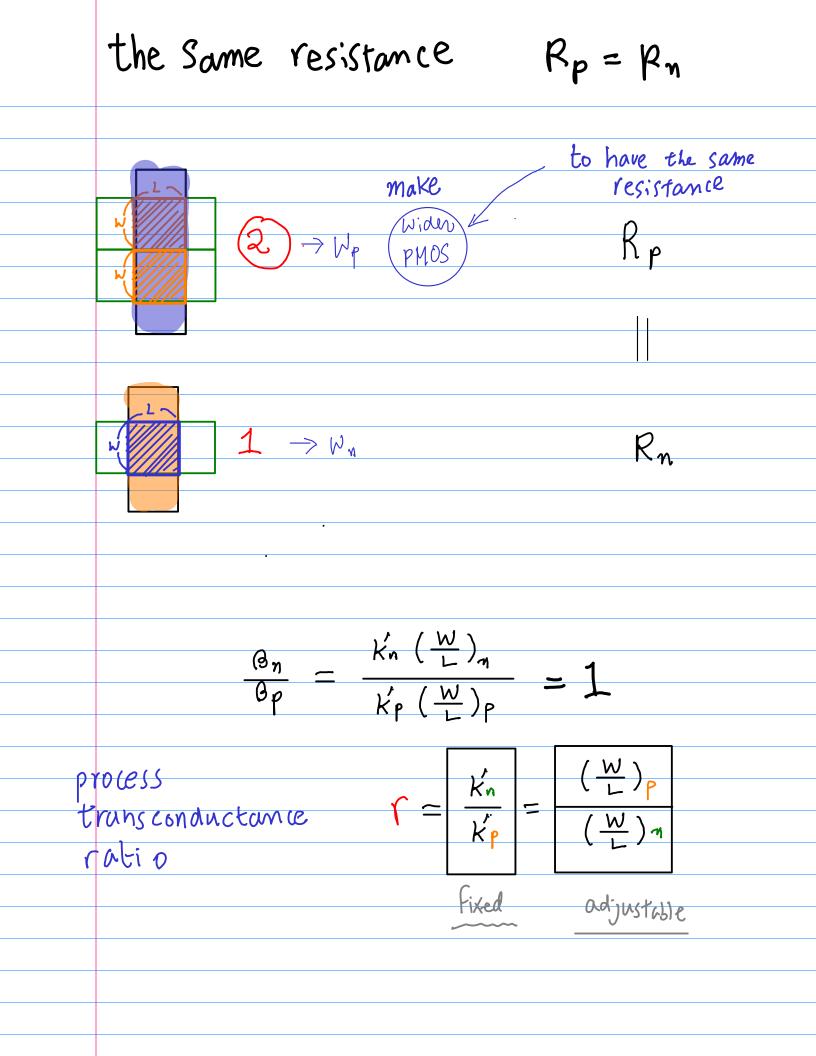

Transconductance

$$\frac{\Theta_n}{\Theta_p} = \frac{k'_n \left(\frac{W}{L}\right)_n}{k'_p \left(\frac{W}{L}\right)_p}$$

$$\Theta \propto \frac{1}{k} \quad \Theta \propto \left(\frac{W}{L}\right) \quad \beta \propto k.$$

$$\frac{k'_n}{k'_p} = 2 \times 3 \quad \text{difforent mobility}$$

$$Physical property$$

$$A unit nMOS \quad \frac{\left(\frac{W}{L}\right)_n}{\left(\frac{W}{L}\right)_p} = 1$$

$$\frac{\Theta_n}{\Theta_p} = \frac{k'_n}{k'_p} = \gamma = 2 \times 3$$

as pect ratio for the same (R) a symmetric inverter Bn = Bp Rn = Rpa relative aspectiratio d  $(\beta_p) = (\beta_n) \quad r = 2 \sim 3$  $\left(\frac{\omega}{L}\right)_{p} = r \left(\frac{\omega}{L}\right)_{m}$  $Kn = r K_p$ for a fixed (h),  $W_{p} = \bigvee_{n} W_{n}$ consider a scale factor

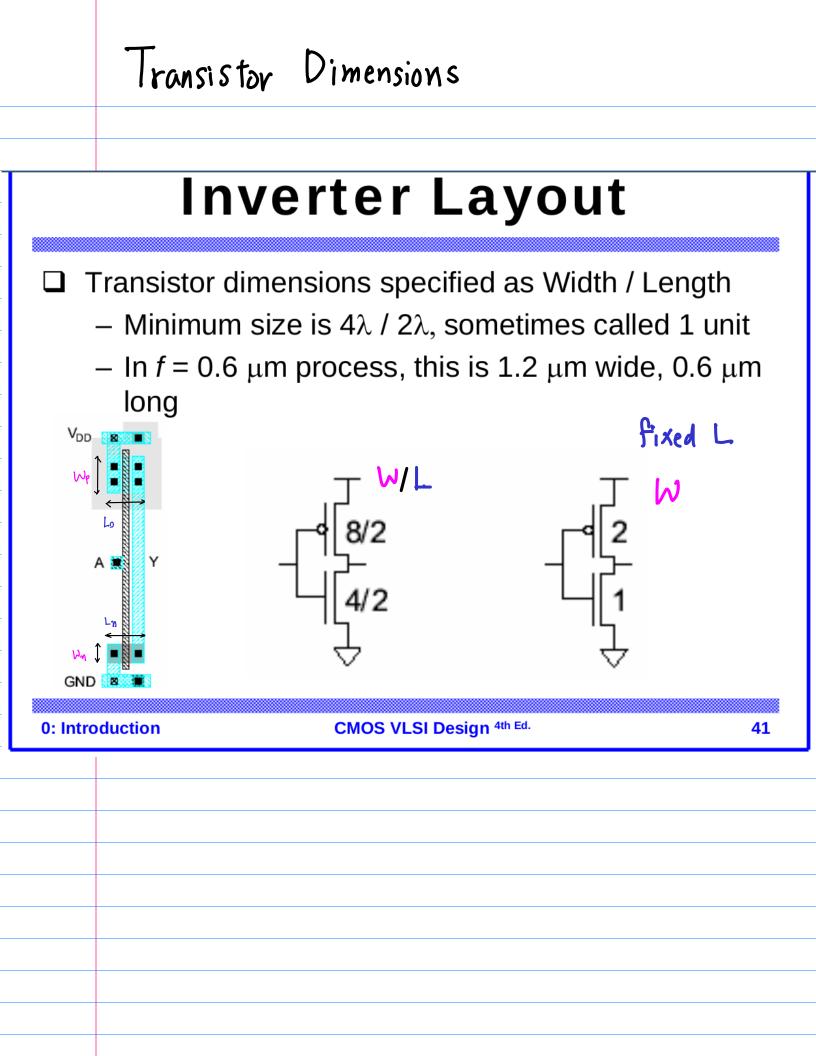

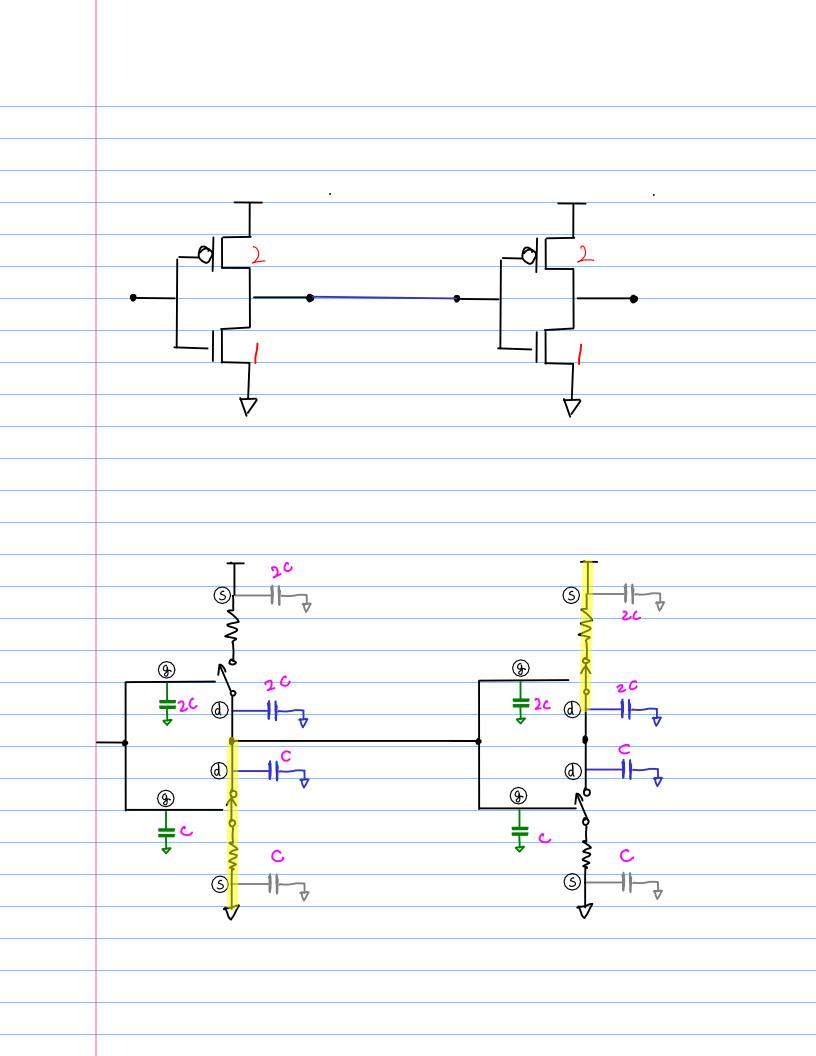

Sizing, Scaling d <u>4</u>7 4 x ref IX ref the smallest sizing in the logic chain  $\left(\frac{\omega}{L}\right)_{p} = r \left(\frac{\omega}{L}\right)_{m}$  $\left(4\frac{W}{L}\right)_{p} = r \cdot \left(4 \cdot \frac{W}{L}\right)_{m}$ for the same L,  $\left(\frac{4W}{L}\right) = \mathcal{V} \cdot \left(\frac{4W}{L}\right)_{m}$ 4 4 Large Drive Strength

Fall Delay & Rise Delay  $V_{in}$ 1.0 -0.5 0.0 t<sub>pdr</sub> t<sub>pdf</sub> out 1.0 0.9 (0.8 tf  $= 2.27_{n}$ 0.5 0- 0.2  $T_r = 2.27_p$ tr output rise time output fall time out 2 delay = k·R·C

Transistor Sizing

determination of the appropriate  $\left(\frac{W}{2}\right)$ 's. for transistors for performance on other design goals

## Transistor sizing algorithm

- individually tune the widths of all transistors

- in a circuit to meet delay requirement

- or make efficient use of layout area -> power efficient

- every transistor with different size -> difficult to layout

- approximation in Standard cells

- -> selecting different sized transistors

transistor sizing is used in circuits that inherently requires long wires. Vanying the sizes of transistors at strategic points → improve delay full custom layout: anbitrary transistor sizing Standard cell: limited transistor sizing Several versions of differently-sized transistors

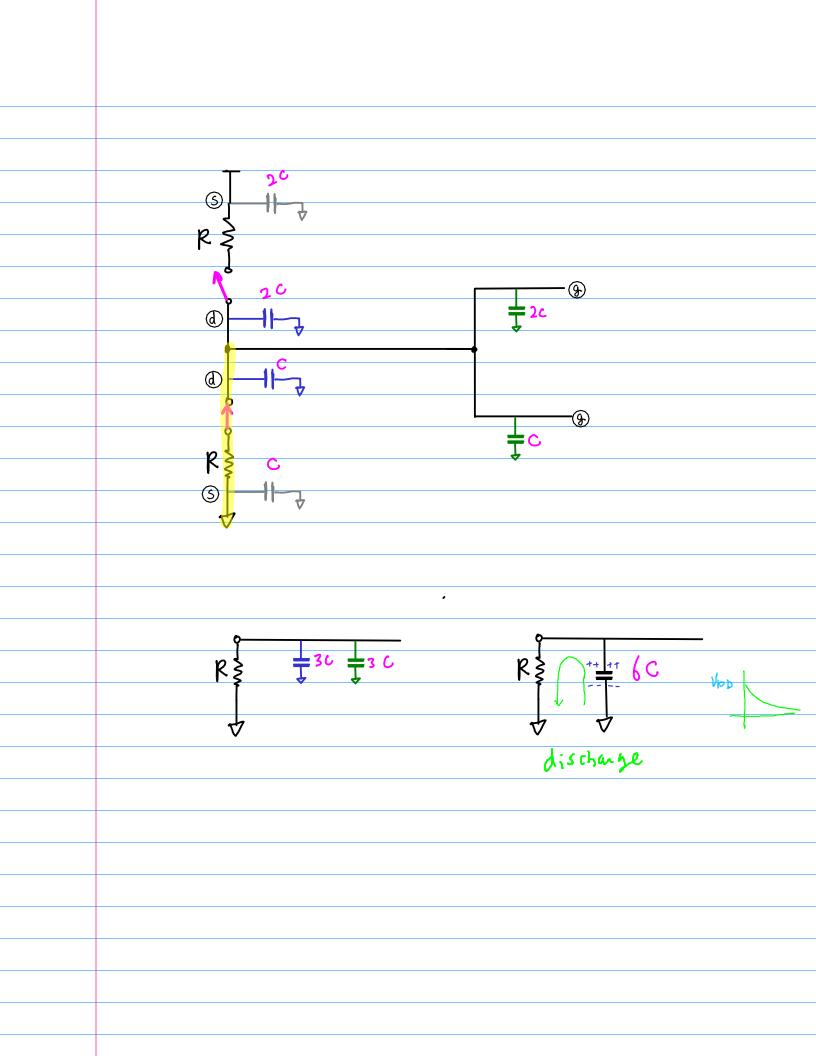

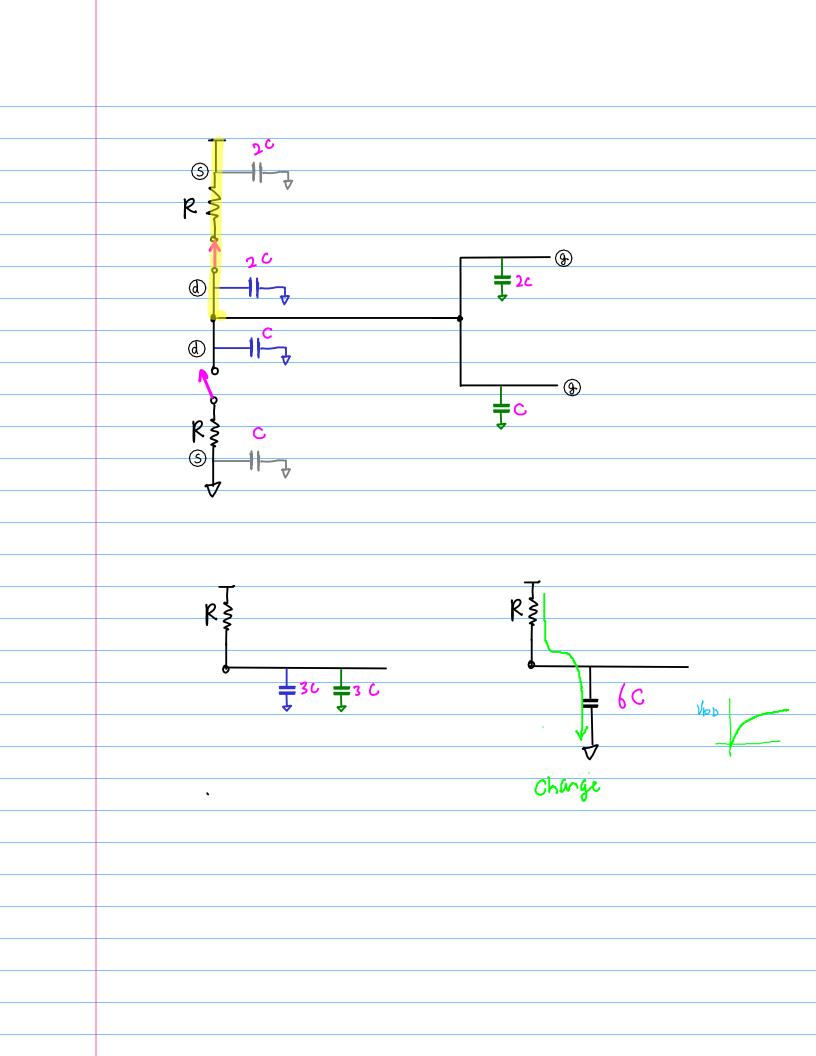

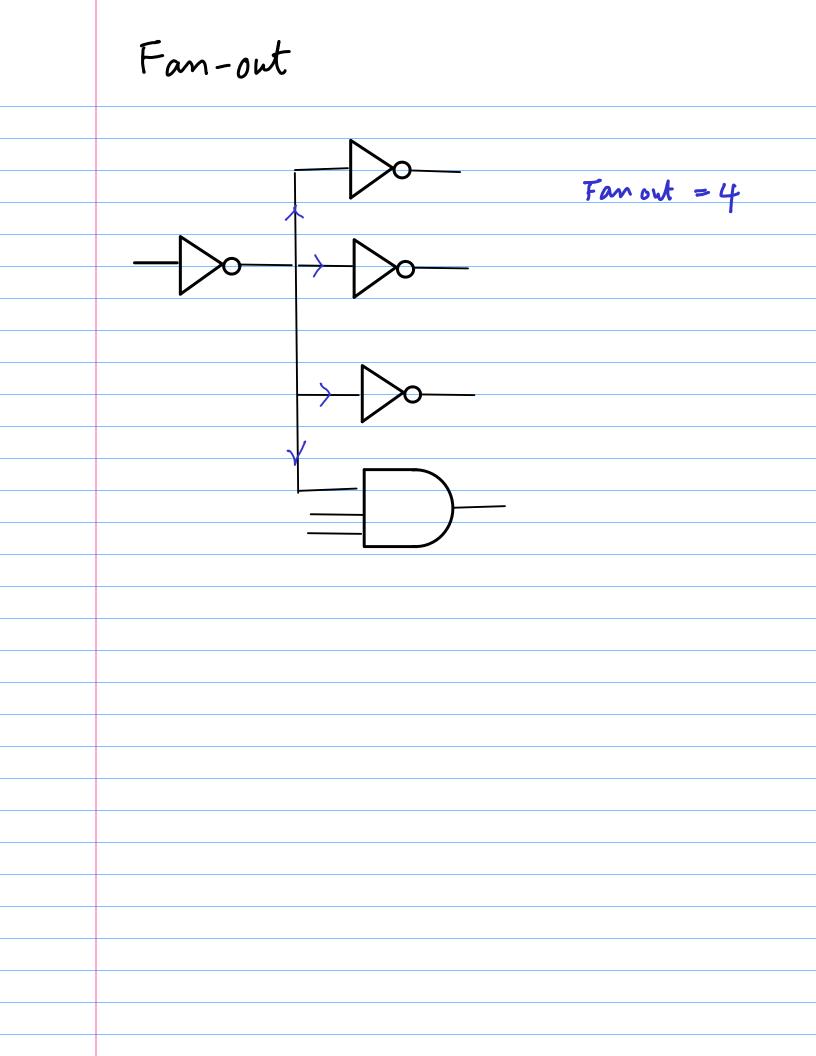

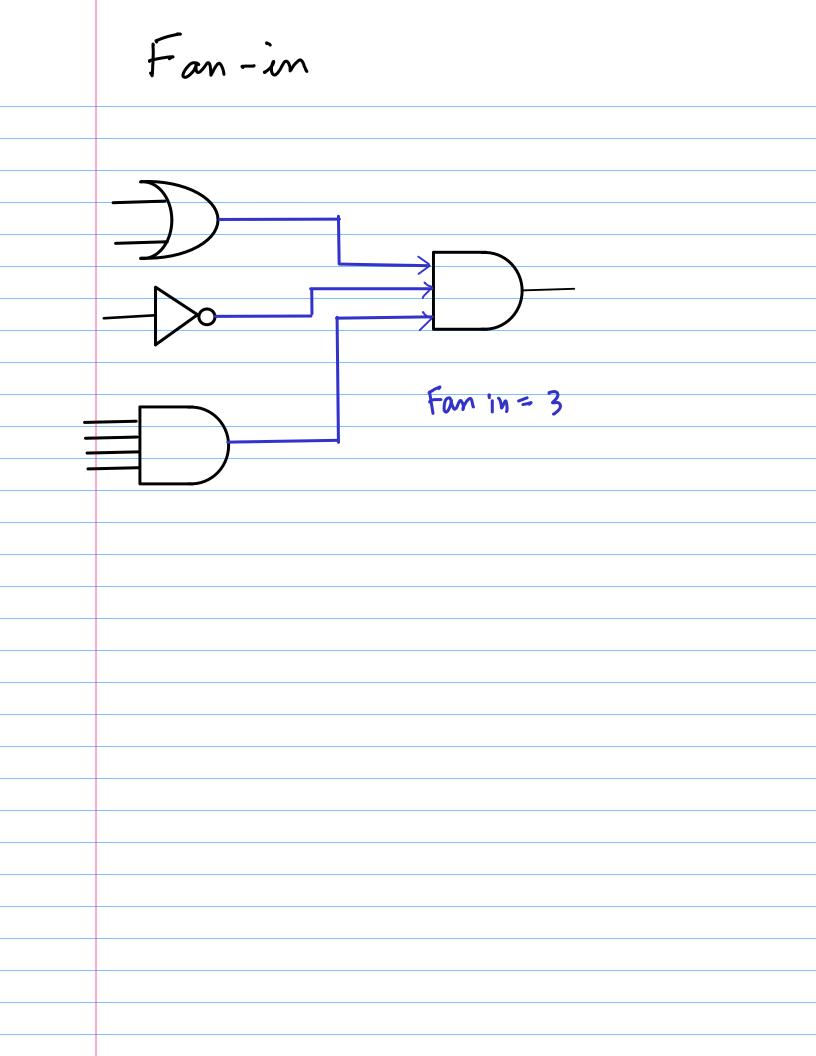

driving large load - off chip load - long signal wire - Clock, reset wire (lange famout) large fan out -> large capacitance to increase current by large transistor also increase the gate capacitance - problem back one level of logic T CL Solution: exponentially topering

D use a minimum sized device throughout Then optimize paths

from a critical path timing analysis