# DRAM (H.1) 2006.06.06 www.wikiversity.org The necessities in Computer Organization Copyright (c) 2015 Young W. Lim.

Permission is granted to copy, distribute and/or modify this document under the terms of the GNU Free Documentation License, Version 1.2 or any later version published by the Free Software Foundation; with no Invariant Sections, no Front-Cover Texts, and no Back-Cover Texts. A copy of the license is included in the section entitled "GNU Free Documentation License".

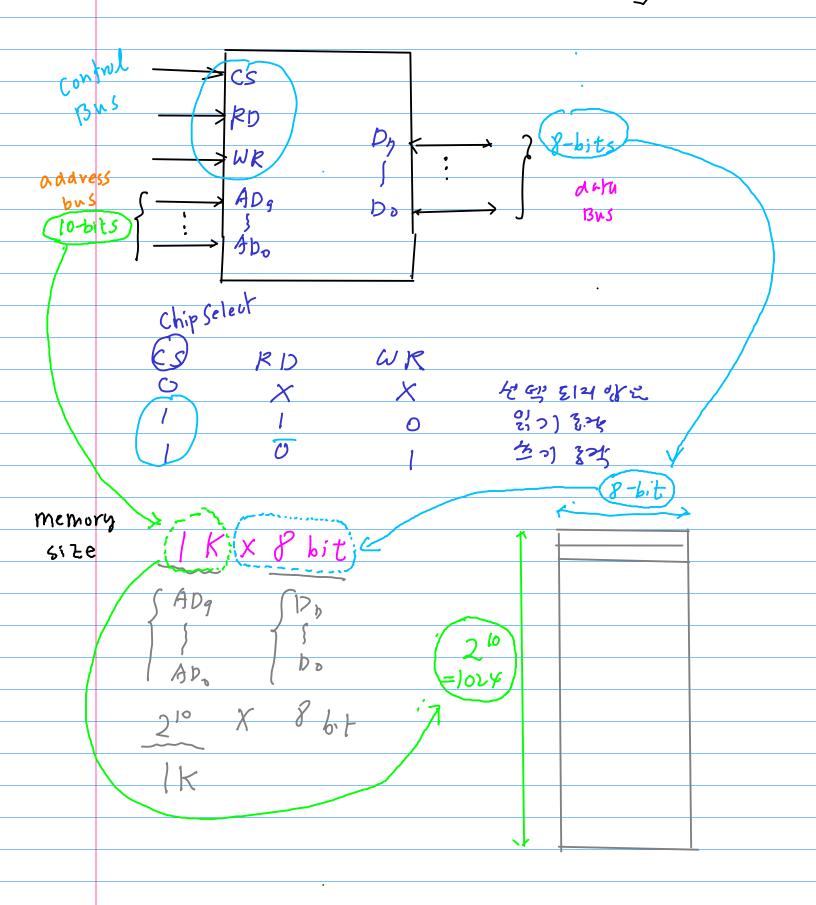

# RAM (Random Access Memory)

DRAM --- capacitor = 223/2+ 01 = 1 Dem () Pyramic Prefresh (3)34 2H= 24) SRAM -- Flip-flop

Static (refresh X) (ell) --- memoryona |-bite 21253>1312 71243 DRAM (clied SRAM cell OI) of thoy It Chores (なも 与し) transistorる 子弛かる) 45 82-11 Chip 22 30 21 21-21 34 Ct. Low roct integrate → that main memory 2 1+832t. SRAM - fast - Olyth - Cache Memory 3 458 EL

+ refresh 회 2 と Chipon 시 기고하는 면적이 DRAM의 용강이 거건 수록 장대적으로 즉 이 돈기 때는 이 가정에 엉덩이 없다

Cell E

Why refresh

हैगध् लिहिं। होनाम ध्रिक

1////

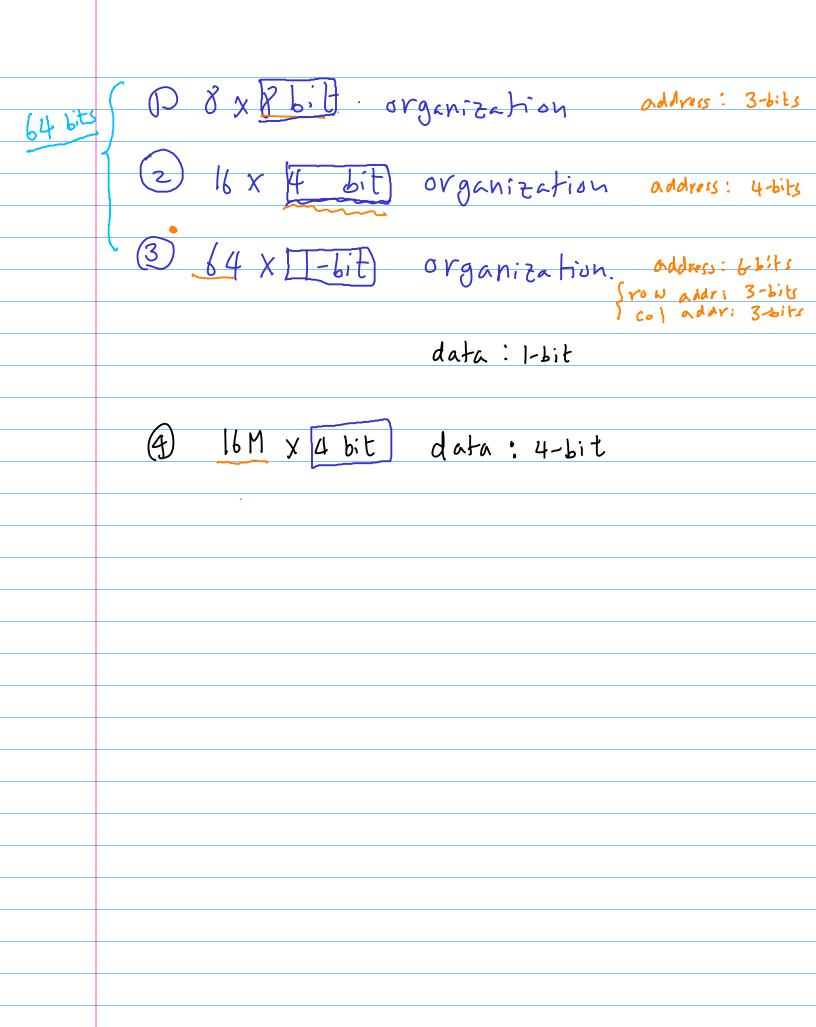

# 64-bit Memory Configuration

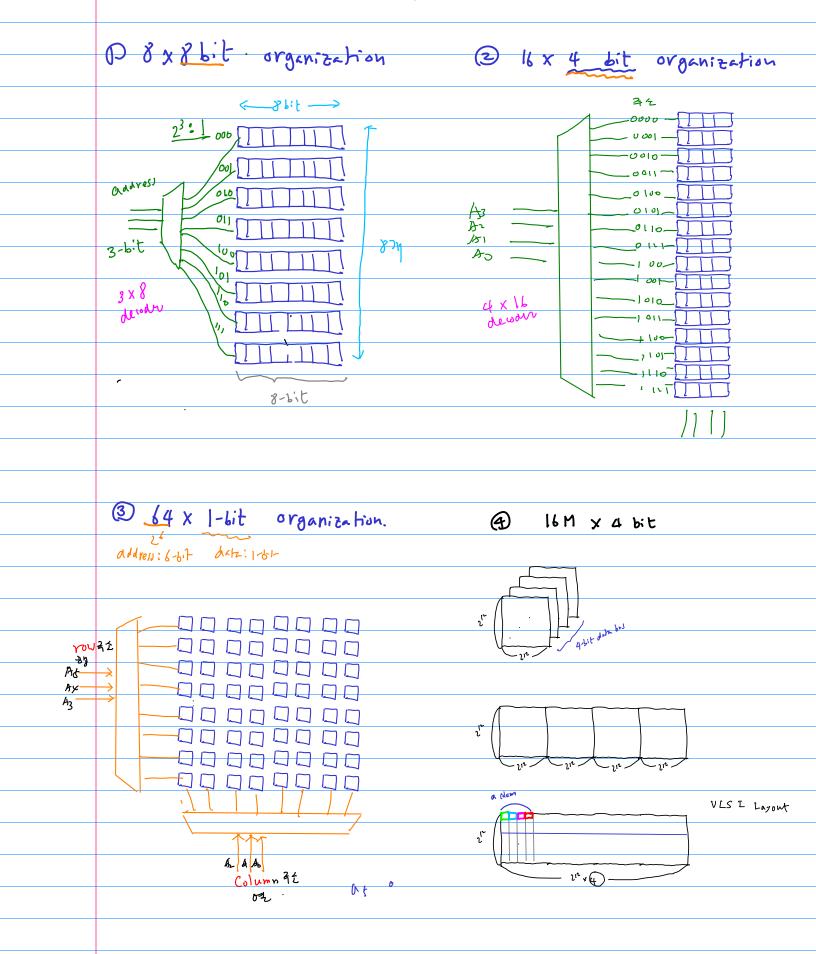

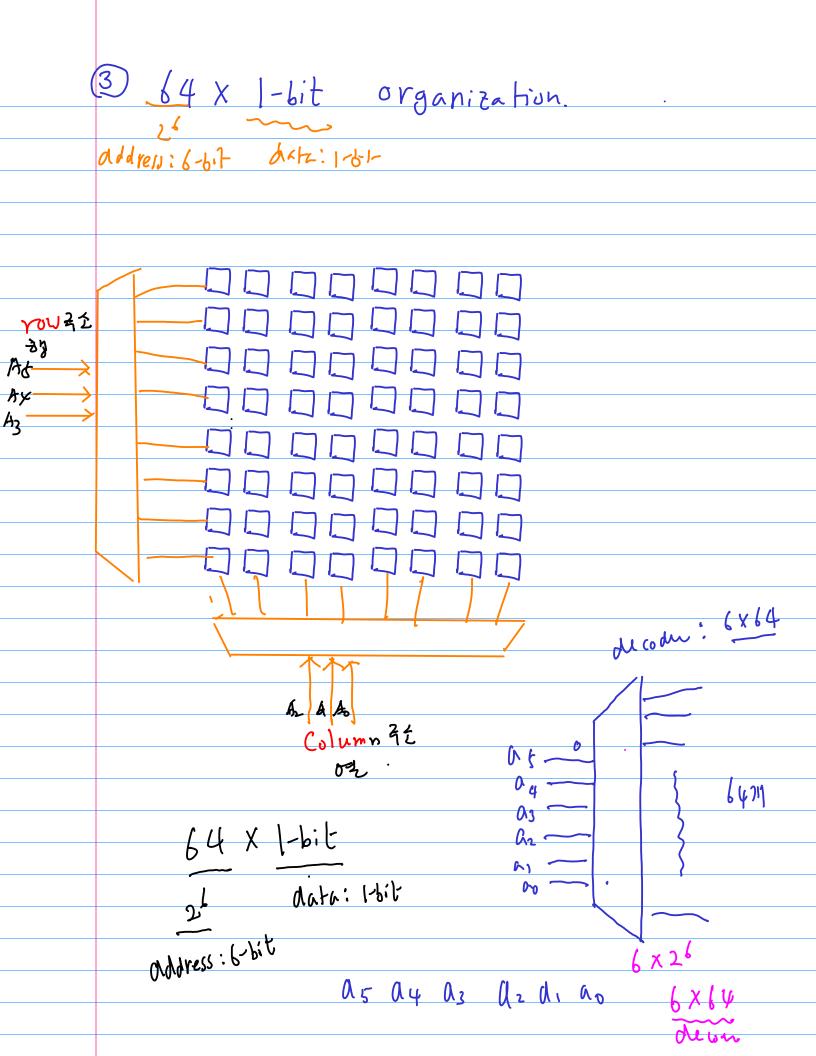

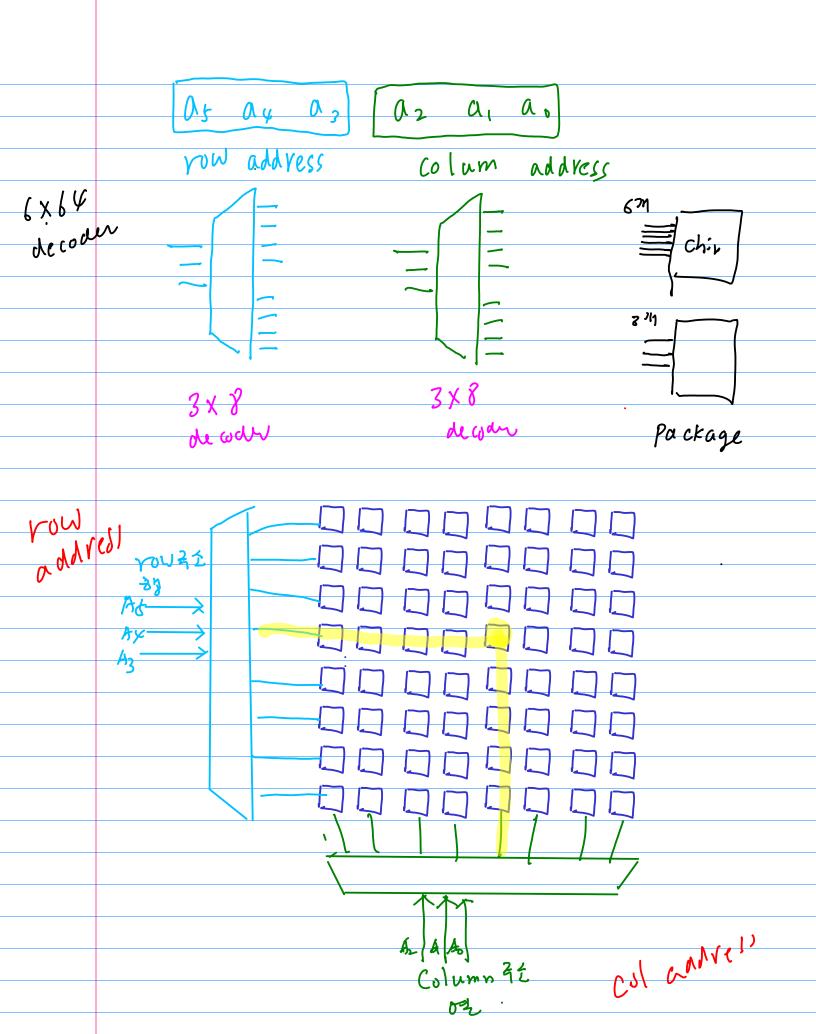

P&x&bit. organization

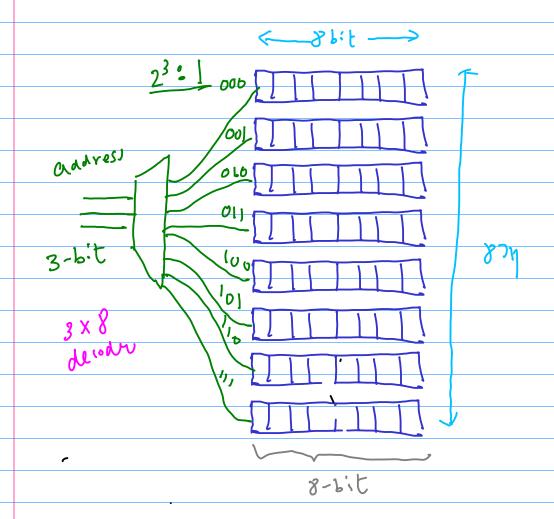

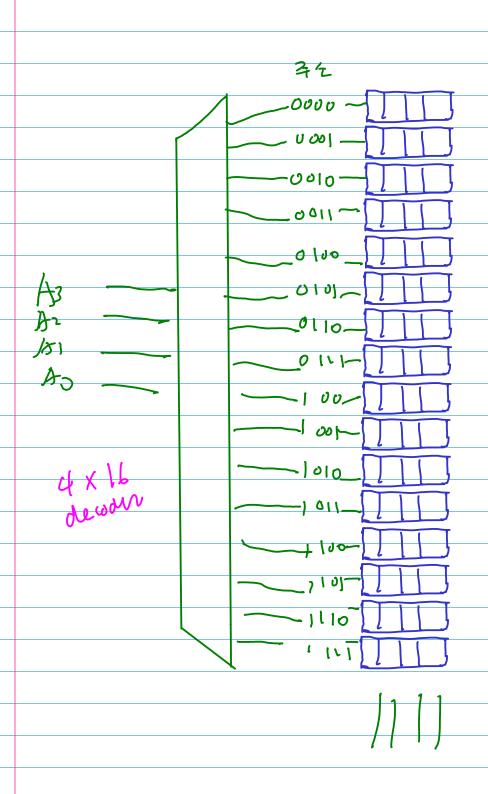

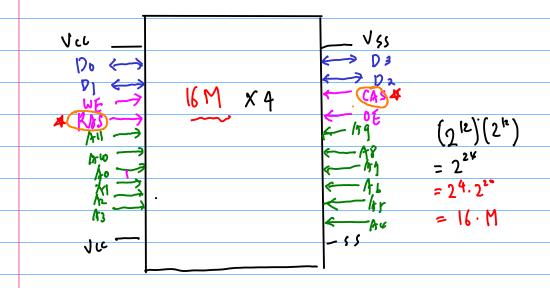

2 16 x 4 bit organization

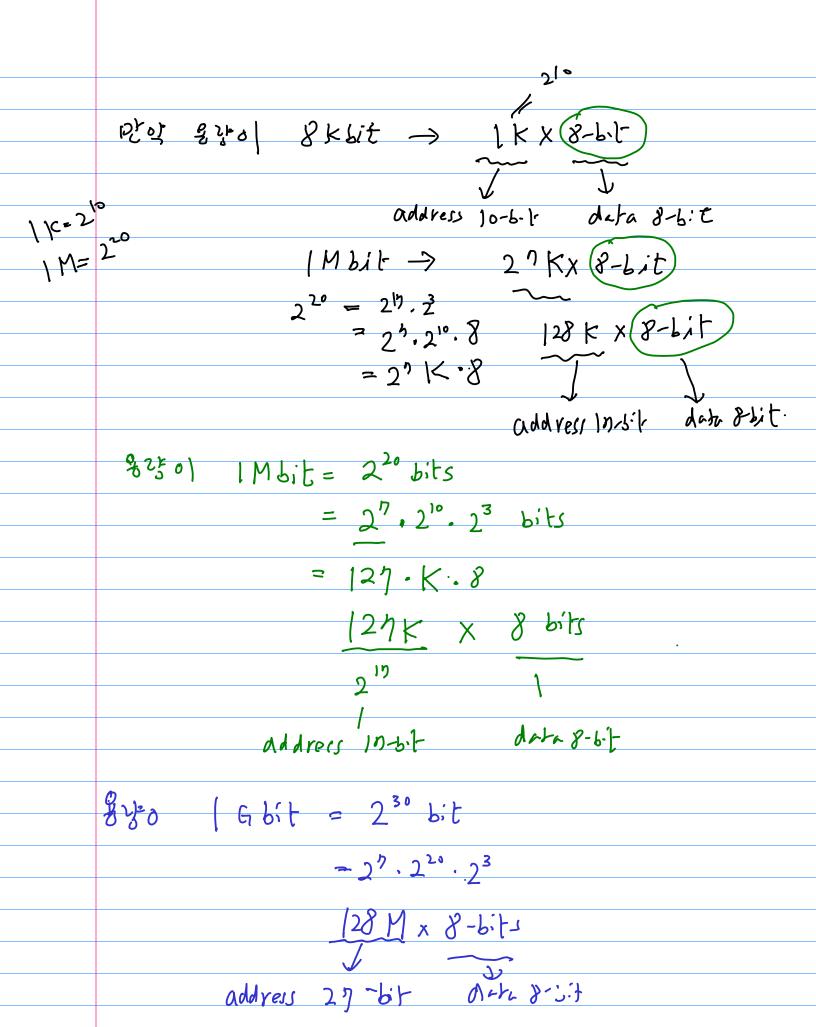

· 3 8210/ 8 K bit  $2^{3} \cdot 2^{10} - 2^{1} \cdot 2^{2}$ 2 K x 4 bit

address: 11-6: - data = 45: -3 6200 / Mbit 2 20 6 - 28.210.23 25/K × 4 1:1/2

add: 18

dela 46-fi 3 g z + 0) | G bit 2 · 2<sup>20</sup> · 2<sup>2</sup> 257 M X 4 bits address 28 dots white

|     | 3, 821-0 | 8 K bit | 8 K x 1-bit                    |

|-----|----------|---------|--------------------------------|

|     |          |         | 23 · 210                       |

|     |          |         |                                |

|     |          |         | 213                            |

|     |          |         | address: 13-bit acta=1-bit     |

|     |          |         |                                |

|     | 92° 0)   | ( Mbit  | 1 M × 1-6:1-                   |

|     |          |         | 220                            |

|     |          |         | address: 20 date: 15:t         |

|     |          |         |                                |

|     | 9 2 60   | Gbit    | G x 1-bit                      |

|     | · ·      |         | 30                             |

|     |          |         | address: 30-5:t Axte: 1-6-t    |

|     |          |         | Oggless . 39.2, f Myre 1 1.9.1 |

|     |          |         |                                |

|     |          |         |                                |

|     |          |         |                                |

|     |          |         |                                |

|     |          |         |                                |

|     |          |         |                                |

|     |          |         |                                |

|     |          |         |                                |

| i e |          |         |                                |

### a lom x 4 bit

$$\frac{2^{12} + 64 \text{ Mbit}}{2^{12} + 2^{10} + 41024 + 4196}$$

$$2^{12} = 2^{1} \cdot 2^{10} + 41024 + 4196$$

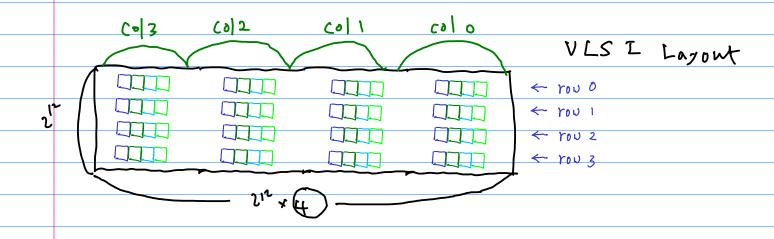

4096 × 4096 × 4-6:t

24-6it address

64Mbit (16Mx4bit) DRAMe17主 4096 columns 46:6 4 bib/column RAS Sense amp data bus 12-bit YOU YOW 4091 addy add Mux de cod into buf -4096X4-DRAM refresh Col addr deader CAS col. addr buf RAS Mux 12-bit [A23~A12] A11~A0 12-617 3 CAS 24-bit andress

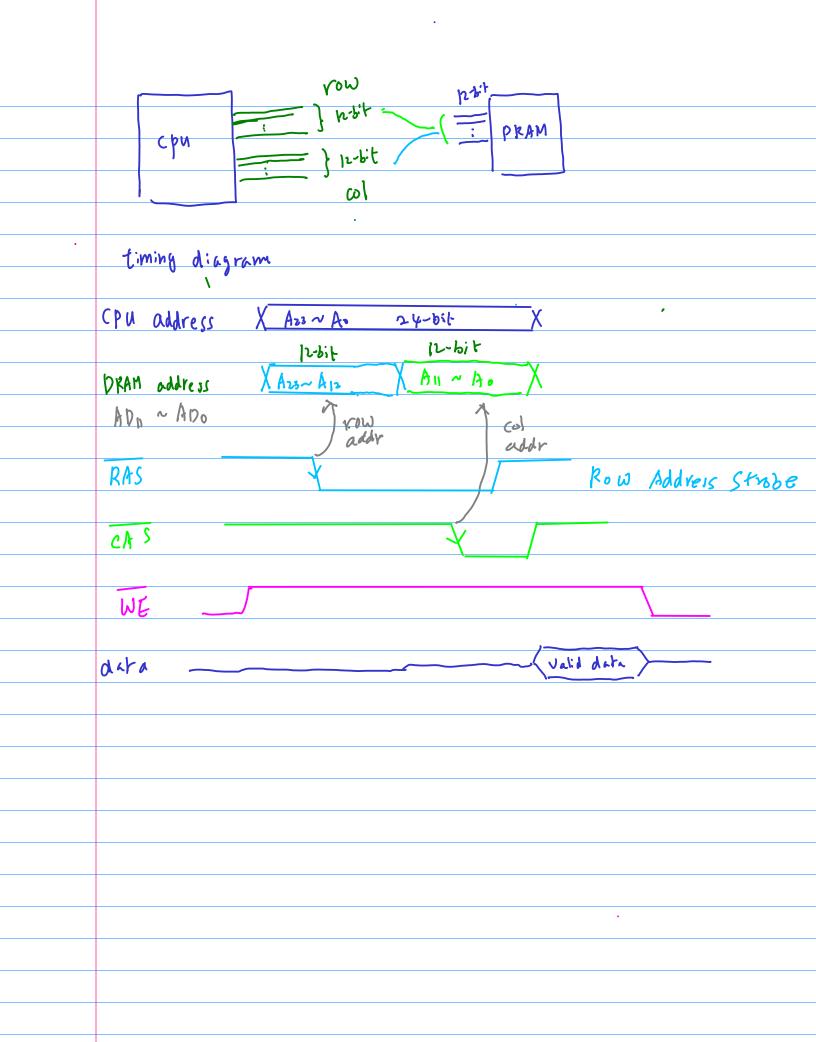

# CPU address 는 CPUI LN 足叫는 (克思) 計包 \$ 24-bit address? explayer Row Address Col address भिरुष्ट एम स्लु । धार्म DRAM chipel address } wzzur RAS (Row Address strube) / craon रिका १२ bitel खप्रवासवस् DKAM chipel address } byzeur PRAMOI Mani Address Buffer Register on Add Buffer Regon Latchiel: 322 274 Towadavess = = (0) address de coder de coder

on बाम मा गण गण भर्द स्पार्म

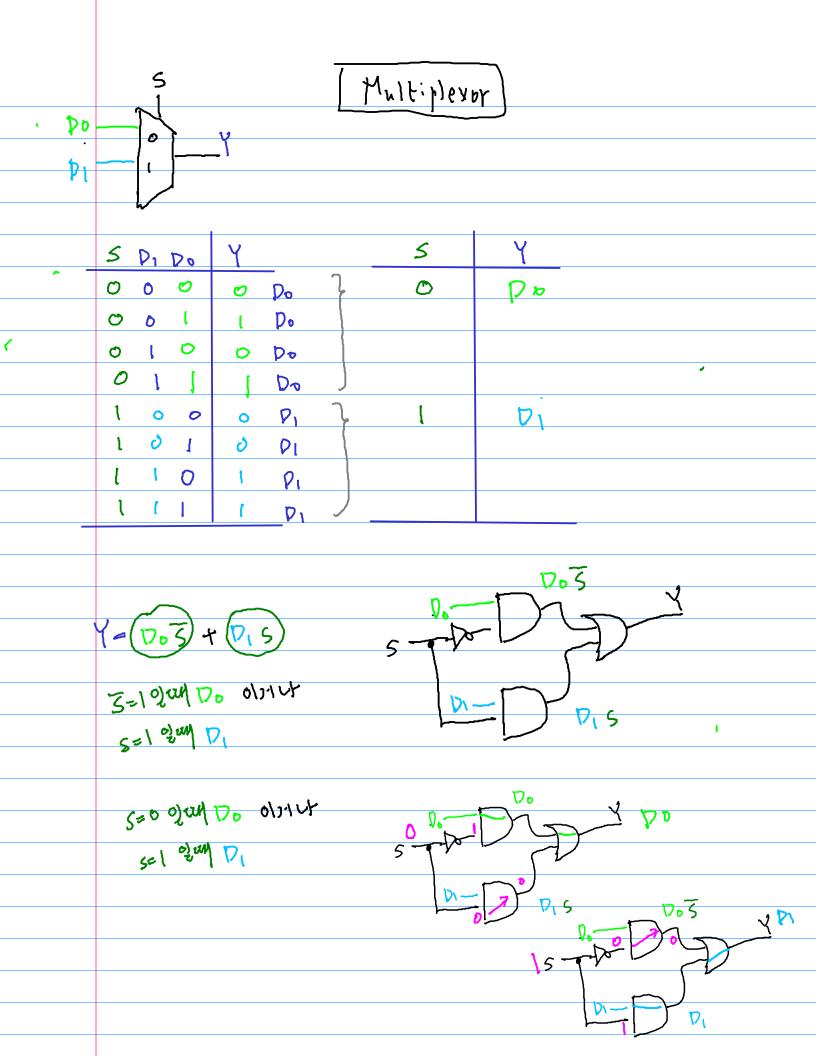

Mitzez multiplexing DRAM RBS ~ CAS 24 bit -> 12-bit Chipel pin 숙환 축임 Memory Controller

DRAM Chip

databas p3~po 4-bit addr bas A11~A0 12-bit control bas WE, OE, CAS, RAS

DRAM | \* clock X

Async DRAM W/o banks

SDRAM C Dynamic . Synchronous gold Clock Him of orth data 2 28 25 CT Rum DRANZ 取到 data et confrol signal 先の2七 六人 aues zu LRO/WR) Andra gerieur 쓰기 ~~ 건설된 data는 즉시 and 기억 간소에 지각 일시 ३५ : 인원동작은 숙양한국 국시 사내 버스고 전송 DRAMONE ON ZIED 04 20 02 01 CM -> CPUIL Wait -> Busi cti 7-621 2 448 X 一 代的 时的 SDRAM ottal quel clockon द्राधाल नेअप्राटी. O CPUTY I chac cycle 30t address et श्री त्या रहे Busz ध्याप. CPUE न्यारे ग्रामयम हार पार व्यक्त नेश्रेश्व SDRAMOI STOW SINTER THE FA  $(\gamma)$ access ४५१ मिरोप SPRAM System Bus 从客院对 割气记予 ( clock cycle 30t data & Bus 2 23 24

CPUTY BUSIN OLY ALKE THE CH.

\

#### SPRAM

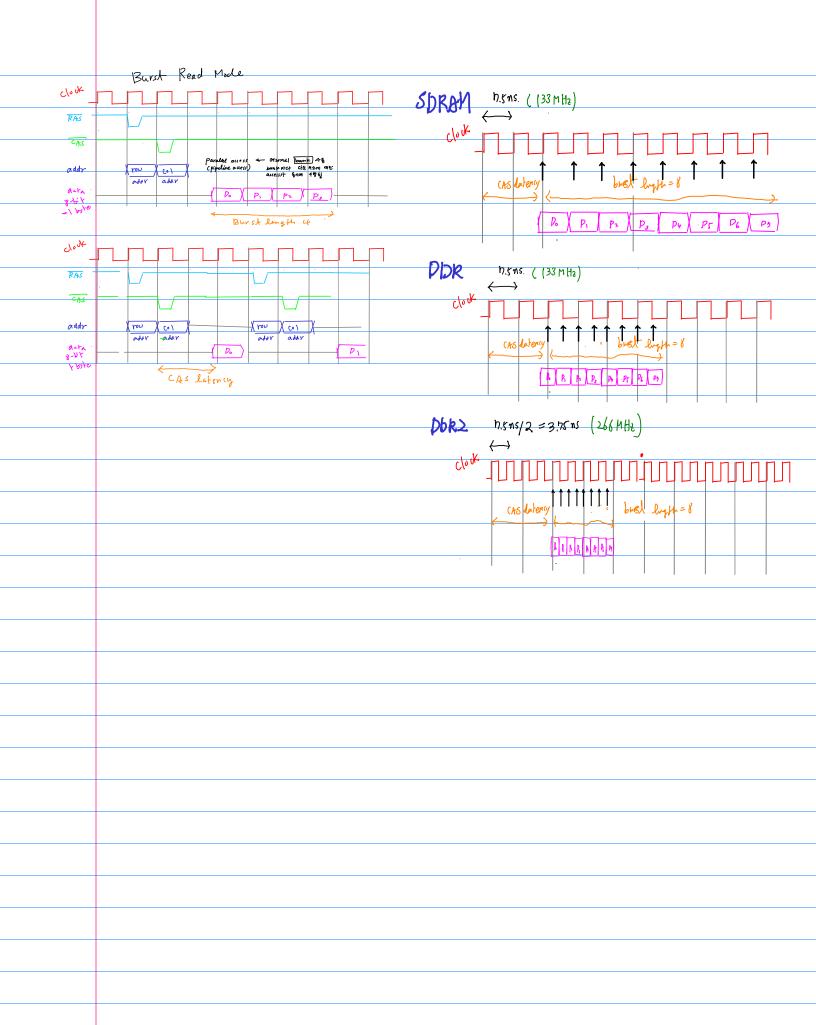

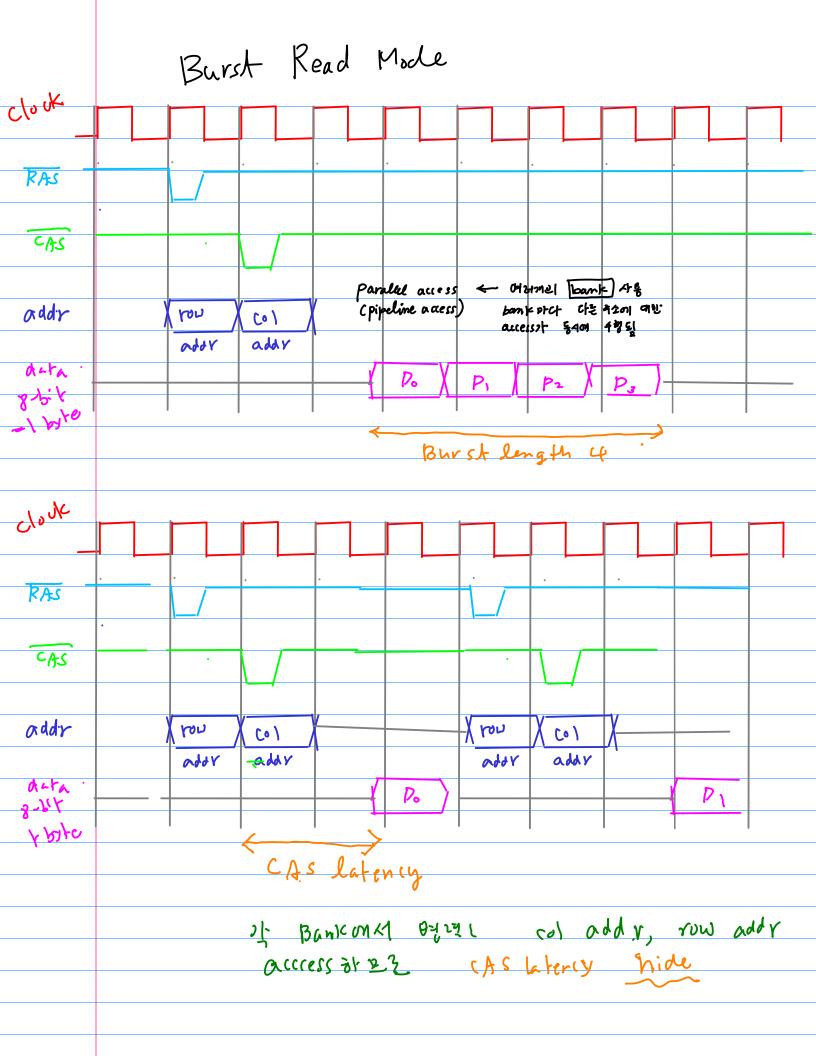

Parallel access

Othernel bank At &

Opipeline access)

bank pict ct2 4201 ct2 420

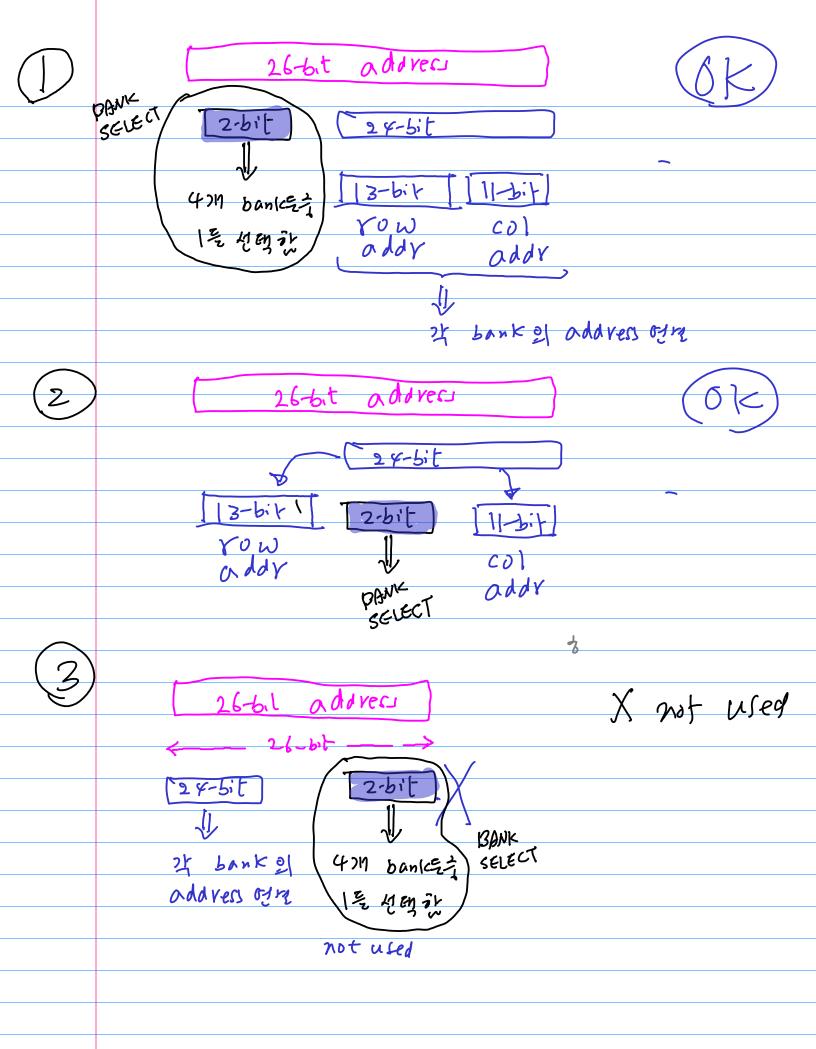

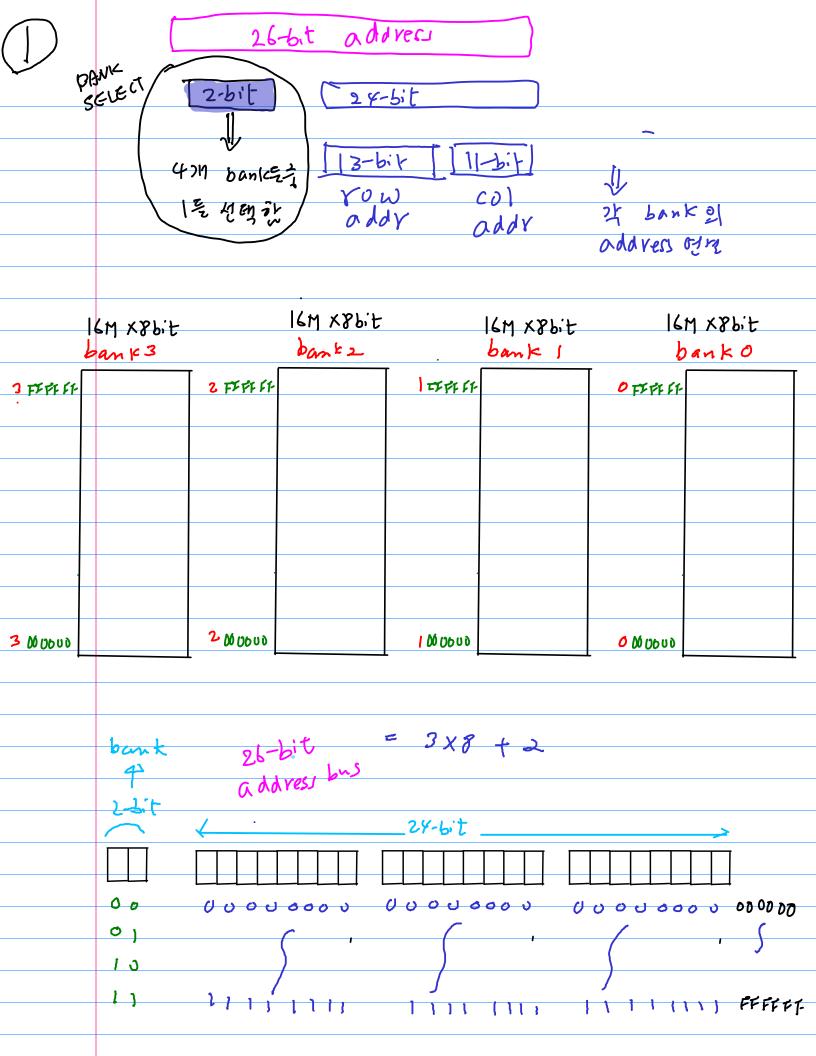

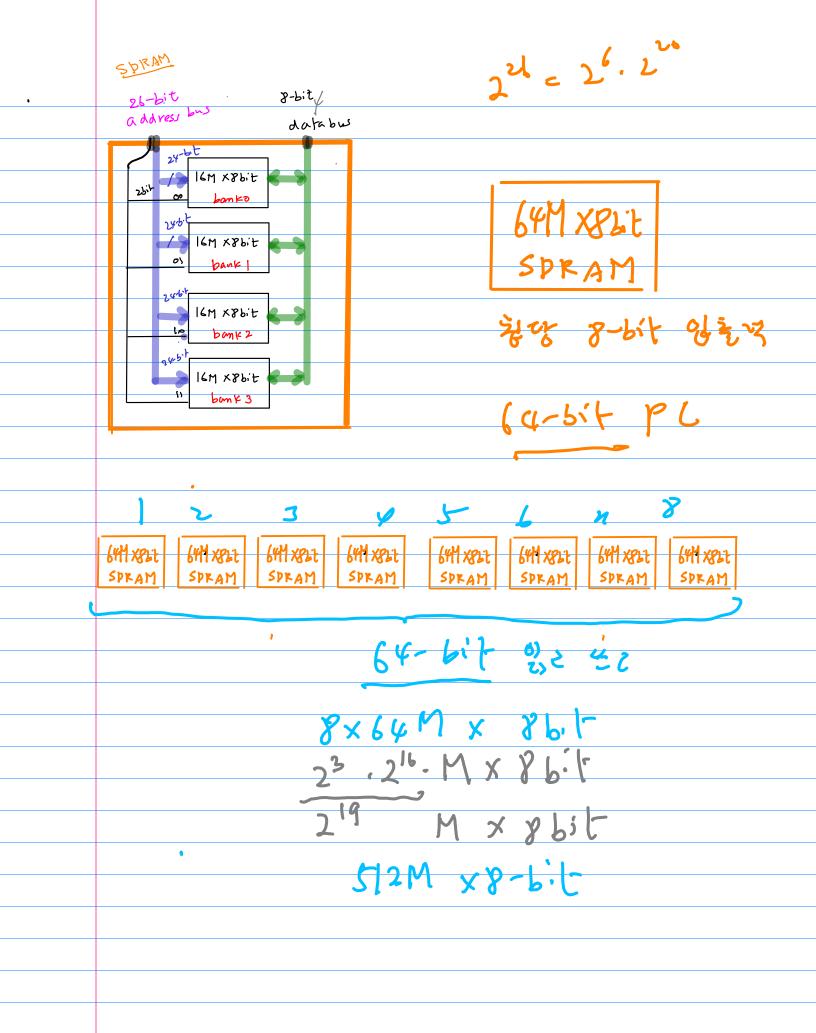

512 M 29 220 221 x 22 224 x 23 bank 512Mbit 男は SDRAM 4211 21 Bank NE [16M × 8-61t] 1 banker 3 6. IGM X 8-bit X 4 bank = 164 x 4 bank x 8-bit = 64M x 8-bit  $= 2^{4} \cdot 2^{20} \cdot 2^{2} \times 8^{-bit} = 2^{6} \cdot 2^{20} \times 8^{-bit}$ 2 X8-bit à address 21-bit

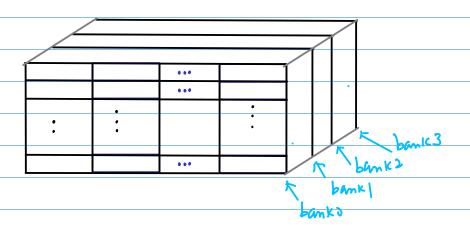

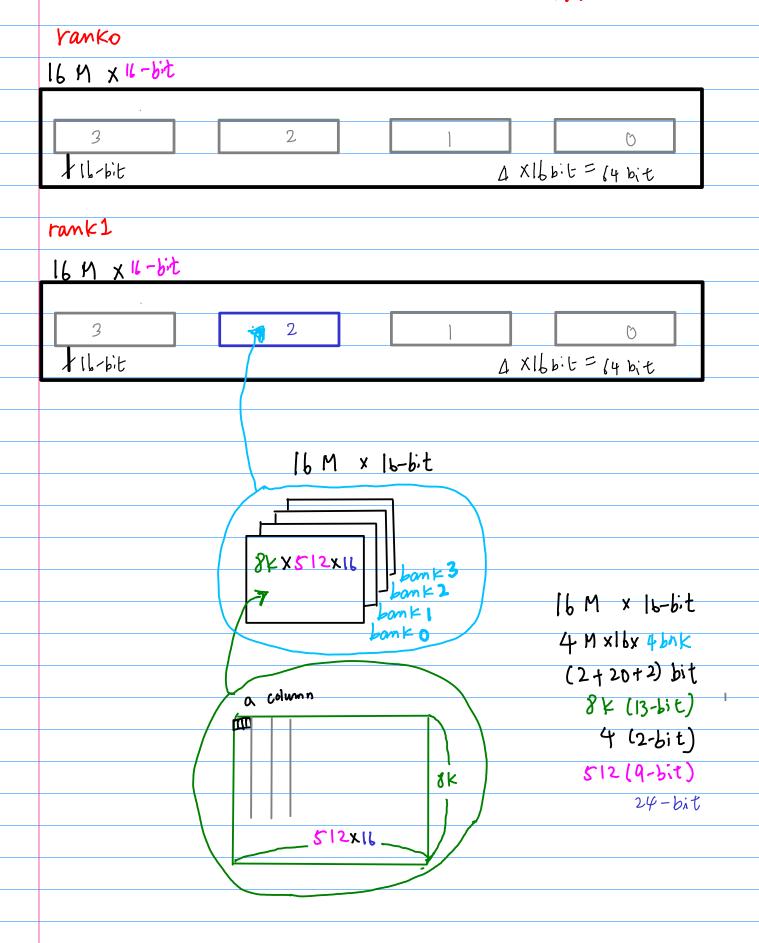

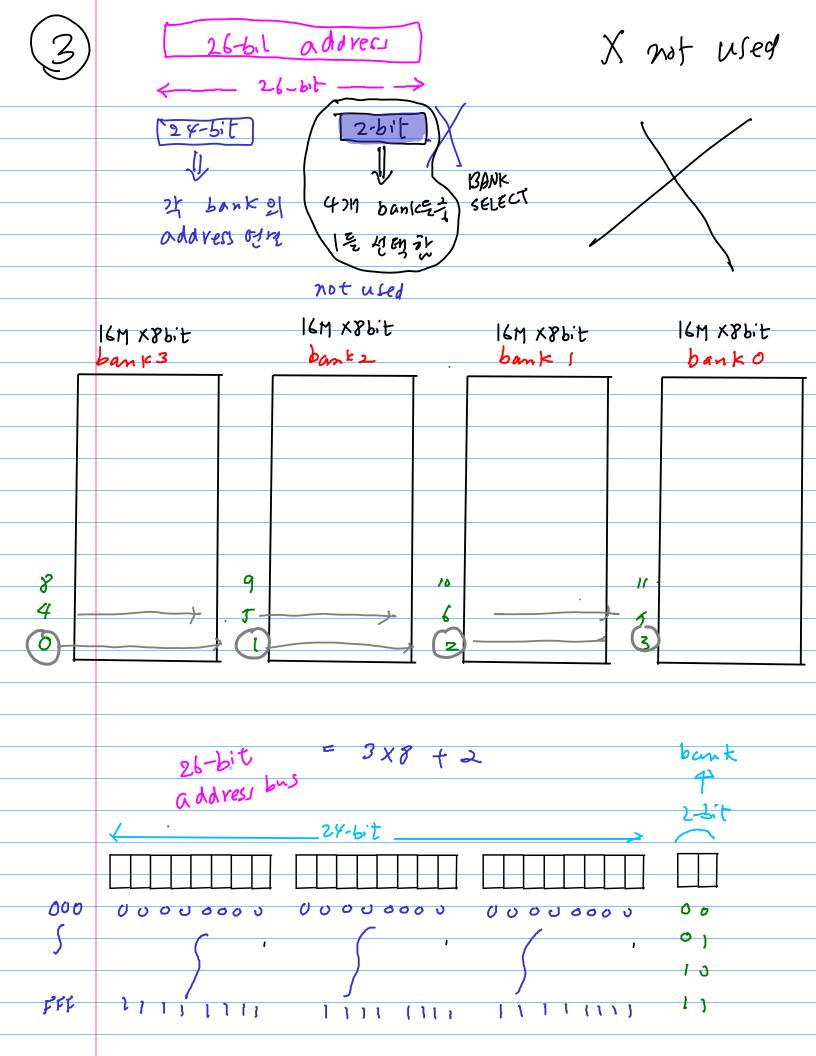

### 256 Mbit SDRAM - Banks

64 M x 4-bit

$$2^{6} \cdot 2^{20} \cdot 2^{2} = 2^{28}$$

32 M x 8-bit  $2^{5} \cdot 2^{20} \cdot 2^{3} = 2^{28}$  28 Mbit  $2^{4} \cdot 2^{1} \cdot 2^{3} = 2^{18}$  = 256 Mbit

memory

|               | 64M x4-bit      | 3211 x 8-bit | 16 M × 16-6.t |

|---------------|-----------------|--------------|---------------|

| configuration | 164 x 4 x 4 bnK | 8 Mx8x4bnK   | 4 M xlbx 4bnk |

| , 0           | (4+20+2) bit    | (3+20+2) b.t | (2+20+2) bit  |

| row addr      | 8K (13-bit)     | 8K(13-bit)   | 8 × (13-6; t) |

| bnk addr      | 4 (2-b;t)       | 4 (2-b;t)    | 4 (2-bit)     |

| col addr      | 2k (11-bit)     | K (10-b;t)   | 512(9-bit)    |

26-bit

25-5:4

24-3:5

4 banks

# 256 Mbit SDRAM - Dafa Width (4,8,16-bit)

|               | 64M x4-bit      | 32 M x 8-bit | 16 M x 16-6it |

|---------------|-----------------|--------------|---------------|

| configuration | ILM X 4 X 4 bnK | 8 Mx8x4bnK   | 4 M xlbx 4bnk |

|               | (4+20+2) bit    | (3+20+2) bit | (2+20+2) bit  |

| row addr      | 8K (13-bit)     | 8K (13-bit)  | 8 × (13-6)    |

| bnk addr      | 4 (2-b;t)       | 4 (2-bit)    | 4 (2-bit)     |

| col addr      | 2 k (11-bit)    | [ K (10-b;t) | 512 (9-bit)   |

| -             |                 | 1            |               |

26-bit 20-bit 24-bit 24

16 Pier / Col

|   |             |   | <b>\</b> |   |   |

|---|-------------|---|----------|---|---|

|   |             |   | • • •    |   |   |

|   |             |   | •••      |   |   |

|   | •           | • |          | • | • |

|   | •           | • |          | • | • |

|   | •           | • |          | • | • |

| Ī |             |   | • • •    |   |   |

| • |             |   |          |   |   |

|   | 512 columns |   |          |   |   |

- IK columns

X4 banks

### 256 Mbit SDRAM - SIMM, DIMM

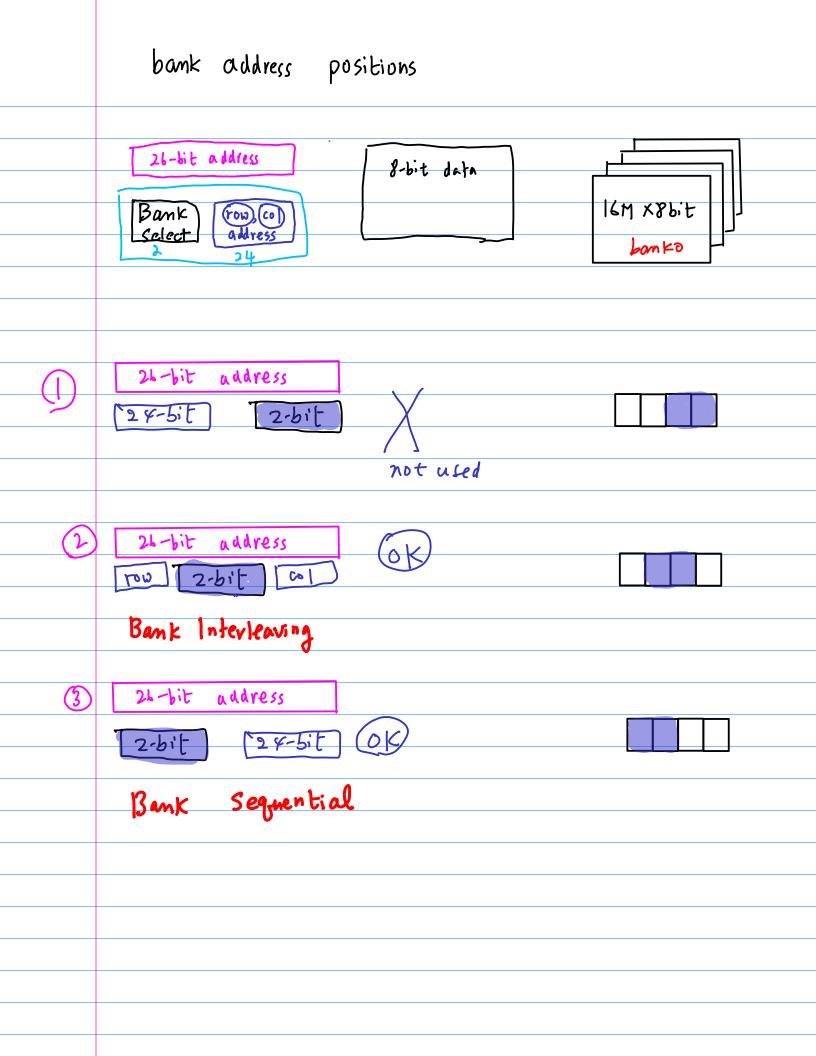

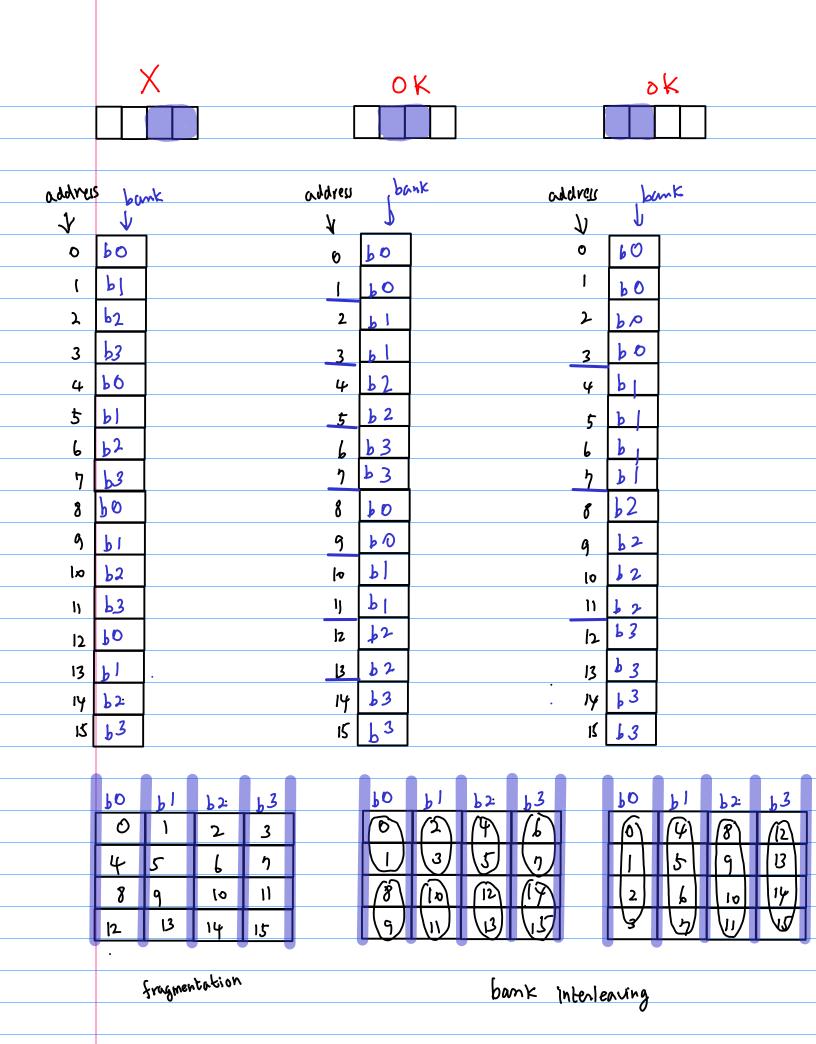

### 256 Mbit SDRAM - Bank Interleaving

|     |           | 64M x4-bit      | 3211 x8-bit  | 16 M × 16-6.t |

|-----|-----------|-----------------|--------------|---------------|

| con | fguration | 16M x 4 x 4 bnK | 8 Mx8x4bnK   | 4 M xlbx 4bnk |

|     | 0         | (4+20+2) bit    | (3+20+2) b.t | (2+20+2) bit  |

| Vo  | w addr    | 8K (13-bit)     | 8K (13-bit)  | 8 × (13-61t)  |

| bn  | k addr    | 4 (2-b;t)       | 4 (2-b;t)    | 4 (2-bit)     |

| Co  | d addr    | 2k (11-bit)     | K (10-b;t)   | 512 (9-bit)   |

| •   |           | 26-bit          | 25-6;6       | 24-bit        |

10987654321098765432109876543210 bak Column (11-bit) rnk row (13-bit) 21-bit 10987654321098765432109876543210 bak Column (10-bit) rnk row (13-bit) 25-516 0 10987654321098765432109876543210 bnk Column (9-bit) rnk row (13-bit) 24-5; t

> 64-bit = 8 bytes 3-bit address

### 256 Mbit SDRAM - Rank

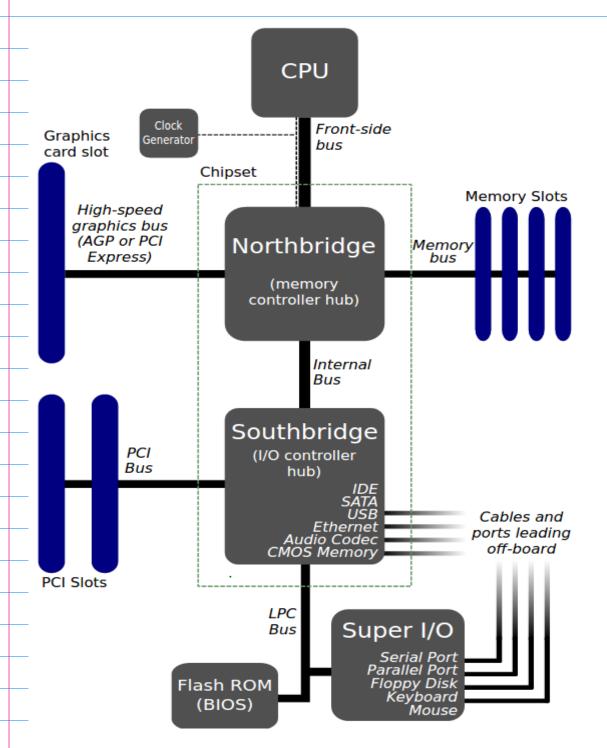

# Intel Memory Controller

https://upload.wikimedia.org/wikipedia/commons/b/bd/Motherboard\_diagram.svg

SPRAM

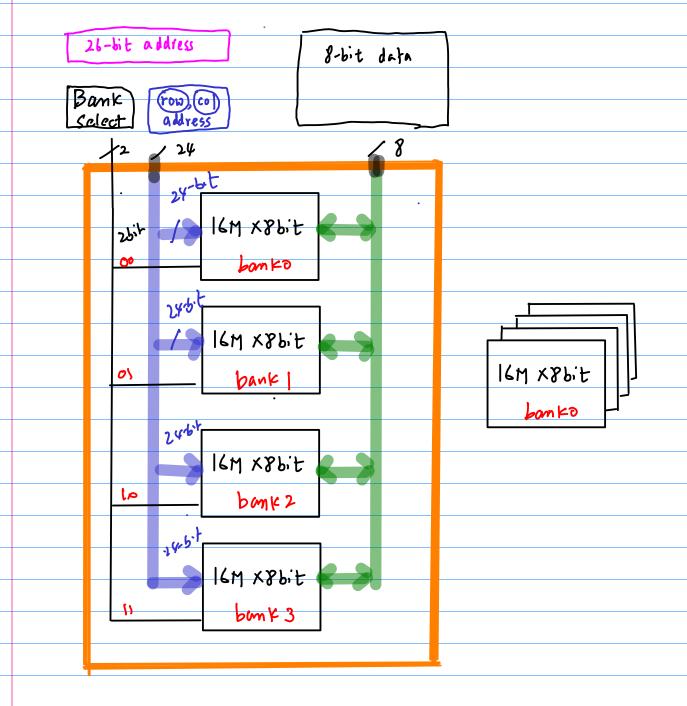

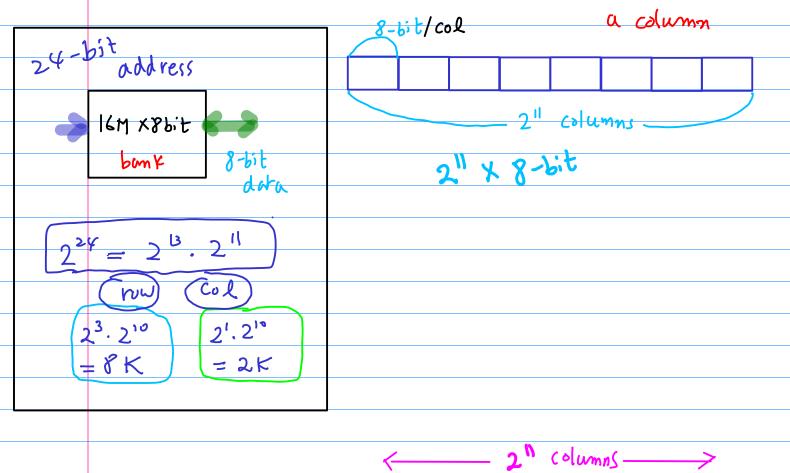

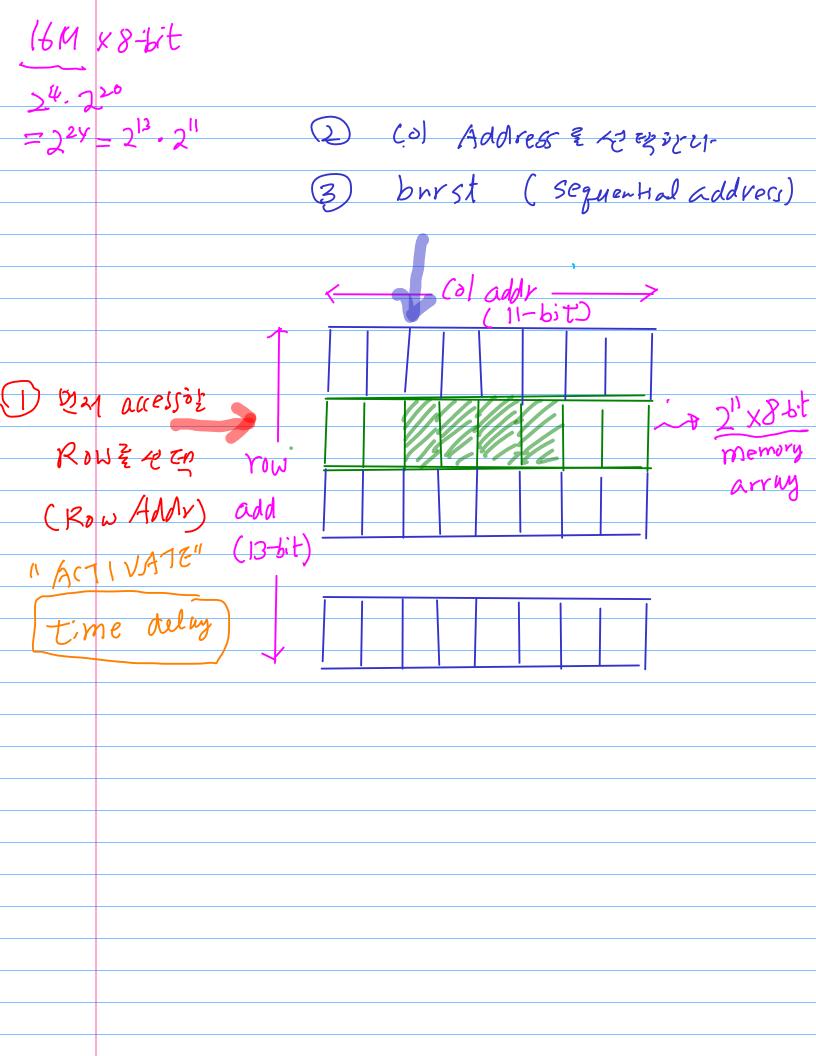

24bit address = 3/10/1 4/10/1

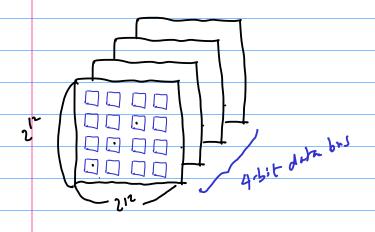

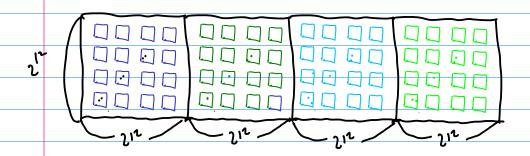

oten 1272 bankを data bus元 みまたっ

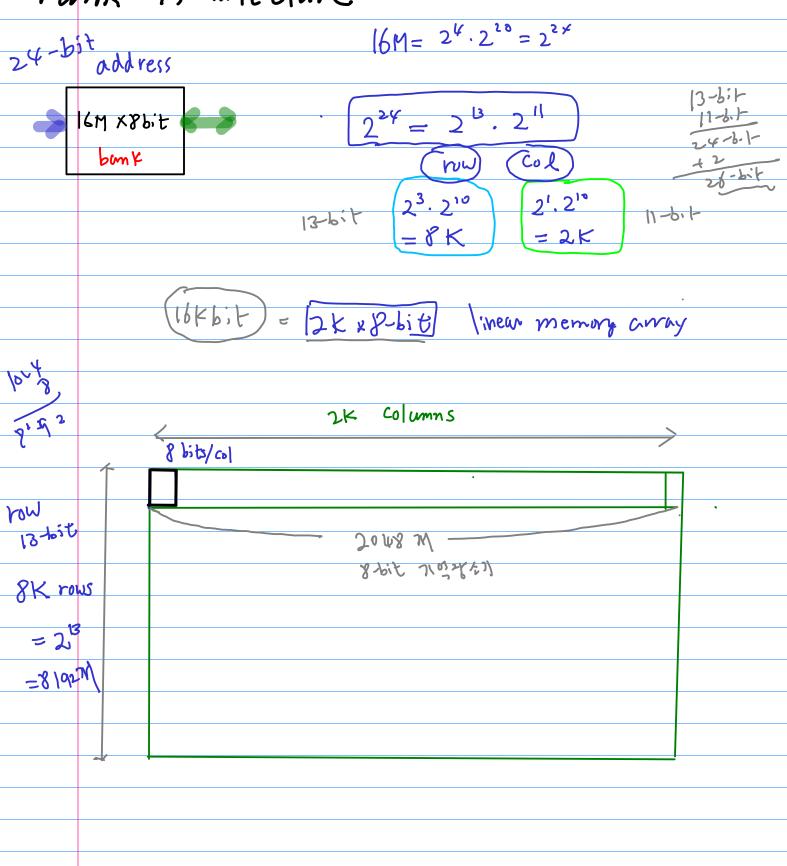

### Bank Architecture

SPRAM (Row) & (col) Address Decoder 41-3 PRAM21-21:01 ROW & Col address x+20 0000000 0000000 0000000 -> []-bit data access 11% 0000000 0000000 8-bit data accesse Slamare 8 m 0000000 0000000 9999999 Co payof Fig.

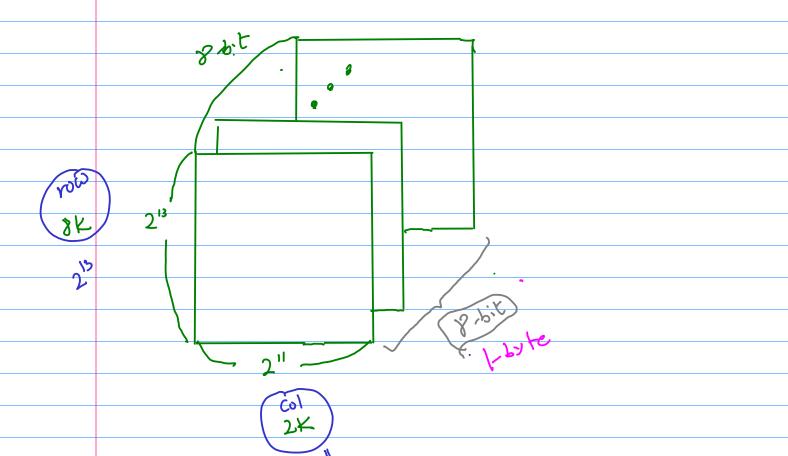

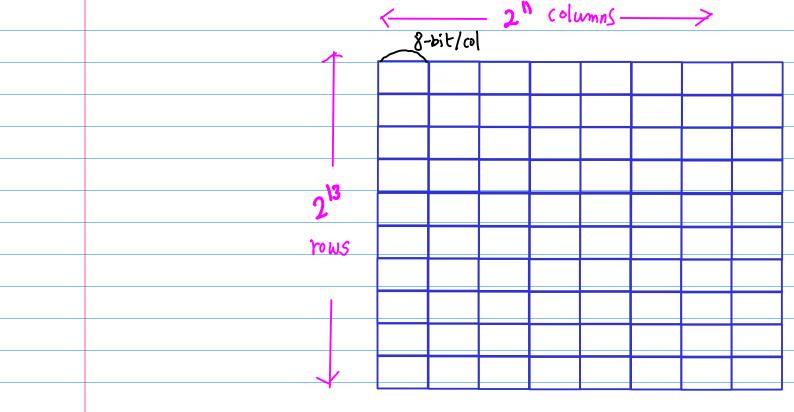

$$2^{24} = 2^{13} \cdot 2^{11}$$

$$(nw) \quad (col)$$

$$2^{3} \cdot 2^{10} \quad 2^{1} \cdot 2^{10}$$

$$= 8 \, \text{K} \qquad = 2 \, \text{K}$$

- · 3 8 K M of rowst of ct.

- · 子 rowのに 16 Kbit가 기なをい.

74/2/2/1/ 22/

| ( Activa  | te.   | γοω |  |  |

|-----------|-------|-----|--|--|

|           |       |     |  |  |

| (2) RD/   | WR    | col |  |  |

|           |       |     |  |  |

| (3) Prech | narge |     |  |  |

|           |       |     |  |  |

|           |       |     |  |  |

|           |       |     |  |  |

|           |       |     |  |  |

|           |       |     |  |  |

|           |       |     |  |  |

|           |       |     |  |  |

|           |       | •   |  |  |

|           |       |     |  |  |

|           |       |     |  |  |

|           |       |     |  |  |

|           |       |     |  |  |

|           |       |     |  |  |

|           |       |     |  |  |

|           |       |     |  |  |

|           |       |     |  |  |

|           |       |     |  |  |

|           |       |     |  |  |

|           |       |     |  |  |

|           |       |     |  |  |

|           |       |     |  |  |

|           |       |     |  |  |

|           |       |     |  |  |

|           |       |     |  |  |

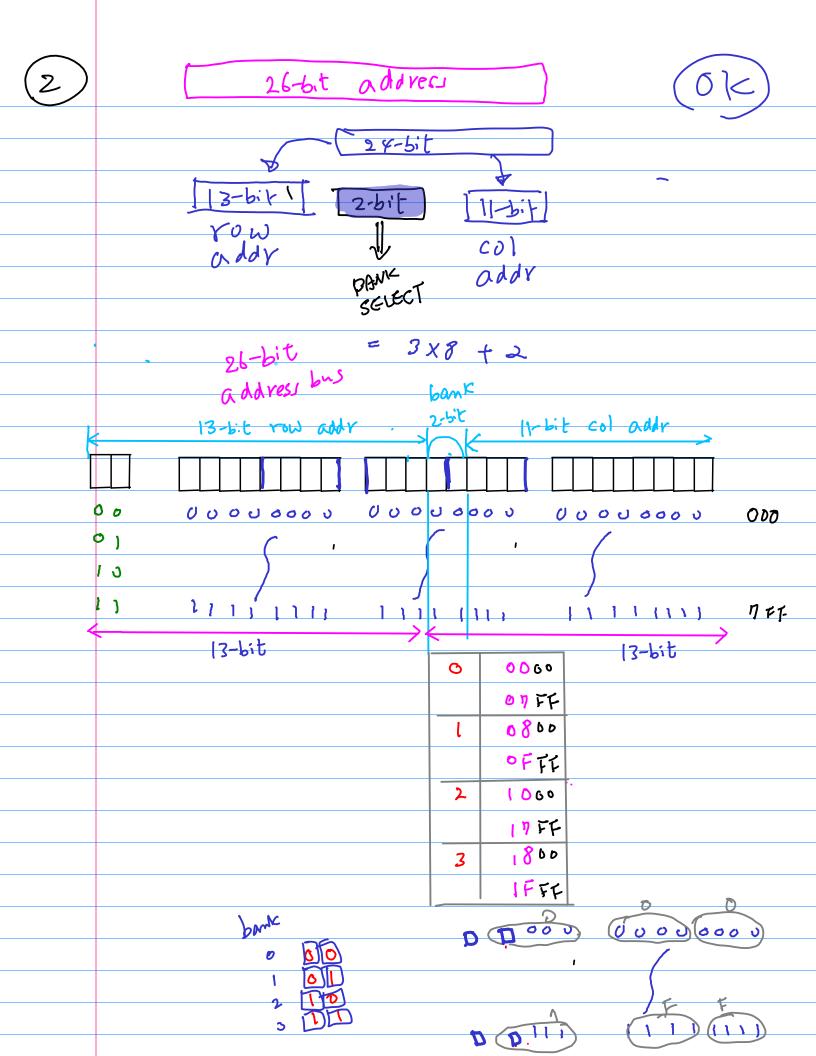

## **Bank Interleaving**

allows operations to 2 ~ 4 banks simultaneously

inside of a DRAM chip

| 3 FF FF (1-         |          |        |              |       |          |                                         |

|---------------------|----------|--------|--------------|-------|----------|-----------------------------------------|

|                     |          |        |              |       |          |                                         |

|                     | bank3    |        |              |       |          |                                         |

|                     |          |        |              |       |          |                                         |

| 3 000000            |          |        |              |       |          |                                         |

| 2 FF FF 61-         |          |        |              |       |          |                                         |

|                     |          |        |              |       |          |                                         |

|                     | bank2    |        |              |       |          |                                         |

|                     |          | -      |              |       |          |                                         |

| . 200000            |          |        |              |       |          |                                         |

| \FF FF 61-          |          |        |              |       |          |                                         |

|                     |          |        |              |       |          |                                         |

|                     | banx 1   |        |              | 1212  | 221      |                                         |

| •                   |          |        |              | 70.0  |          | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |

| 100000              |          |        |              |       |          | X3                                      |

| ० हर हो ।-          |          |        |              |       | · /      |                                         |

|                     | 1 100    |        |              | 8-6:  | t        |                                         |

|                     | banko    |        | <u> </u>     |       |          |                                         |

|                     |          |        |              |       |          |                                         |

| <b>0</b> 00 00 00 0 |          |        |              | 75    | 00       | J                                       |

|                     |          |        |              |       |          |                                         |

| 26-6:               | t        |        | .1           |       | ) 10 lit |                                         |

|                     | - (      |        | J            | (     | 2 K-5: t |                                         |

|                     | 2¥       |        | 2            | ΙĽ    | Ī L      | FF                                      |

| heic                | YOW + CO | 1      | 3            | () () | •        | •                                       |

| OMMIC               | (13)     | T C II | b mic        |       | 00       | 0 0                                     |

|                     | (13)     |        | <i>P</i> 11" |       |          |                                         |

|                     |          |        |              |       |          |                                         |

21-bit address

221 = 26 · 220 = 4 M

72 bank Mel 四点 전含复杂 没足 row on 外边 Burst Mode: 한번 읽을 때 어내게의 13개도 등을 연 옥선 의 건 3 같 등 의 다 120, P1, 122, P3 burst length = 4 of Bankonky Byryl col addy, row addy accress of 22 cAs laterly hide Bankl Bank3

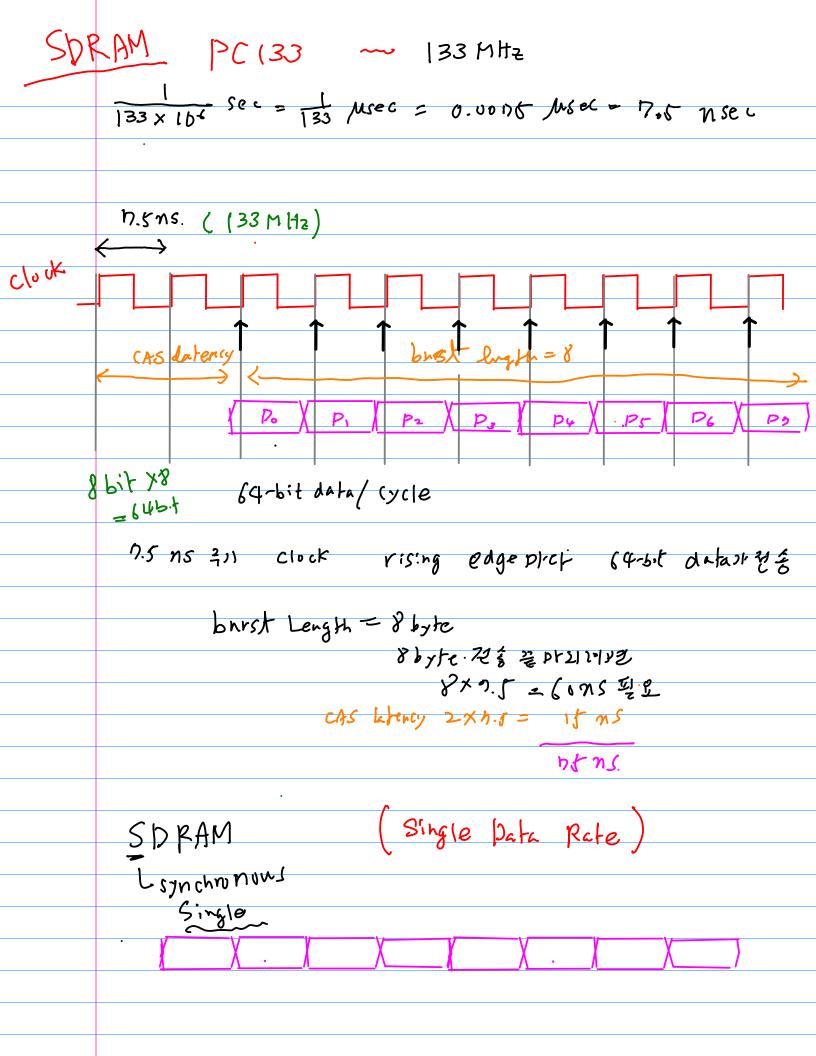

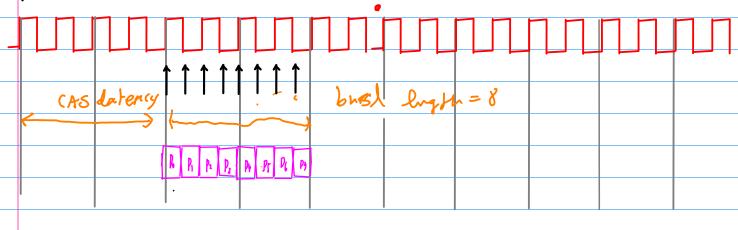

## DDR ( Double Data Rate ) PDR-266 Clock 133MHz x2 n.5ns. ( (33 m Hz) Clock frising edge falling edge CAS latency 2 4 h.5 arta transf 60/2 = 307 PDR-266 2711 Clock = 13311 Hz PDR-333 2711 Clock & 166 MHz PDR-400 2211 Clock 2 200 MHz

17Db 5

2 D11 出色 是对 freg 是 外包补气

DAR SDRAM.

7.5ns/2 = 3.75ns (266MHz)

CAS laterly 4 x 3.75 = 15

CAS laterity

$$(4 \times 3.75 = 15)$$

data transfer  $30/2 = 15$

$30 \times 7$

gougle

Computer Organization in plain vee

wikiversity. Mg

The necessities in Computer Organization wikiversity.org

644 XPLT SPRAM SPRAM SPRAM SPRAM SPRAM SPRAM 1111 SIMM (Single In-Line Memory Module) क्रिक DIMM ( Dual In-line Memory Module) 0 / 103/ SDRAM: 29bit = 256 M x 8 bit  $2 \cdot 2^{30} = 2^{8} \cdot 2^{10} \cdot 2^{3}$ SIMM = 8 x SDKAM = 8 x 256M x8 Lit = 8 × (2 G Bit) = 16 G(BIF) = 2 G (Byte)

| memory | rank |

|--------|------|

|        |      |

| Olympia 2 and Marine Coult Action 2015        |

|-----------------------------------------------|

| Oftraoz CPU - Memory 64-bit data 223          |

| C1101 61 0/2 1/2 Widthor 64-bit 61-8131- 515} |

| 745 modules memory rank                       |

|                                               |

| TEDEC 2001 GINES Q产型 等0) 610-bitz             |

| 어내게이 M로고칼을 사용하여                               |

| 78t 792/21 module                             |

|                                               |

| 각 rankonx address brct                        |

| 64-bit = read/write it 4                      |

| SDRAM. ([] X Ubil-) 1674                      |

| = D X 64 pil-                                 |

|                                               |

| SPRAM. ( X 8 bil-) 8 M                        |

|                                               |

| = DX64Pit                                     |

|                                               |

|                                               |

\_\_\_\_\_

| •                              |

|--------------------------------|

| Single rank module - (64-bit)  |

|                                |

| 7an/cz/ 36-219                 |

| duch rank module - (4-bit) X2. |

| rankor 504                     |

| ·                              |

|                                |

|                                |

|                                |

|                                |

|                                |

|                                |

|                                |

|                                |

|                                |

|                                |

|                                |

|                                |

|                                |

|                                |

|                                |

|                                |

|                                |

|                                |

|                                |

|                                |

|                                |

|                                |

|                                |