Copyright (c) 2014 Young W. Lim.

Permission is granted to copy, distribute and/or modify this document under the terms of the GNU Free Documentation License, Version 1.2 or any later version published by the Free Software Foundation; with no Invariant Sections, no Front-Cover Texts, and no Back-Cover Texts. A copy of the license is included in the section entitled "GNU Free Documentation License".

Please send corrections (or suggestions) to youngwlim@hotmail.com.

This document was produced by using OpenOffice and Octave.

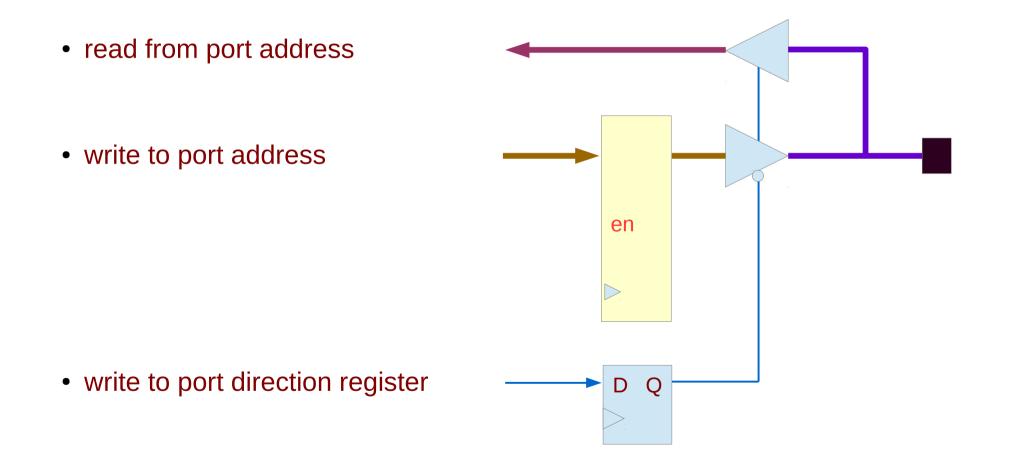

## **IO Registers**

FSM Example (2A)

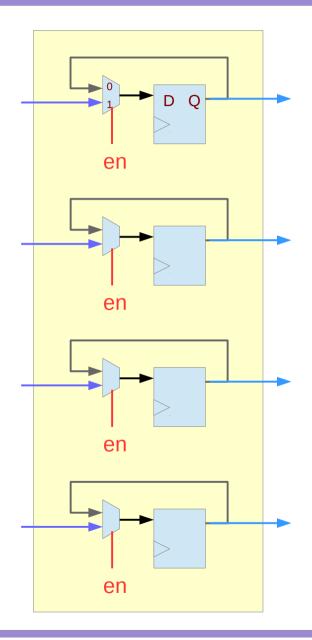

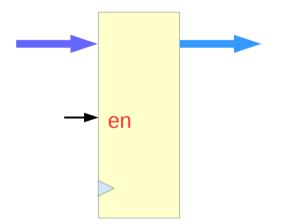

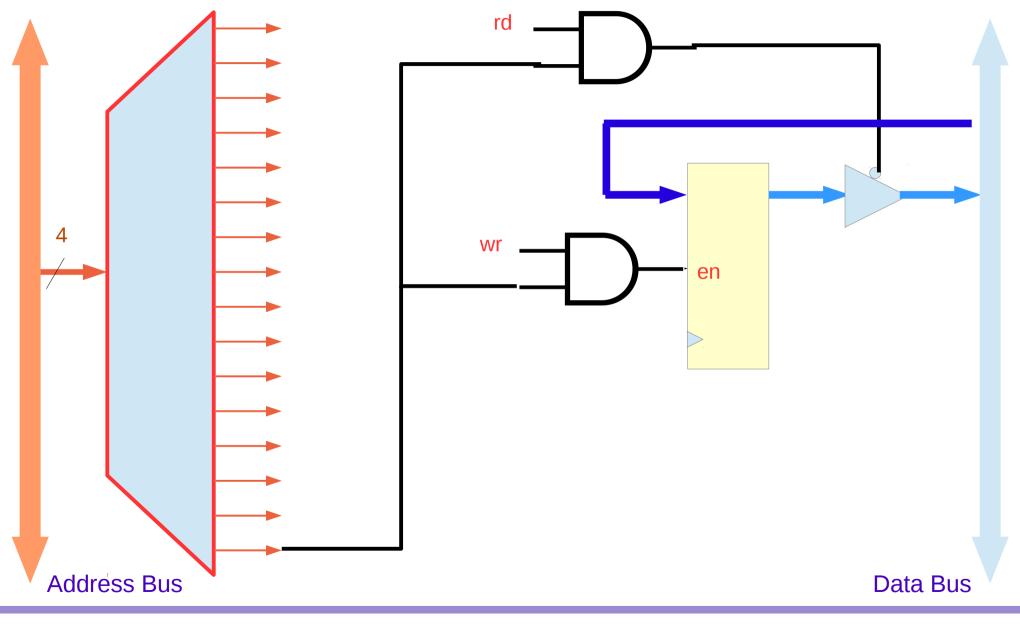

## Address Decoding & IO Register

4

FSM Example (2A)

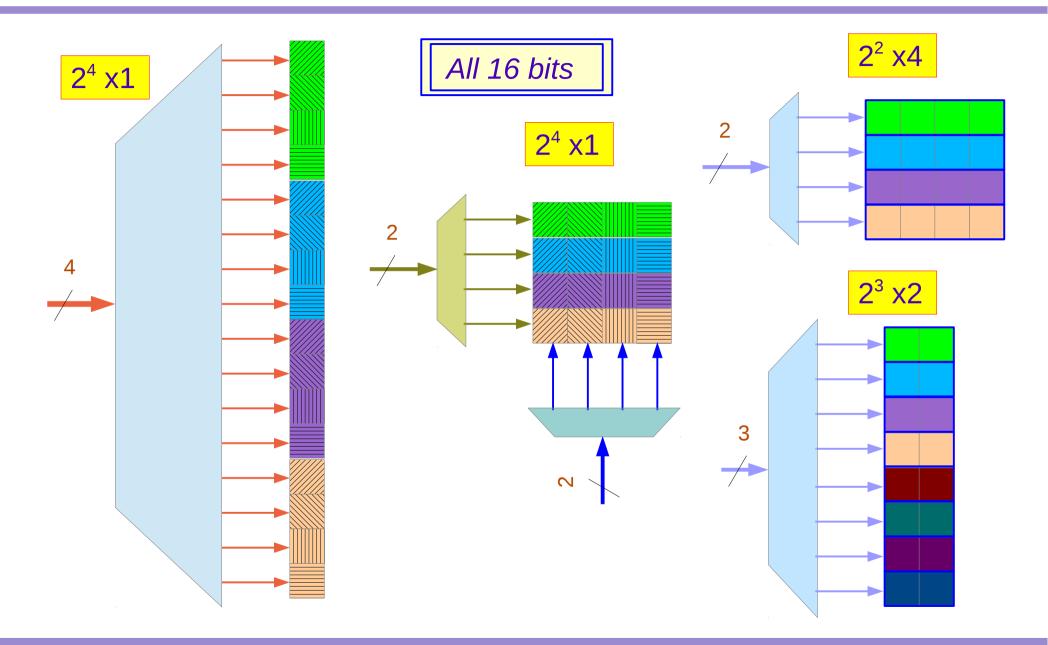

## Address Decoding & DRAM

FSM Example (2A)

## References

- [1] http://en.wikipedia.org/

- [2] D.M. Harris, S. L. Harris, "Digital Design and Computer Architecture"