Copyright (c) 2011-2013 Young W. Lim.

Permission is granted to copy, distribute and/or modify this document under the terms of the GNU Free Documentation License, Version 1.2 or any later version published by the Free Software Foundation; with no Invariant Sections, no Front-Cover Texts, and no Back-Cover Texts. A copy of the license is included in the section entitled "GNU Free Documentation License".

Please send corrections (or suggestions) to youngwlim@hotmail.com.

This document was produced by using OpenOffice and Octave.

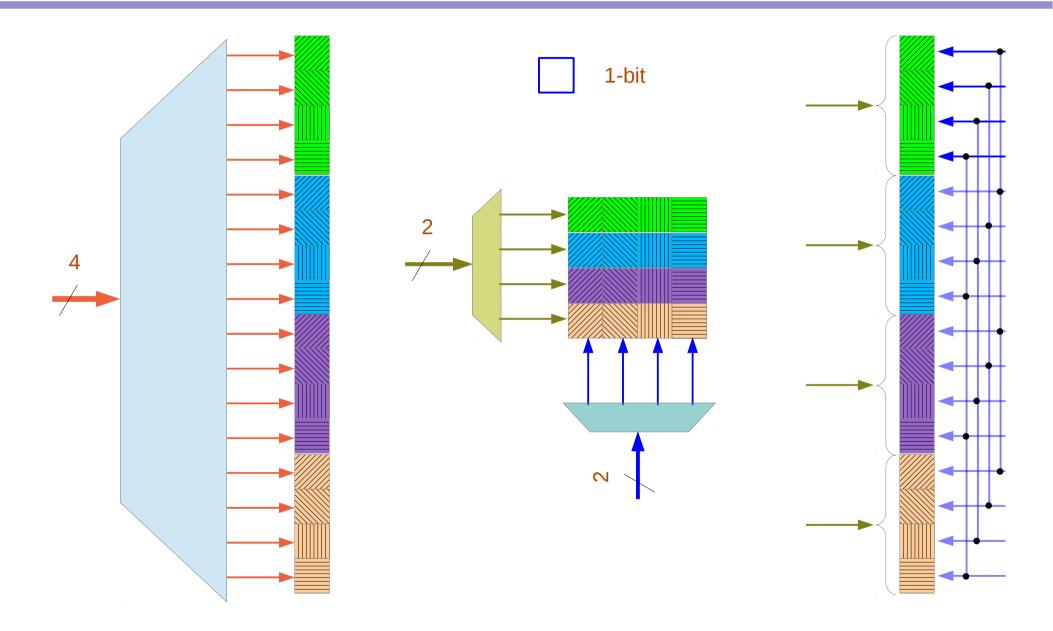

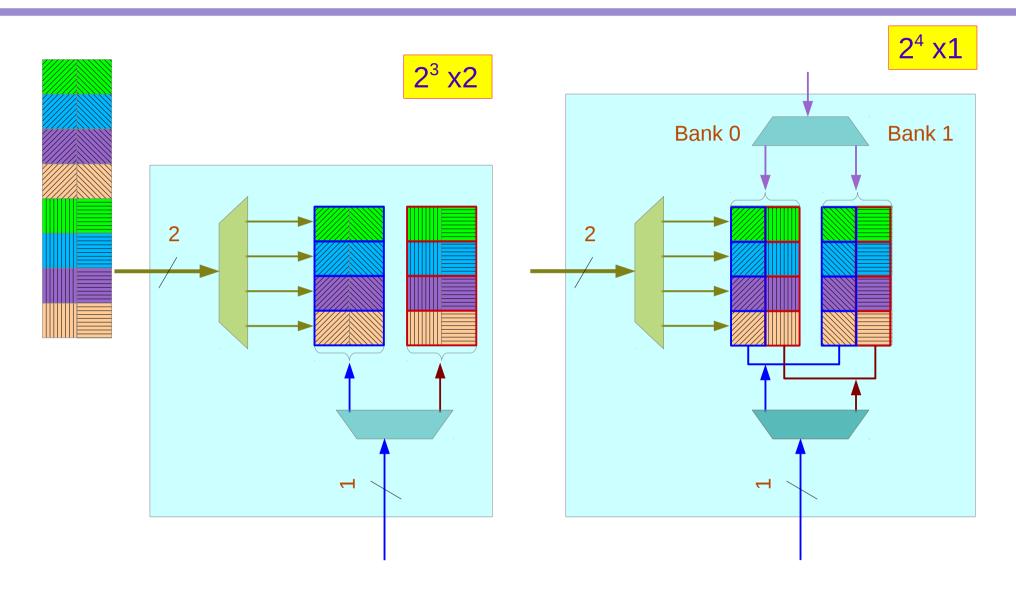

## DRAM – Coincidence Selection (1)

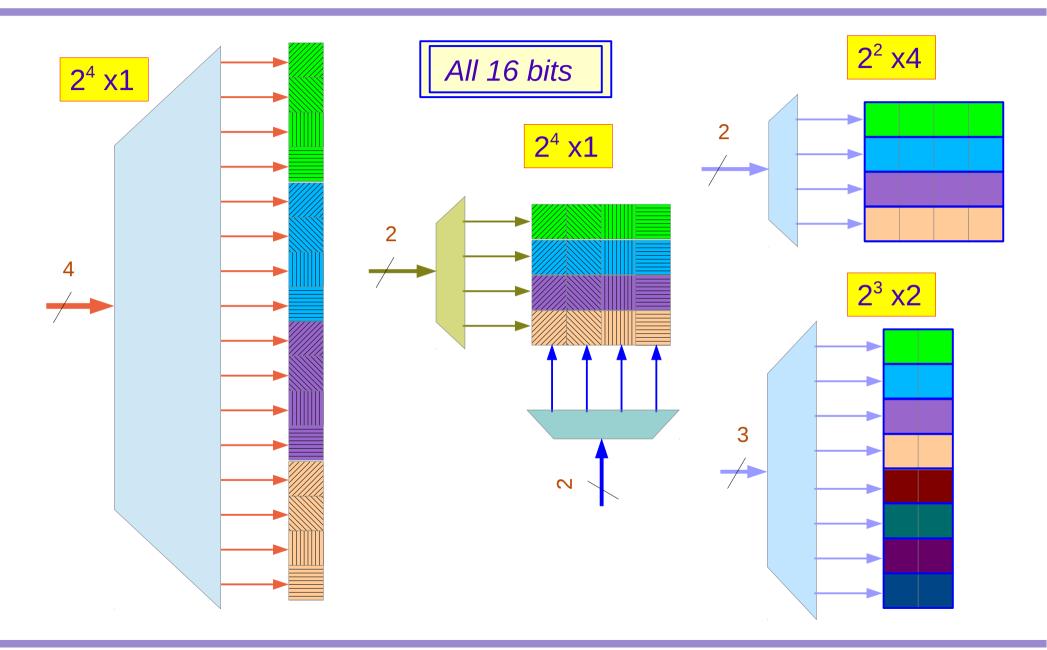

## DRAM – Coincidence Selection (2)

#### DRAM (2A)

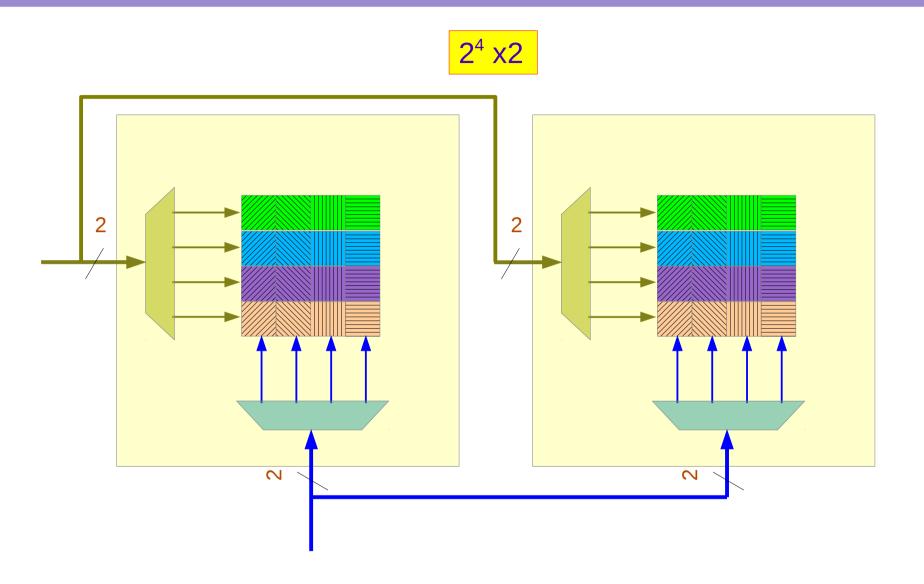

#### DRAM – Coincidence Selection (3)

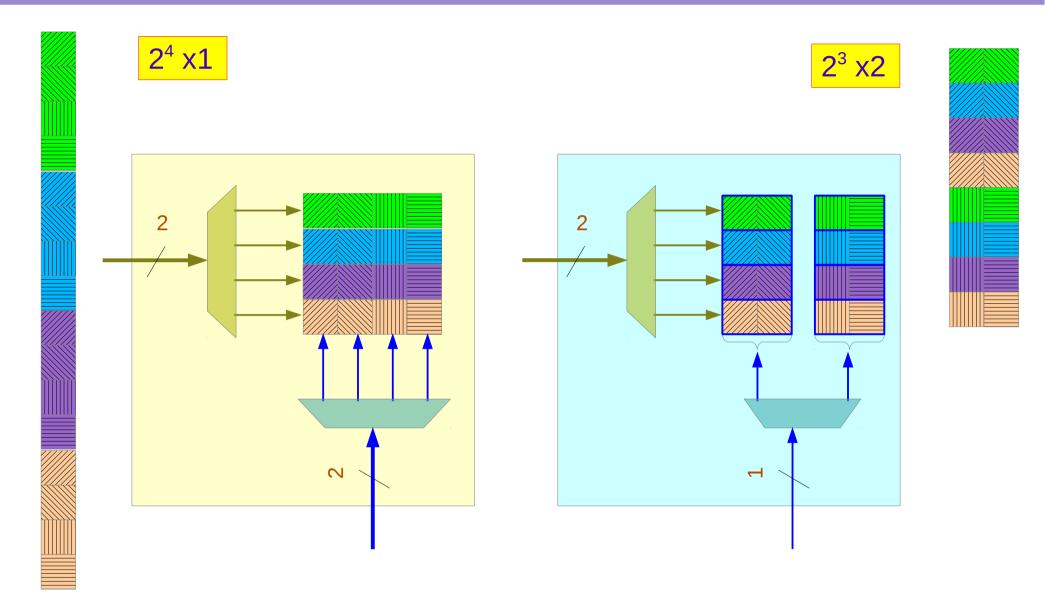

#### DRAM – Coincidence Selection (4)

## DRAM – Coincidence Selection (5)

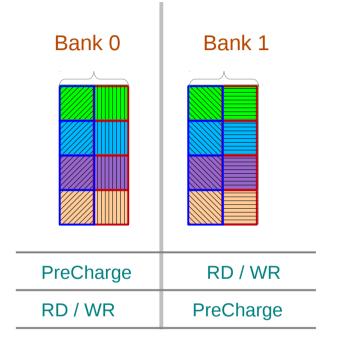

## DRAM – PreCharge

DDR RAM executes commands given by the chipset. (Activate, Read, Write, Precharge, etc)

To activate a bank with a row for reading or writing, the bank is to be charged.

This amplifies the signal from that row for a read

A memory bank is usually **precharged** without waiting for a read/write request and then charging.

**Precharging** one memory bank can usually be overlapped with **accessing** another memory bank.

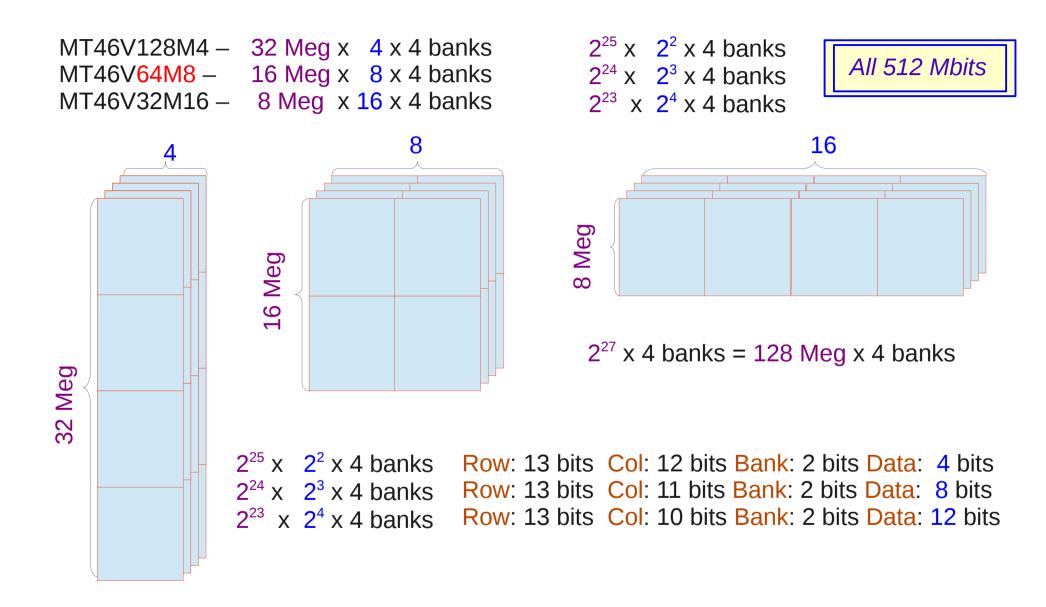

### DRAM – 512Mb Example

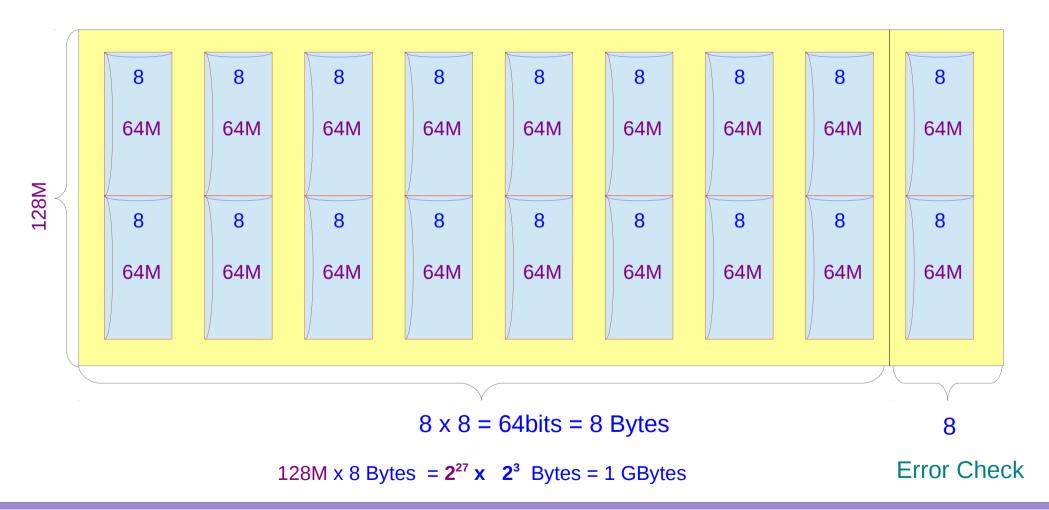

# DIMM Example (1)

DRAM (2A)

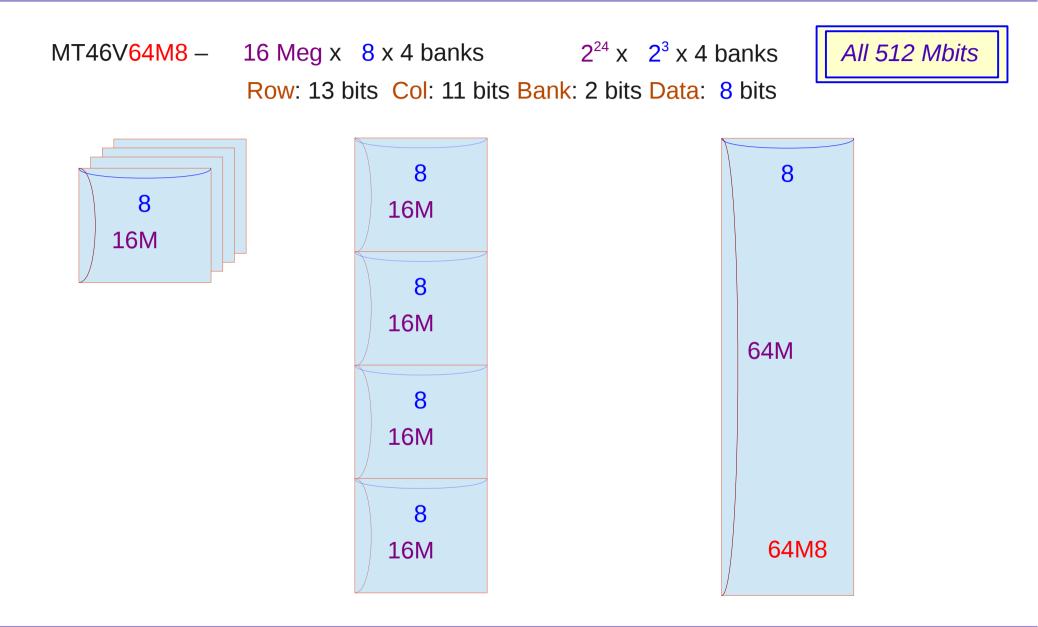

# DIMM Example (2)

MT46V64M8 – 16 Meg x 8 x 4 banks 2<sup>24</sup> x 2<sup>3</sup> x 4 banks Row: 13 bits Col: 11 bits Bank: 2 bits Data: 8 bits

#### References

- [1] http://en.wikipedia.org/

- [2] M. M. Mano, C. R. Kime, "Logic and Computer Design Fundamentals", 4<sup>th</sup> ed.

- [3] http://www.ccs.neu.edu/course/com3200/parent/NOTES/DDR.html "DDR RAM by Gene Cooperman"